(S+) УСТРОЙСТВО ДЛЯ СЛОЖЕНИЯ И ВЫЧИТАНИЯ

| название | год | авторы | номер документа |

|---|---|---|---|

| Многоразрядное устройство для сложения и вычитания | 1981 |

|

SU993264A1 |

| Устройство для суммирования фибоначчиево-десятичных кодов | 1981 |

|

SU945862A1 |

| Суммирующее устройство с плавающей запятой | 1982 |

|

SU1056182A1 |

| Двухразрядный сумматор в коде "М из N | 1981 |

|

SU980092A1 |

| Арифметико-логическое устройство двухадресной ЦВМ | 1980 |

|

SU890390A1 |

| Устройство для алгебраического сложения чисел | 1983 |

|

SU1136148A1 |

| УСТРОЙСТВО для СУММИРОВАНИЯ | 1973 |

|

SU393740A1 |

| Устройство для сложения и вычитания | 1978 |

|

SU842798A1 |

| Многовходовой знакоразрядный сумматор | 1982 |

|

SU1027716A1 |

| Последовательный двоично-десятичный сумматор-вычитатель | 1977 |

|

SU693369A1 |

I

Изобретение относится к вычислительной технике и может быть использовано в арифметических устройствах электронных вычислительных машин и в цифровых следящих системах управления.

Известны последовательные устройства дли сложения и вычитания, содержащие полусумматор - вычитатель, линии задержки, элемент И, элемент ИЛИ, блоки задержки на разряд, блок коррекции результата, накопитель, причем вь1ход накопителя соединен с входом блока задержки на разряд и с первым входом блока анализа на нуль первого слагаемого, второй вход которого соединен свходом устройства, а выход - с первым входом элемента И, второй вход которого подключен к генератору одиночного импульса, третий вход элемента И подключен к дополнительному выходу блока коррекции результата, а выход элемента И - к второму входу

элемента ИЛИ, причем выход второго блока задержки на разряд соединен с входом полусуммат:ора - вычитателя С1 . Эти.устройства характеризуются недостаточным быстродействием.

Известны также устройства для сложения и вычитания в избыточной двоичной системе счисления, содержащие в каждом разряде блок форми- . рования отрицательной суммы, блок

10 формирования положительного переноса и триггер хранения результата, причем в каждом разряде установлен блок формирования положительной суммы и блок формирования отрицательisного переноса, входы которых попарно объединены и подключены соответственно к выходам формирования отрицательной суммы, к шинам прямого и инверсного отрицательного

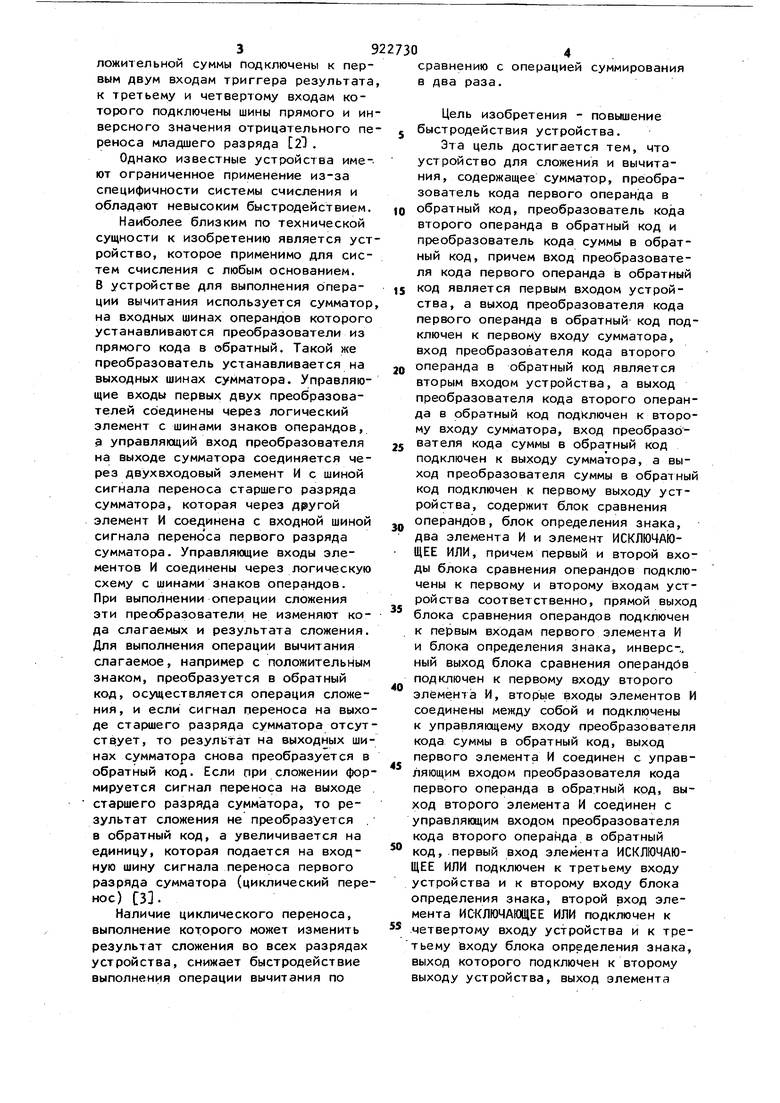

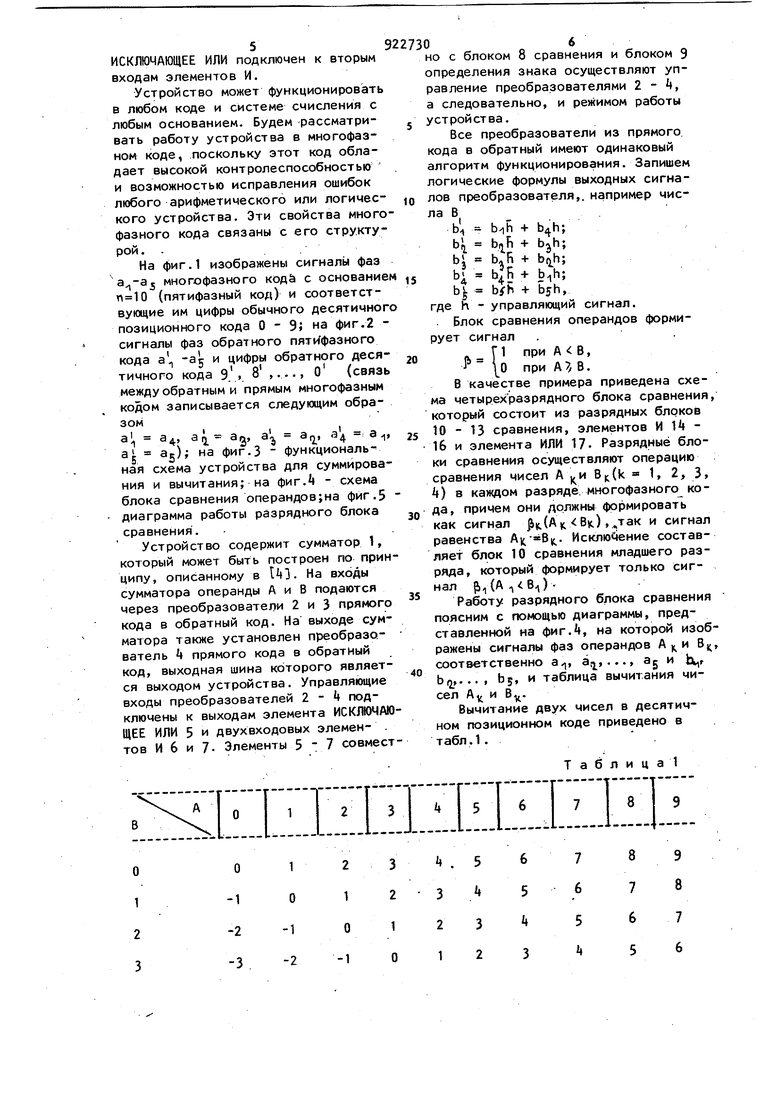

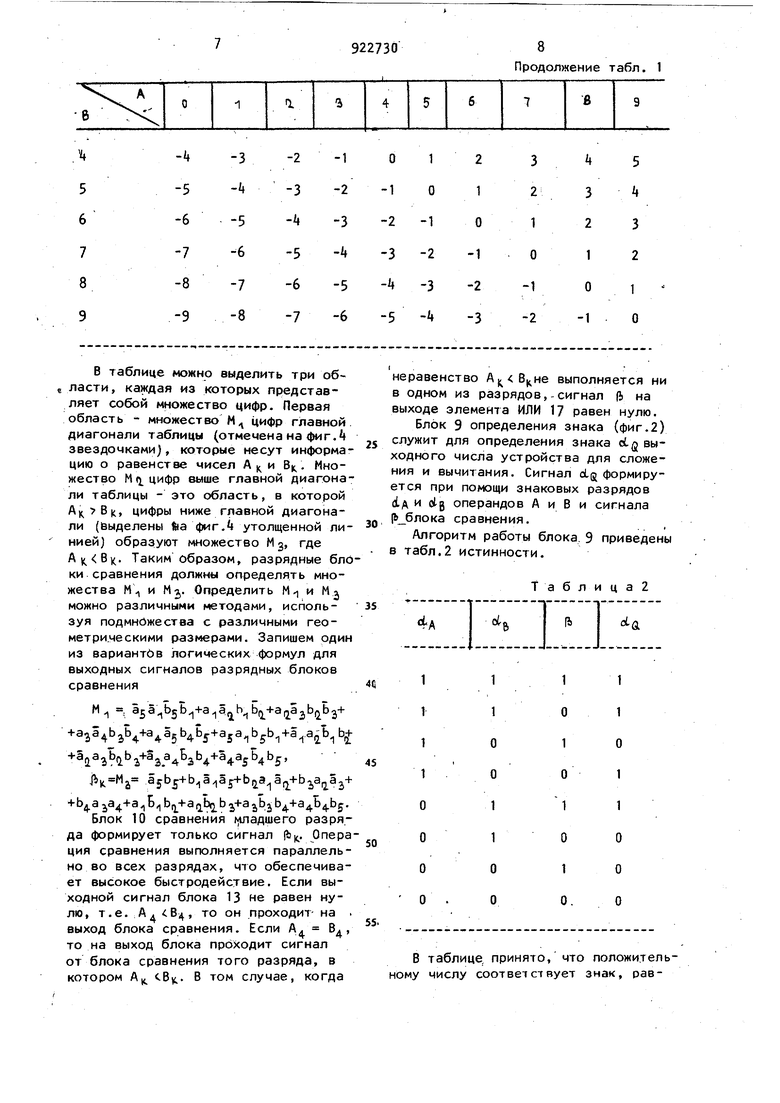

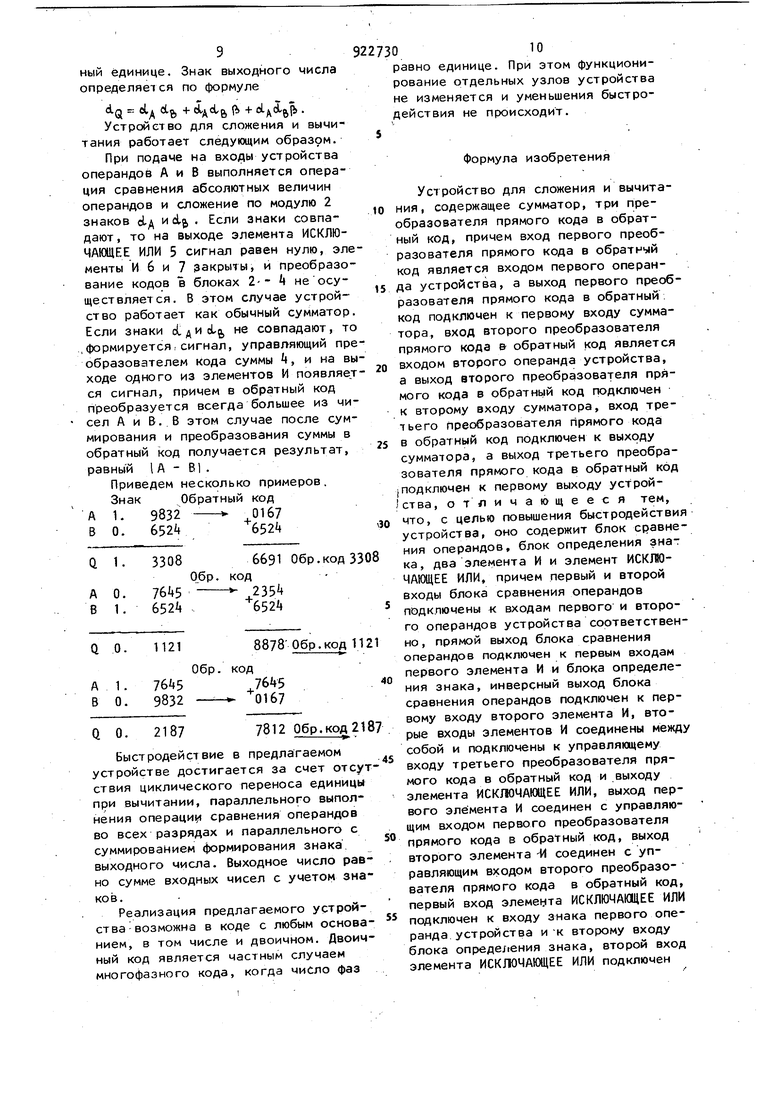

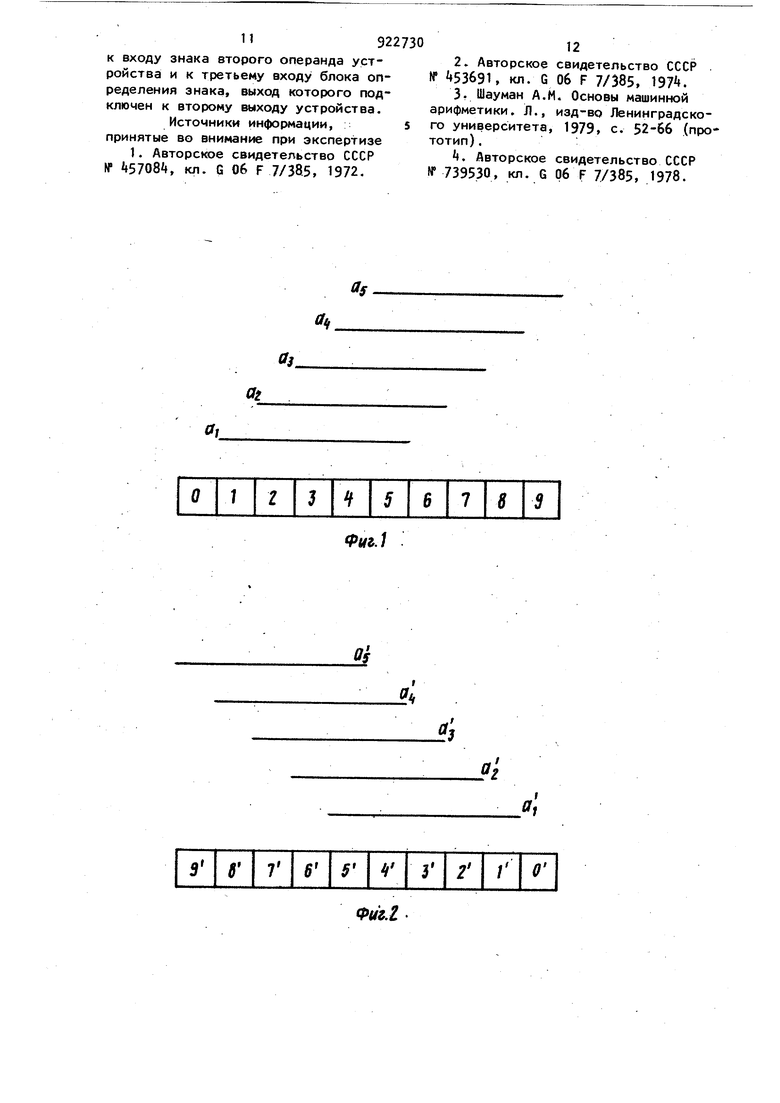

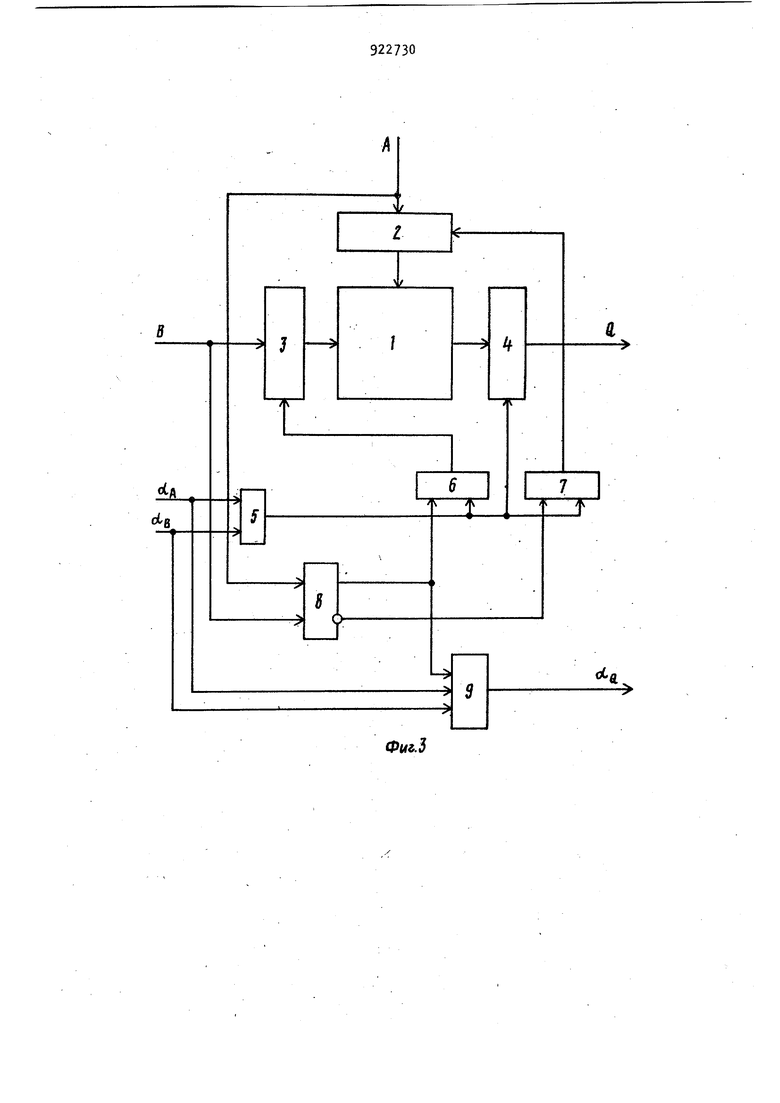

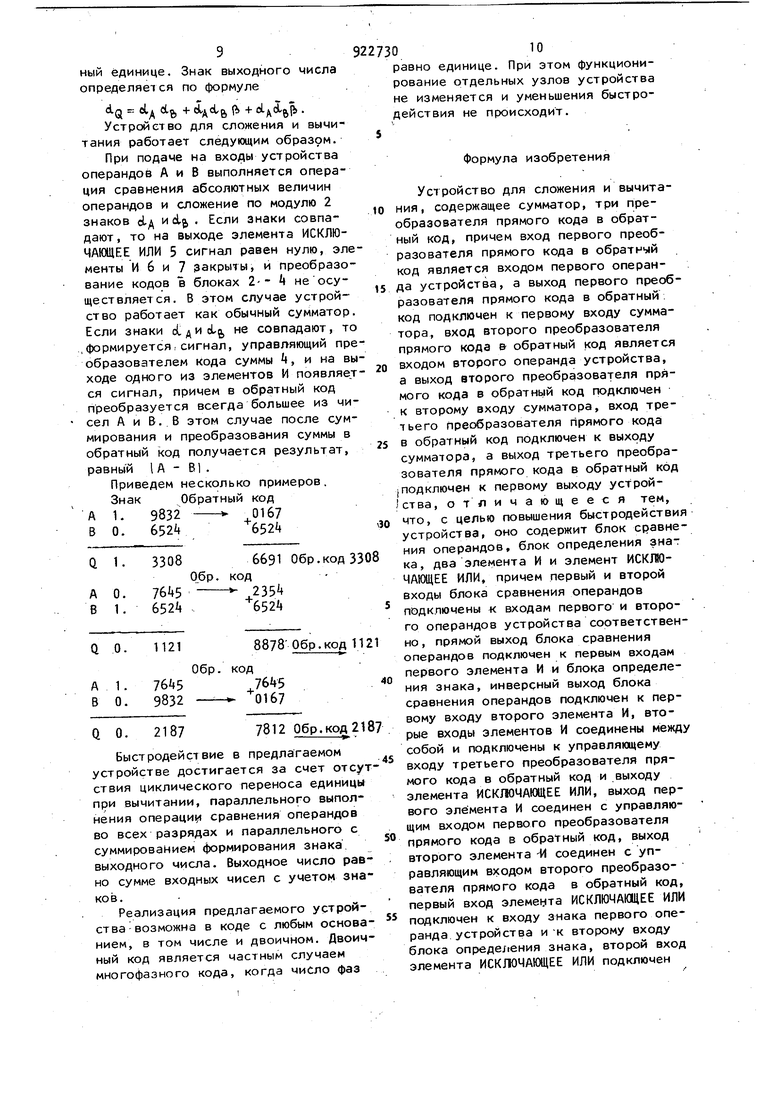

30 второго значения операндов и к шинам прямого и инверсного значения положительного переноса младшего разряда, выходы блока формирования положительнои суммы подключены к первым двум входам триггера результата к третьему и четвертому входам которого подключены шины прямого и ин версного значения отрицательного пе реноса младшего разряда 21 . Однако известные устройства имеют ограниченное применение из-за специфичности системы счисления и обладают невысоким быстродействием. Наиболее близким по технической сущности к изобретению является уст ройство, которое применимо для систем счисления с любым основанием. В устройстве для выполнения операции вычитания используется сумматор на входных шинах операндов которого устанавливаются преобразователи из прямого кода в обратный. Такой же преобразователь устанавливается на выходных шинах сумматора. Управляющие входы первых двух преобразователей соединены через логический элемент с шинами знаков операндов, а управляющий вход преобразователя на выходе сумматора соединяется через двухвходовый элемент И с шиной сигнала переноса старшего разряда сумматора, которая через другой элемент И соединена с входной шиной сигнала переноса первого разряда сумматора. Управляющие входы элементов И соединены через логическую схему с шинами знаков операндов. При выполнении операции сложения эти преобразователи не изменяют кода слагаемых и результата сложения. Для выполнения операции вычитания слагаемое, например с положительным знаком, преобразуется в обратный код, осуществляется операция сложения, и если сигнал переноса на выхо де старшего разряда сумматора отсут ствует, то результат на выходных ши нах сумматора снова преобразуется в обратный код. Если при сложении фор мируется сигнал переноса на выходе старшего разряда сумматора, то результат сложения не преобразуется . в обратный код, а увеличивается на единицу, которая подается на входную шину сигнала переноса первого разряда сумматора (циклический пере нос) 3. Наличие циклического переноса, выполнение которого может изменить результат сложения во всех разрядах устройства, снижает быстродействие выполнения операции вычитания по 9 4 сравнению с операцией суммирования в два раза. Цель изобретения - повышение быстродействия устройства. Эта цель достигается тем, что устройство для сложения и вычитания, содержащее сумматор, преобразователь кода первого операнда в обратный код, преобразователь кода второго операнда в обратный код и пр)еобразователь кода суммы в обратный код, причем вход преобразователя кода первого операнда в обратный код является первым входом устройства, а выход преобразователя кода первого операнда в обратный код подключен к первому входу сумматора, вход преобразователя кода второго операнда в обратный код является вторым входом устройства, а выход преобразователя кода второго операнда в обратный код подключен к второму входу сумматора, вход преобразователя кода суммы в обратный код подключен к выходу сумматора, а выход преобразователя суммы в обратный код подключен к первому выходу устройства, содержит блок сравнения операндов, блок определения знака, два элемента И и элемент ИСКЛЮЧАЮЩЕЕ ИЛИ, причем первый и второй входы блока сравнения операндов подключены к первому и второму входам устройства соответственно, прямой выход блока сравнения операндов подключен к первым входам первого элемента И и блока определения знака, инверс-., ный выход блока сравнения операндов подключен к первому входу второго элемента И, вторые входы элементов И соединены между собой и подключены к управляющему входу преобразователя кода суммы в обратный код, выход первого элемента И соединен с управляющим входом преобразователя кода первого операнда в обратный код, выход второго элемента И соединен с управляющим входом преобразователя кода второго операнда в обратный код, первый вход элемента ИСКЛЮЧАЮЩЕЕ ИЛИ подключен к третьему входу устройства и к второму входу блока определения знака, второй вход элемента ИСКЛЮЧАЮЩЕЕ ИЛИ подключен к четвертому входу устройства и к третьему Входу блока определения знака, выход которого подключен к второму выходу устройства, выход элемента ИСКЛЮЧАЮЩЕЕ ИЛИ подключен к вторым входам элементов И. Устройство может функционировать в любом коде и системе счисления с любым основанием. Будем рассматривать работу устройства в многофазном коде, поскольку этот код обладает высокой контролеспособностью и возможностью исправления ошибок любого арифметического или логического устройства. Эти свойства много фазного кода связаны с его структурой . . На фиг.1 изображены сигналы фаз многофазного коде с основание (пятифазный код) и соответствующие им цифры обычного десятичног позиционного кода О - 9 на фиг.2 сигналы фаз обратного пятЯфазного кода а-| -Bj и цифры обратного десятичного кода 9.., 8 ,..., О (связь между обратным и прямым многофазным кодом записывается следующим образомa, ai3 - ag, a - a, al at); на фиг.З функциональная схема устройства для суммирования и вычитания; на фиг. - схема блока сравнения операндов;на фиг.5 диаграмма работы разрядного блока сравнения. Устройство содержит сумматор 1, который может быть построен по прин ципу, описанному в . На входы сумматора операнды А и В подаются через преобразователи 2 и 3 прямого кода в обратный код. На выходе сумматора также установлен преобразователь прямого кода в обратный код, выходная шина которого является выходом устройства. Управляющие входы преобразователей 2 - подключены к выходам элемента ИСКЛЮЧАЮ ЩЕЕ ИЛИ 5 и двухвходовых элементов И 6 и 7- Элементы 5 7 совмест

1 О

О -1

-1 -2

-1

-2 -3

8 7 6 5

9 8

6 5

7 6

. 5

3Л

7 6

5 Ц

23

3

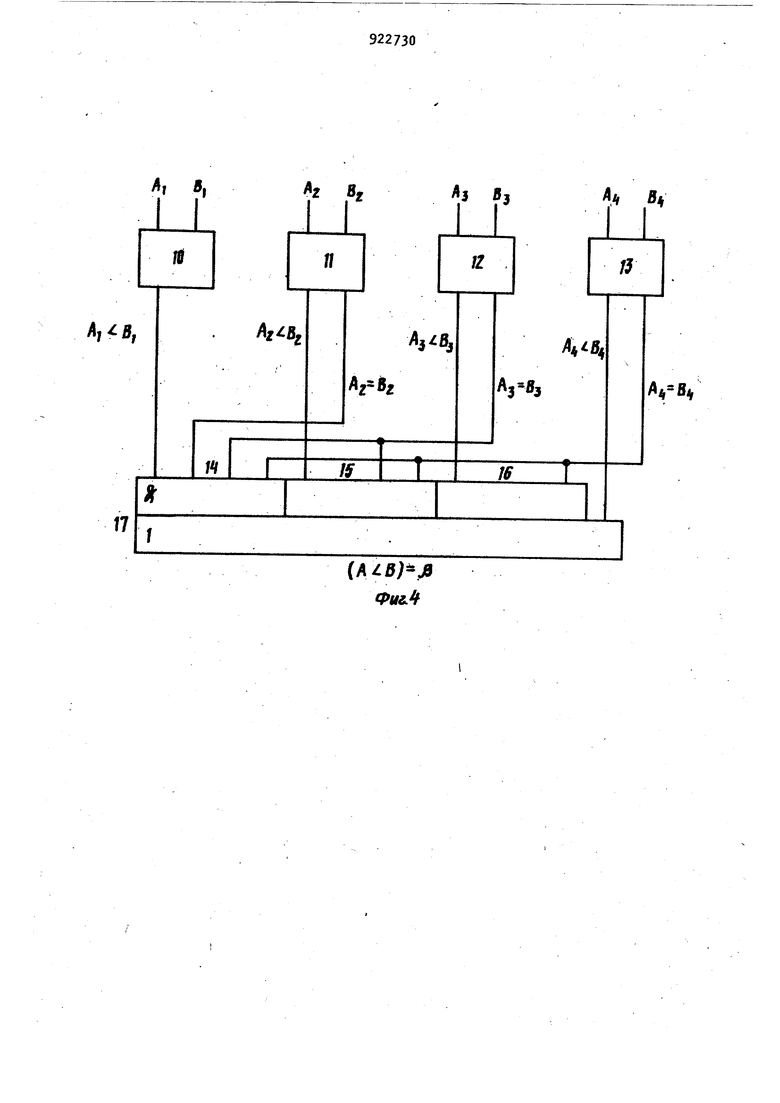

12 0 но с блоком 8 сравнения и блоком 9 определения знака осуществляют управление преобразователями 2 - , а следовательно, и режимом работы устройства. Все преобразователи из прямого кода в обратный имеют одинаковый алгоритм функционирования. Запишем логические формулы выходных сигналов преобразователя,, например числа В Ь - + bahj b||i -f bjh; b + bi + b bfb + bjh, где h - управляющий сигнал. Блок сравнения операндов формирует сигнал . ft- Р при А В, 0 О при А В. В качестве примера приведена схема четырехразрядного блока сравнения, который состоит из разрядных блоков 10-13 сравнения, элементов И Н 16 и элемента ИЛИ 17. Разрядные блоки сравнения осуществляют операцию сравнения чисел А ,и B|.(k 1, 2, 3, 4) в каждом разряде, многофазного кода, причем они должны формировать как сигнал {А ХВц), дак и сигнал равенства ,. Исключение составляет блок 10 сравнения младшего разряда, который формирует только сигнал )i(). Работу разрядного блока сравнения поясним с помощью диаграммы, представленной на фиг., на которой изображены сигналы фаз операндов А и В, соответственно а J Ь;, и таблица вычитания чио (,, .. сел AI Ч и В. Вычитание двух чисел в десятичном позиционном коде приведено в табл.1. . Таблица 1

-k

-3

-1

-2 -it

-5 -2 -3 -6 -Ц -5 -3 -6 -4

7

5 -8 -6

-7

-5 -8 -9 -7 -о

k 3 2 1

2

3

5 i 3 2

1

2

О

1

1

О

-1

О

-2 1

В таблице можно выделить три об ласти, каждая из которых представляет собой fwomecTBo цифр. Первая область - множество М цифр главной диагонали таблицы (отмечена на фиг. звездочками), которые несут информацию о равенстве чисел В. Множество М () цифр выше главной диагонали таблицы - это область, в которой , цифры ниже главной диагонали (быделены fee фиг.4 утолщенной линией) образуют множество М 3, где )(. Таким образом, разрядные блоки сравнения должны определять множества М, и Mj. Определить М и М можно различными методами, используя подмножества с различными геометри.ческими размерами. Запишем один из вариантйв логических формул для выходных сигналов разрядных блоков сравнения

л - Э5а;, +а,. Ь +а,а2 J Ь b J,

+b aja4+a B b +a,bQ,bj+ajbjb +a4.. Блок 10 сравнения («шадшего разряда формирует только сигнал (Ь. Операция сравнения выполняется параллельно во всех разрядах, что обеспечивает высокое быстродействие. Если выходной сигнал блока 13 не равен нулю, т.е. АЛ В, то он проходит- на . выход блока сравнения. Если А. B, то на выход блока проходит сигнал от блока сравнения того разряда, в котором Ац cB)t. В том случае, когда

неравенство А,Вцне выполняется ни в одном из разрядов,-сигнал (Ь на выходе элемента ИЛИ 17 равен нулю.

Блок 9 определения знака (фиг.2) служит для определения знака ctg выходного числа устройства для сложения и вычитания. Сигнал oLg формируется при помощи знаковых разрядов dA и Ыв операндов А и В и сигнала (Ь блока сравнения.

Алгоритм работы блока, 9 приведены в табл.2 истинности.

Таблица2

В таблице, принято, что положительному числу соответствует знак, равный единице. Знак выходного числа определяется по формуле -(3 Ь + Р + Устройство для сложения и вычитания работает следующим образом. При подаче на входы устройства операндов А и В выполняется операция сравнения абсолютных величин операндов и сложение по модулю 2 знаков о1д и dj , Если знаки совпадают, то на выходе элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 5 сигнал равен нулю, эле менты И 6 и 7 закрыты, и преобразо вание кодов в блоках 2-- А не осуществляется. В этом случае устройство работает как обычный сумматор Если знаки оСдисЬц, не совпадают, то .формируется,сигнал, управляющий пре образовэтелем кода суммы J, и на вы ходе одного из элементов И появляет сигнал, причем в обратный код преобразуется всегда большее из чи сел А и В..В этом случае после суммирования и преобразования суммы в обратный код получается результат, равный 1 А - В1 . Приведем несколько примеров. ЗнакОбратный код А 1. 9832 ,0167 В 0. 6524652 0. 1. 33086691 Обр.код 3 Обр. код 0. 235/+ 1.652k 652 8878Обр.код 1 Обр. код Q 0. 2187 7812 Обр.код 2 Быстродействие в предлагаемом устройстве достигается за счет отсу ствия циклического переноса единицы при вычитании, параллельного выполнения операци1 1 сравнения операндов во всех разрядах и параллельного с суммированием (формирования знака, выходного числа. Выходное число рав но сумме входных чисел с учетом зна ков. Реализация предлагаемого устройства возможна в коде с любым основа нием, в том числе и двоичном. Двоич ный код является частным случаем многофазного кода, когда число фаз равно единице. При этом функционирование отдельных узлов устройства не изменяется и уменьшения быстродействия не происходит. Формула изобретения Устройство для сложения и вычитания, содержащее сумматор, три преобразователя прямого кода в обратный код, причем вход первого преобразователя прямого кода в обратный код является входом первого операнда устройства, а выход первого преобразователя прямого кода в обратный код подключен к первому входу сумматора, вход второго преобразователя прямого кода в обратный код является операнда устройства, ° е а выход второго преобразователя пряа oLiv/ n втлгчлпгч пг опг%па л|эатопо ппо - мого кода в обратной код подключен к второму входу сумматора, вход третьего Преобразователя прямого кода в обратный код подключен к выходу сумматора, а выход третьего преобразователя прямого кода в обратный код пoдключeн к первому выходу устройства, отличающееся тем, что, с целью повышения быстродействия устройства, оно содержит блок сравнения операндов, блок определения знака, два элемента И и элемент ИСКЛЮЧАЮЩЕЕ ИЛИ, причем первый и второй входы блока сравнения операндов подключены к входам первого и второго операндов устройства соответственно , прямой выход блока сравнения операндов подключен к первым входам первого элемента И и блока определения знака, инверсный выход блока сравнения операндов подключен к первому входу второго элемента И, вторые входы элементов И соединены между собой и подключены к управляющему входу третьего преобразователя прямого кода в обратный код и выходу элемента ИСКЛОЧАЮЩЕЕ ИЛИ, выход первого элемента И соединен с управляющим входом первого преобразователя прямого кода в обратный код, выход второго элемента -И соединен с управляющим входом второго преобразователя прямого кода в обратный код, первый вход элемечта ИСКЛЮЧАЮЩЕЕ ИЛИ подключен к входу знака первого операнда устройства и-к второму входу блока опреде/гения знака, второй вход элемента ИСКЛЮЧАЩЕЕ ИЛИ подключен

11922730

к входу знака второго операнда устройства и к третьему входу блока определения 3HaKat выход которого подключен к второму выходу устройства.

Источники информации, : 5 принятые во внимание при экспертизе

12

2 Авторское свидетельство СССР N 53691, кл. G Об F 7/385, 197.

3- Шауман A.M. Основы машинной арифметики. Л., изд-во Ленинградского университета, 1979, с. 52-66 (прототип) .

. Авторское свидетельство СССР №739530, кл. G 06 F 7/385, 1978.

Фнъ.1

Фиг,2

В

(ig

-

Фмг.5 А, в, Аг

,

()-Я Фи взК, в„

АК а Ог

в.

Фиг. 5

Авторы

Даты

1982-04-23—Публикация

1980-09-02—Подача