1(54) ОДНОРАЗРЯДНЫЙ ДЕСЯТИЧНЫЙ СУММАТОР

| название | год | авторы | номер документа |

|---|---|---|---|

| Сумматор-вычитатель | 1981 |

|

SU993254A1 |

| Последовательный двоично-десятичный сумматор-вычитатель | 1978 |

|

SU734685A1 |

| Одноразрядный десятичный сумматор- ВычиТАТЕль | 1977 |

|

SU807275A1 |

| Устройство для вычитания десятичных чисел | 1975 |

|

SU607216A1 |

| ДВОИЧНО-ДЕСЯТИЧНЫЙ НАКАПЛИВАЮЩИЙ СУММАТОР | 1971 |

|

SU293241A1 |

| Устройство для вычитания двоично-десятичных кодов | 1982 |

|

SU1043640A1 |

| Устройство для последовательного сложения и вычитаний чисел | 1976 |

|

SU579613A1 |

| ПАРАЛЛЕЛЬНЫЙ СУММАТОР-ВЫЧИТАТЕЛЬ НА НЕЙРОНАХ СО СКВОЗНЫМ ПЕРЕНОСОМ | 2012 |

|

RU2523942C2 |

| Сумматор-вычитатель | 1988 |

|

SU1536373A1 |

| СУММАТОР-ВЫЧИТАТЕЛЬ СТАРШИМИ РАЗРЯДАМИ ВПЕРЕД НА НЕЙРОНАХ | 2002 |

|

RU2205444C1 |

I

Изобретение относится к области цифровой вычислительной техники.

Известны сумматсфы двоичио-десятичиых чисел, которые, однако, не могут Ьыг1( иепосредствеипо применены для вычитании; двоично-десятичных чисел {.

Известны устройства для сложения ц вычитания двоично-де,сятнчных чисел {2 и {3, содержащие входные н выходные сумматоры, блоки инвертирования кодов и блоки коррекции и формирования межтетрадйых переносов. Недостатками этих устройств является сложность их выполнення.

В качестве прототипа выбраи одибразрядиый десятичный сумматор, содержащий корректирующий двоичный сумматор, два элемента И и элемент ИЛИ, перв1 1Й и второй входы подключены к выходам пер вого и второго элементов И, а выход соединен с выходом переноса десятичного сумматора и первым входом первого разряда кор- рент ИрующегЬ двоичного сумматора, выходы которого соединены со вторым, третьим и четвертым разрядами выхода суммы десятичного сумматора 4.

Недостатком такого cyMMiaTupa является невозможность прямого вычитания десятичных чисел.

Целью изобретения являейгся расширение функциональных возможностей десятичного

сумматора, заключающееся в возможности вычитания десятичных чисел.

Для достижения этой цели десятичный сумматор содержит двоичный сумматор-вычитатель и третий и четвертый элемееты И,

выходы которых пбдняючены к первым входам соответственно второго н третьего раз-рядов корректирующего двоичного сумматора, первые входы соединены с выходом элемента ИЛИ, а вторые входы - соответственно с управляющими шннами сложения

и вычитания, которые подключены также к управляющим входам двоичного суммато ра-вычитателя, информационные входы которого соединены с вхЬдами первого и второго операндов и входом переноса десятичкого cytjMaTopa, выход первого разряда двоичного сумматора-вычитателя подклк)чен к первому разряду выхода суммы десятичноto сумматора, а выходы второго, третьего и

.четвертого разрядов подключены ко вторым входам соответственно первого, второго и третьего разрядов корректирующего двоичкого сумматора, входы первого элемента И подключены к выходам второго и четвертого разрядов, а входы второго элемента И - к выходам третьего и четвертого разрядов двоичного сумматора-вычитатёля, выход переноса которого подключен к третьему входу элемента ИЛИ.

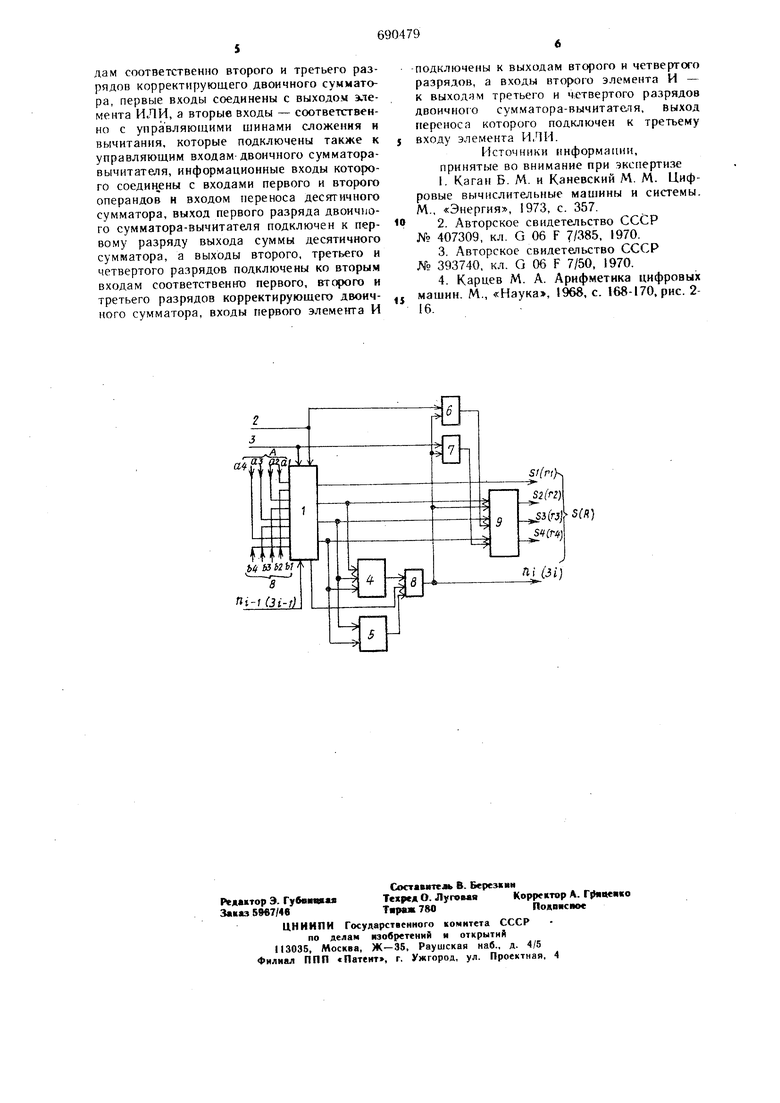

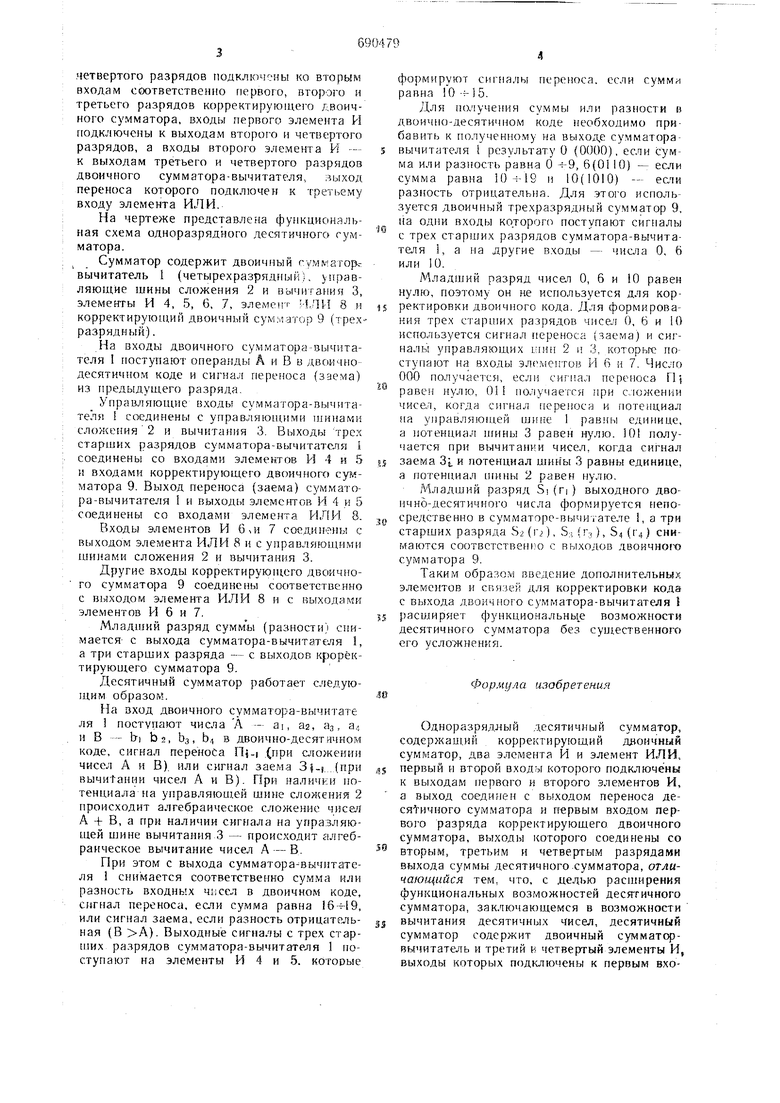

На чертеже представлена функциональная схема одноразрядного десятичного сумматора.

Сумматор содержит двоичный сумматор -: вычитатель 1 (четырехразрядный), управляющие шины сложения 2 и вычитания 3,

элементы И 4, 5, б, 7, .элемент ИЛИ 8 .и корректирующий двоичный сумматор 9 (трехразрядный).

На входы двоичного сумматора-вычитатёля 1 поступают операнды А и В в двоичнодесятичном коде и сигнал переноса (заема) из предыдущего разряда.

Управляющие входы сумматора-вычитателя соединены с управляющими щинами сложения 2 и вычитания 3. Выходы трех старших разрядов сумматора-вычитателя I соединены со входами элементов И 4 и 5 и входамй корректируюЩёГОдйШМ гоШсумматора 9. Выход переноса (заема) сумматора-вычитателя i и выходы элементов И 4 и 5 соединены со входами элемента ИЛИ 8.

Входы элементов И 7 соединены с выходом элемента ИЛИ 8 и с управляющими щинами сложения 2 и вычитания 3.

Другие входы корректирующего двричного сумматора 9 соединены сШЯ1 8те&нн о с выходом элемента ИЛИ 8 и с выходами элементов И б и 7.

Младщий разряд суммы (разности) снимается- с выхода сумматора-вычитателя 1, а три старших разряда - с выходов крорёктирующего сумматора 9.

Десятичный сумматор работает следующим образом.. . .

. На вход двоичного сумматора-вычитате ля 1 поступают числа А - ai, аг, аз, а4

и В - Ь) b 2, Ьз, Ь4 в двоично-десятичном коде, сигнал переноса П}- .(ри сложении чисел А и В) или сигнал заема 3}-|..(при вычитании чисел А и В). При наличии потенциала на угфавляющей шине сложения 2 происходит алгебраическое сложение чHcfei А 4- Bs а при наличии сигнала на управляющей,щине вычитания 3 - происходит алгебраическое вычитание чисел А -- В..

: При этом с выхода сумматора -ВйЧ11Тателя i снимается соответствейНО сумма или разность входных чисел в двоичном коде, сигнал переноса, если сумма равна ,

или сигнал заема, если разность отрицательная (В А). Выходные сигналы с трех старших разрядов сумматора-вычитателя 1 поступают на элементы И 4 и 5. которые

формируют сигналы переноса, если сумма равна .

Для получения суммы или разности в двоично-десятичном коде необходимо прибавить к полученному на выходе сумматоравычитателя 1 результату О (0000). если сумма или разность равна О -f-9, 6(0110) - если сумма равна 10-;-19 и 10(1010) - если разность отрицательна. Для этого используется двоичный трехразря.аный сумматор 9, на одни входы которого поступают сигналы с трех старших разрядов сумматора-вычитателя 1, а на другие входы - числа О, 6 или 10. .

Младщий разряд чисел О, 6 и 10 равен нулю, поэтому он не используется для корректировки двоичного кода. Для формирования трех старщих разрядов чисел О, б и 10 используется сигнал переноса (заема) и сйгналь управляющих щин 2 и 3, которые поступают на входы элементов И 6 и 7. Число 00) получается, если сигнал переноса П|

равен нулю, 011 получается при сложении чисел, кс1гда сигнал переноса и потенциал на управляющей шине 1 равны единице, а поТенц,иал щины 3 равен нулю. 101 получается при вычитании чисел, когда сигнал

заема 3i и потенциал щины 3 равны единице, а потенциал щины 2 равен нулю. Младщий разряд Si(ri) выходного двоично-десятичного числа формируется непосрёдственно в сумматоре-вычитателе 1, а три старщих разряда Si (гг), 5з (Гз), 84 (Г4) снимаются соответственно с выходов двоичного сумматора 9.

Хаким образом введение дополнительных элемё ов и связей для корректировки кода с выхода двоичного сумматора-вычитателя I

расшир яет функциональнее возможности десятичного сумматора без существенного его усложнения.

Формула изобретения

Одноразрядный десятичный сумматор, содержащий . корректирующий двоичный сумматор, два элемента И и элемент ИЛИ,

первый и второй входы которого подключены к выходам первого и второго элементов И, а выход соединен с выходом переноса деся ичнргр сумматора и первым входом первого разряда корректирующего двоичного суммат6|ра, выходы которого соединены со

вторым, третьим и четвертым разрядами выхода суммы десятичного сумматора, отличающийся тем, что, Q дедью расширения функциональных возможностей десятичного сумматора, заключающемся в возможности

вычитания десятичных чисел, десятичный сумматор содержит двоичный сумматфвычитатель и третий и четвертый элементы И, выходы которых подключены к первым входам соответственно второго и третьего разрядов корректирующего двоичного сумматора, первые входы соединены с выходом элемента ИЛИ, а вторые входы - соответственно с управляющими щинами сложения и вычитания, которые подключены также к управляющим входам двоичного сумматоравычитателя, информационные входы которого соединены с входами первого и второго операндов н входом переноса десетичного сумматора, выход первого разряда двоичного сумматора-вычитателя подключен к первому разряду выхода суммы десятичного сумматора, а выходы второго, третьего и четвертого разрядов подключены ко вторым входам соответственно первого. Второго и третьего разрядов корректирующего двоичного сумматора, входы первого элемента И

-подключены к выходам второго и четвертого разрядов, а входы второго элемента И - к выходам третьего и четвертого разрядов двоичного сумматора-вычитателя, выход переноса которого подключен к третьему входу элемента ИЛИ.

Источники информации, принятые во внимание при экспертизе

0 № 407309, кл. G 06 F 7/385, 1970.

Авторы

Даты

1979-10-05—Публикация

1975-07-23—Подача