1

Изобретение относится к области вычислительной техники и может быть использовано при построении арифметических устройств ЭВМ.

Целью.изобретения является расширение функциональных возможностей за счет суммирования операндов в двоичном коде.

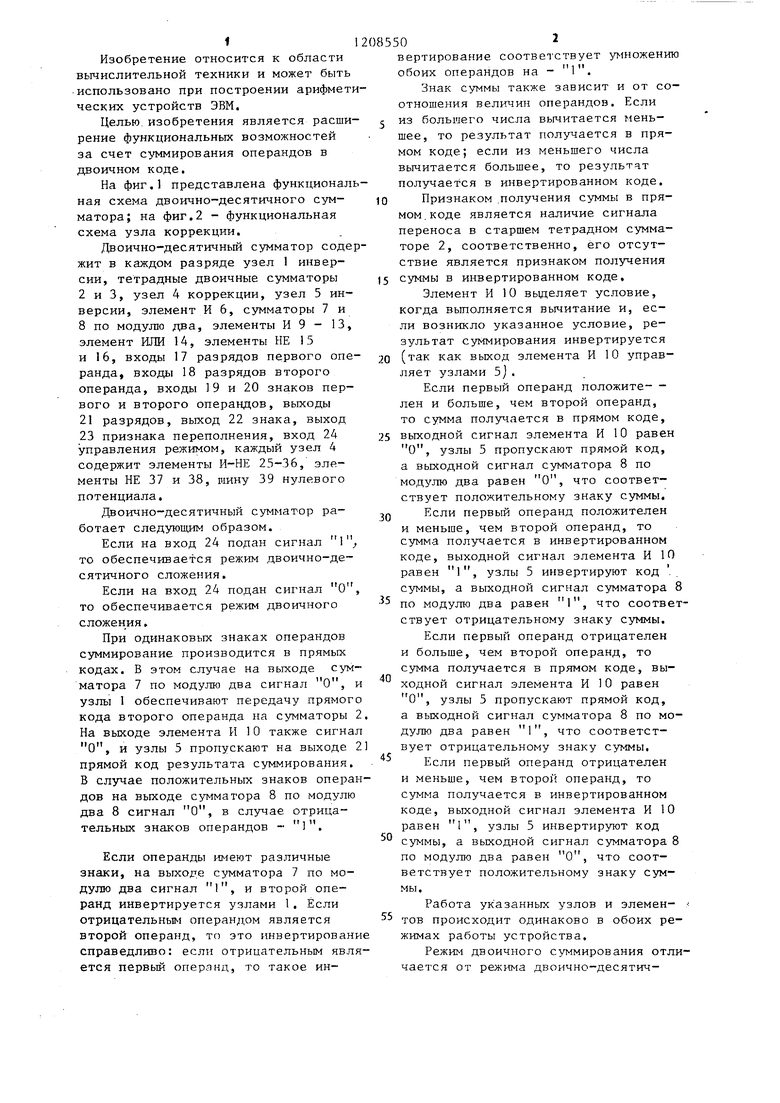

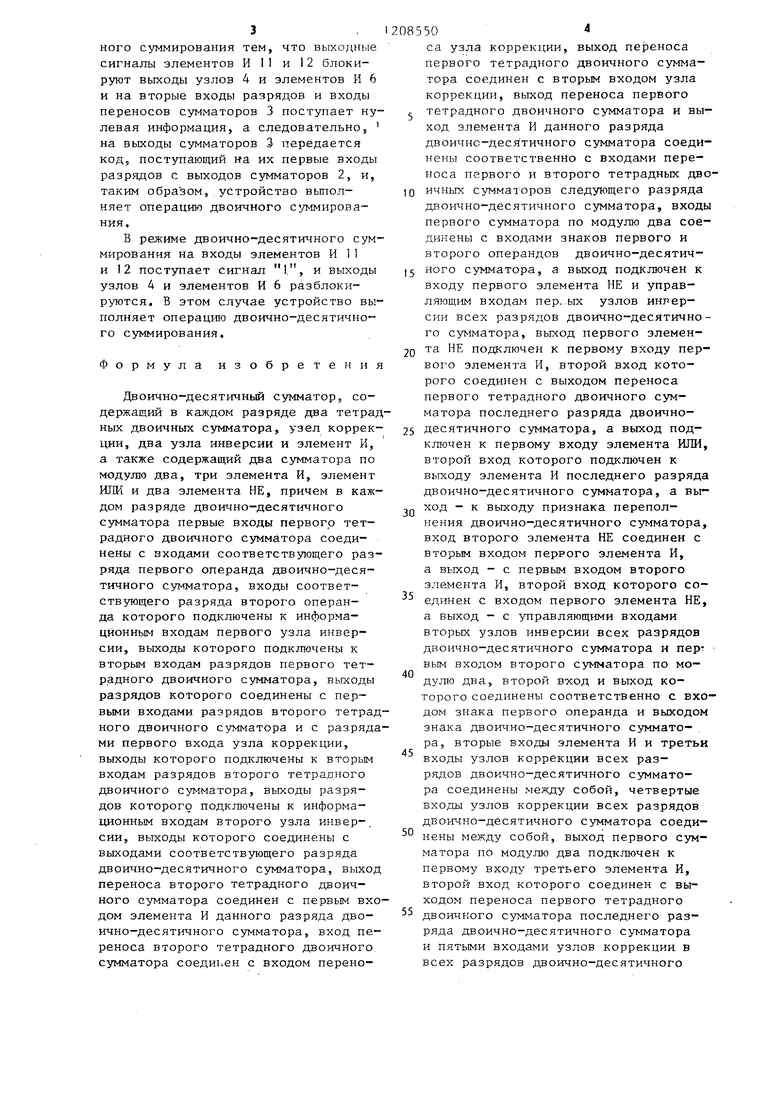

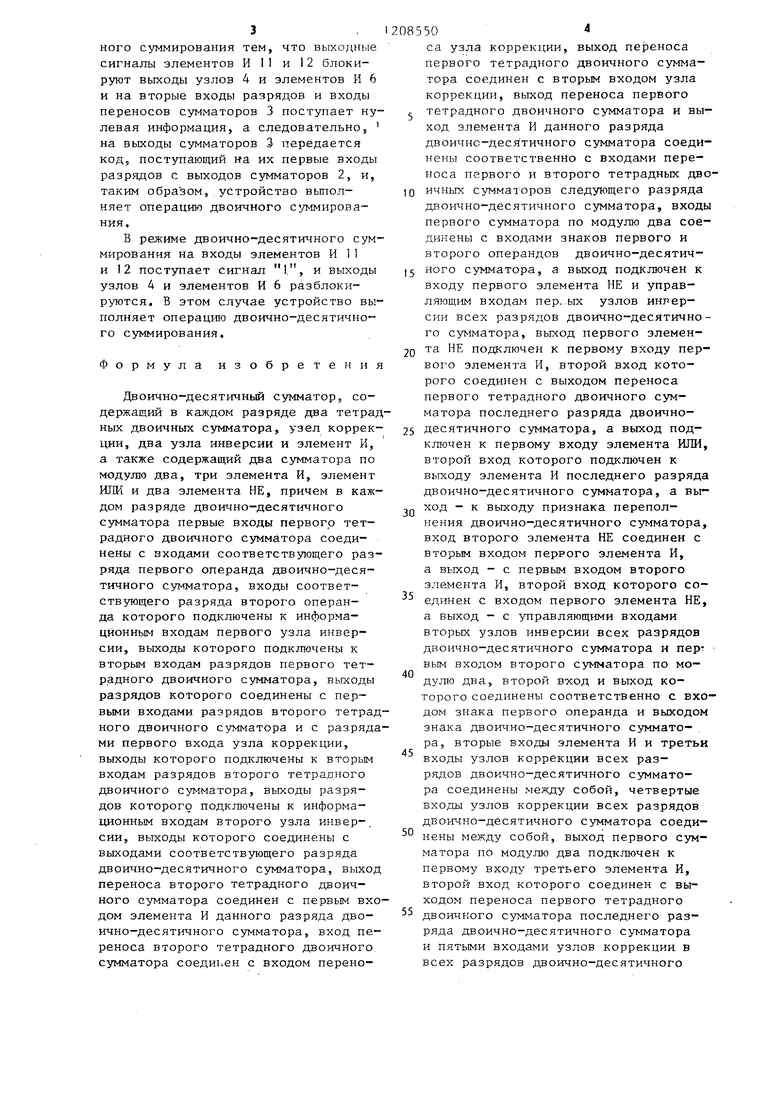

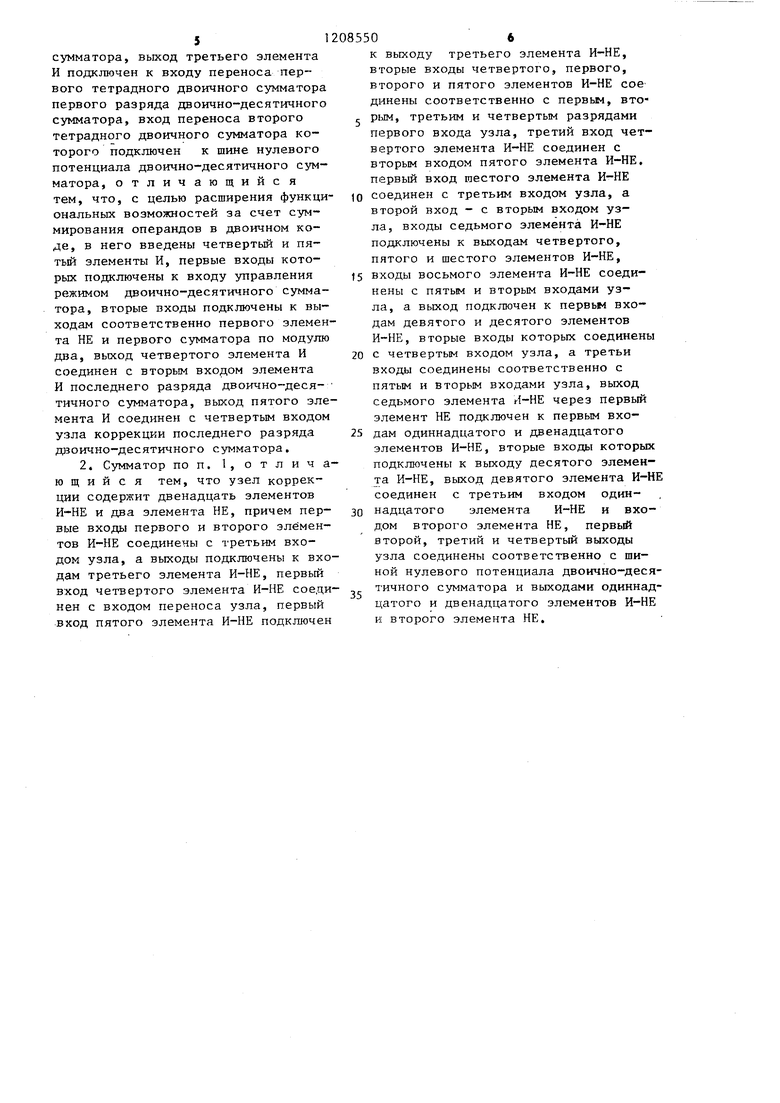

На фиг.1 представлена функциональная схема двоично-десятичного сумматора; на фиг.2 - функциональная схема узла коррекции.

Двоично-десятичный сумматор содержит в каждом разряде узел 1 инверсии, тетрадные двоичные сумматоры 2 и 3, узел 4 коррекции, узел 5 инверсии, элемент И 6, сумматоры 7 и 8 по модулю два, элементы И 9 - 13, элемент ИЛИ 14, элементы НЕ 15 и 16, входы 17 разрядов первого операнда, входы 18 разрядов второго операнда, входы 19 и 20 знаков первого и второго опера1щов, выходы 21 разрядов, выход 22 знака, выход 23 признака переполнения, вход 24 управления режимом, каждый узел 4 содержит элементы И-НЕ 25-36, элементы НЕ 37 и 38, шину 39 нулевого потенциала.

Двоично-десятичный сумматор работает следующим образом.

Если на вход 24 подан сигнал 1 то обеспечивается режим двоично-десятичного сложения.

Если на вход 24 подан сигнал О, то обеспечивается режим двоичного сложения.

При одинаковых знаках операндов суммирование производится в прямых кодах. В этом случае на выходе сумматора 7 по модулю два сигнал О, и узлы 1 обеспечивают передачу прямого кода второго операнда на сумматоры 2 На выходе элемента И 10 также сигнал О, и узлы 5 пропускают на выходе 2 прямой код результата суммирования. В случае положительных знаков операндов на выходе сумматора 8 по модулю два 8 сигнал О, в случае отрицательных знаков операндов - 1.

Если операнды имеют различные знаки, на выходе сумматора 7 по модулю два сигнал 1, и второй операнд инвертируется узлами 1. Если отрицательным операндом является второй операнд, то это инвертировани справедливо: если отрицательным является первый операнд, то такое ин

085502

вертирование соответствует умножению обоих операндов на - 1.

Знак суммы также зависит и от соотношения величин операндов. Если 5 из большего числа вьиитается меньшее, то результат получается в прямом коде; если из меньшего числа вычитается большее, то результат получается в инвертированном коде. 10 Признаком .получения суммы в прямом, коде является наличие сигнала переноса в старшем тетрадном сумматоре 2, соответственно, его отсутствие является признаком получения 15 суммы в инвертированном коде.

Элемент И 10 вьщеляет условие, когда вьшолняется вычитание и, если возникло указанное условие, результат суммирования инвертируется УО (так как выход элемента И 10 управляет узлами 5).

Если первый операнд положите- - лен и больше, чем второй операнд, то сумма получается в прямом коде, 25 выходной сигнал элемента И 10 равен О, узлы 5 пропускают прямой код, а выходной сигнал сумматора 8 по О.

30

.35

40

45

50

55

модулю два равен и , что соответствует положительному знаку суммы.

Если первый операнд положителен и меньше, чем второй операнд, то сумма получается в инвертированном коде, выходной сигнал элемента И 10 равен 1, узлы 5 инвертируют код . суммы, а выходной сигнал сумматора 8 по модулю два равен 1, что соответствует отрицательному знаку суммы.

Если первый операнд отрицателен и больше, чем второй операнд, то сумма получается в прямом коде, выходной сигнал элемента И 10 равен О, узлы 5 пропускают прямой код, а выходной сигнал сумматора 8 по модулю два равен 1, что соответствует отрицательному знаку суммы.

Если первый операнд отрицателен и меньше, чем второй операнд, то сумма получается в инвертированном коде, выходной сигнал элемента И 10 равен 1, узлы 5 инвертируют код суммы, а выходной сигнал сумматора 8 по модулю два равен О, что соответствует положительному знаку суммы.

Работа ук азанных узлов и элемен- тов происходит одинаково в обоих режимах работы устройства.

Режим двоичного суммирования отличается от режима двоично-десятич-

ного суммирования тем, что выходные сигналы элементов И II и 12 блокируют выходы узлов 4 и элементов И 6 и на вторые входы разрядов и входы переносов сумматоров 3 поступает нулевая информация, а следовательно, на выходы сумматоров 3 передается код, поступающий на их первые входы разрядов с выходов сумматоров 2, и, таким образом, устройство выполняет операцию двоичного суммирования.

В режиме двоично-десятичного суммирования на входы элементов И 11 и 12 поступает сигнал 1, и выходы узлов 4 и элементов И 6 разблокируются. В этом случае устройство выполняет операцию двоично-десятично™ го суммирования.

Формула изобретения

Двоично-десятичный сумматор, содержащий в каждом разряде два тетрадных двоичных сумматора, узел коррекции, два узла инверсии и элемент И, а также содержащий два сумматора по модулю два, три элемента И, элемент ИЛИ и два элемента НЕ, причем в каждом разряде двоично-десятичного сумматора первые входы первого тетрадного двоичного сумматора соединены с входами соответствующего разряда первого операнда двоично-десятичного сумматора, входы соответствующего разряда второго операнда которого подключены к информационным входам первого узла инверсии, выходы которого подключены к вторым входам разрядов первого тетрадного двоичного сумматора, выходы разрядов которого соединены с первыми входами разрядов второго тетрадного двоичного сумматора и с разрядами первого входа узла коррекции, выходы которого подключены к вторым входам разрядов второго тетрадного двоичного сумматора, выходы разрядов которого подключены к информационным входам второго узла инвер-. сии, выходы которого соединены с выходами соответствующего разряда двоично-десятичного сумматора, выход переноса второго тетрадного двоичного сумматора соединен с первым входом элемента И данного разряда двоично-десятичного сумматора, вход переноса второго тетрадного двоичного, сумматора соедиьен с входом перено208550Л

са узла коррекции, выход переноса первого тетрадного двоичного сумматора соединен с вторым входом узла коррекции, выход переноса первого

, тетрадного двоичного сумматора и выход элемента И данного разряда двоичнс-деся тичного сумматора соединены соответственно с входами переноса первого и второго тетрадных дво(0 ичных сумматоров следующего разряда двоично-десятичного сумматора, входы первого сумматора по модулю два соединены с входами знаков первого и второго операндов двоично-десятич-

15 ного сумматора, а выход подключен к входу первого элемента НЕ и управляющим входам пер..ых узлов иняер- сии всех разрядов двоично-десятичного сумматора, вькод первого элемен20 та НЕ подключен к первому входу первого элемента И, второй вход которого соединен с выходом переноса первого тетрадного двоичного сумматора последнего разряда двоично-

25 десятичного сумматора, а выход подключен к первому входу элемента ИЛИ, второй вход которого подключен к выходу элемента И последнего разряда двоично-десятичного сумматора, а вы-

30

ход - к выходу признака перепол-

нения двоично-десятичного сумматора, вход второго элемента НЕ соединен с вторым входом первого элемента И, а выход - с первым входом второго элемента И, второй вход которого со- единен с входом первого элемента НЕ, а выход - с управляющими входами вторых узлов инверсии всех разрядов двоично-десятичного сумматора и пер - вым входом второго сумматора по модулю два, второй вход и выход которого соединены соответственно с входом знака первого операнда и выходом знака двоично-десятичного сумматора, вторые входы элемента И и третьи входы узлов коррекции всех разрядов двоично-десятичного сумматора соединены между собой, четвертые входы узлов коррекции всех разрядов двоично-десятичного сумматора соединены между собой, выход первого сумматора по модулю два подключен к первому входу третьего элемента И, второй вход которого соединен с выходом переноса первого тетрадного двоичного сумматора последнего разряда двоично-десятичного сумматора и пятыми входами узлов коррекции в всех разрядов двоично-десятичного

51

сумматора, выход третьего элемента И подключен к входу переноса первого тетрадного двоичного сумматора первого разряда двоично-десят1«ного сумматора, вход переноса второго тетрадного двоичного сумматора которого подключен к шине нулевого потенциала двоично-десятичного сумматора, отличающийс я тем, что, с целью расширения функциональных возможностей за счет с ум- мирования операндов в двоичном коде, в него введены четвертый и пя- тьй элементы И, первые входы которых подключены к входу управления режимом двоично-десятичного сумматора, вторые входы подключены к выходам соответственно первого элемента НЕ и первого сумматора по модулю два, выход четвертого элемента И соединен с вторым входом элемента И последнего разряда двоично-деся- тнчного сумматора, выход пятого элемента И соединен с четвертым входом узла коррекции последнего разряда двоично-десятичного сумматора.

2. Сумматор по п. 1, о т л и ч а- ю щ и и с я тем, что узел коррекции содержит двенадцать элементов И-НЕ и два элемента НЕ, причем первые входы первого и второго элементов И-НЕ соединены с третьим входом узла, а выходы подключены к входам третьего элемента И-НЕ, первый вход четвертого элемента И-НЕ соединен с входом переноса узла, первый вход пятого элемента И-НЕ подключен

2085506

к выходу третьего элемента И-НЕ, вторые входы четвертого, первого, второго и пятого элементов И-НЕ сое динены соответственно с первым, втоJ piJM, третьим и четвертым разрядами первого входа узла, третий вход четвертого элемента И-НЕ соединен с вторым входом пятого элемента И-НЕ, первый вход шестого элемента И-НЕ

)0 соединен с третьим входом узла, а второй вход - с вторым входом узла, входы седьмого элемента И-НЕ подключены к выходам четвертого, пятого и шестого элементов И-НЕ,

15 входы восьмого элемента И-НЕ соединены с пятьм и вторым входами узла, а выход подключен к первьм входам девятого и десятого элементов И-НЕ, вторые входы которых соединены

20 с четвертым входом узла, а третьи входы соединены соответственно с пятым и вторым входами узла, выход седьмого элемента И-НЕ через первый элемент НЕ подключен к первым вхо-

25 дам одиннадцатого и двенадцатого

элементов И-НЕ, вторые входы которых подключены к выходу десятого элемента И-НЕ, выход девятого элемента И-НЕ соединен с третьим входом одиннадцатого элемента И-НЕ и входом второго элемента НЕ, первый второй, третий и четвертый выходы узла соединены соответственно с шиной нулевого потенциала двоично-десятичного сумматора и выходами одиннадцатого и двенадцатого элементов И-НЕ и второго элемента НЕ.

30

35

.

гу

Щ-

| название | год | авторы | номер документа |

|---|---|---|---|

| Двоично-десятичный сумматор | 1981 |

|

SU1019441A1 |

| Матричное устройство для умножения двоичных и десятичных чисел | 1983 |

|

SU1200282A1 |

| УСТРОЙСТВО для СУММИРОВАНИЯ | 1973 |

|

SU393740A1 |

| Устройство для суммирования Фибоначчи-десятичных кодов | 1989 |

|

SU1649535A1 |

| Операционный модуль | 1984 |

|

SU1406592A1 |

| Устройство для умножения | 1982 |

|

SU1229757A1 |

| Устройство для умножения | 1987 |

|

SU1495785A1 |

| Устройство для умножения | 1988 |

|

SU1670685A1 |

| УСТРОЙСТВО ДЛЯ УМНОЖЕНИЯ ЧИСЕЛ В КОДЕ "1 ИЗ 4" | 2003 |

|

RU2251144C1 |

| Арифметико-логическое устройство | 1978 |

|

SU922727A1 |

Изобретение относится к области вычислительной техники и может быть использовано при построении арифметических устройств ЭВМ. Целью изобретения является расширение функциональных возможностей за счет суммирования операндов в двоичном коде. Двоично-десятичный сумматор содержит в каждом разряде 2 узла инверсии, 2 тетрадных двоичных сумматора, узел коррекции, элемент И, 2 сумматора по модулю два, 5 элементов И, элемент ИЛИ, 2 элемента НЕ. Каждый узел коррекции содержит 12 элементов И-НЕ, 2 элемента НЕ. Расширение функциональных возможностей достигается за счет суммирования операндов в двоичном коде введением двух элементов И. 1 з.п. ф-лы, 2 ил. с |С о 00 сд СП

ВНИИПИ Заказ 289/58 Тираж 673 Подписное Филиал ШШ Патент, г.Ужгород, ул.Проектная, 4

| УСТРОЙСТВО для СУММИРОВАНИЯ | 0 |

|

SU393740A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1986-01-30—Публикация

1983-11-29—Подача