(54) ЦИФРОВОЙ ПРЕОБРАЗОВАТЕЛЬ КООРДИНАТ

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для цифрового преобразования координат | 1982 |

|

SU1019445A1 |

| Устройство для умножения и деления с плавающей точкой | 1985 |

|

SU1278837A1 |

| Цифровое устройство для преобразования координат | 1981 |

|

SU960808A1 |

| Устройство для вычисления скалярного произведения двух векторов | 1981 |

|

SU955088A1 |

| Устройство для цифровой обработки сигналов | 1985 |

|

SU1336028A1 |

| Устройство для преобразования координат | 1984 |

|

SU1179324A1 |

| НЕЙРОПРОЦЕССОР, УСТРОЙСТВО ДЛЯ ВЫЧИСЛЕНИЯ ФУНКЦИЙ НАСЫЩЕНИЯ, ВЫЧИСЛИТЕЛЬНОЕ УСТРОЙСТВО И СУММАТОР | 1998 |

|

RU2131145C1 |

| Устройство для моделирования графов | 1989 |

|

SU1709346A2 |

| Устройство для деления | 1990 |

|

SU1709352A1 |

| Устройство для поворота вектора | 1983 |

|

SU1144104A1 |

t

Изобретение относится к цифровой вычислительной технике и может быть использовано д.1я преобразования прямоугольных и полярных координат.

....

Из1вестно устройство, реализующее .aлгqpитм Волдера, содержащее сумматоры, сдвигающие регистры, ПЗУ констант и блок управления Г.

Недостатком данного устройства является относительно низкое быстродействие.

Наиболее близким по технической сущности к изобретению является устройство для вычисления значений координат вектора 2.

Недостатком известного устройства является относительно низкое быстрО|действие, а также деформация длины вектора в результате его , для компенсации котсрой возникает нео& ххпямость в проведении второго цикла : . {феобразования, что снижает быстродействие устройства.

Цель изобретения - повьоиение быстродействия устройства.

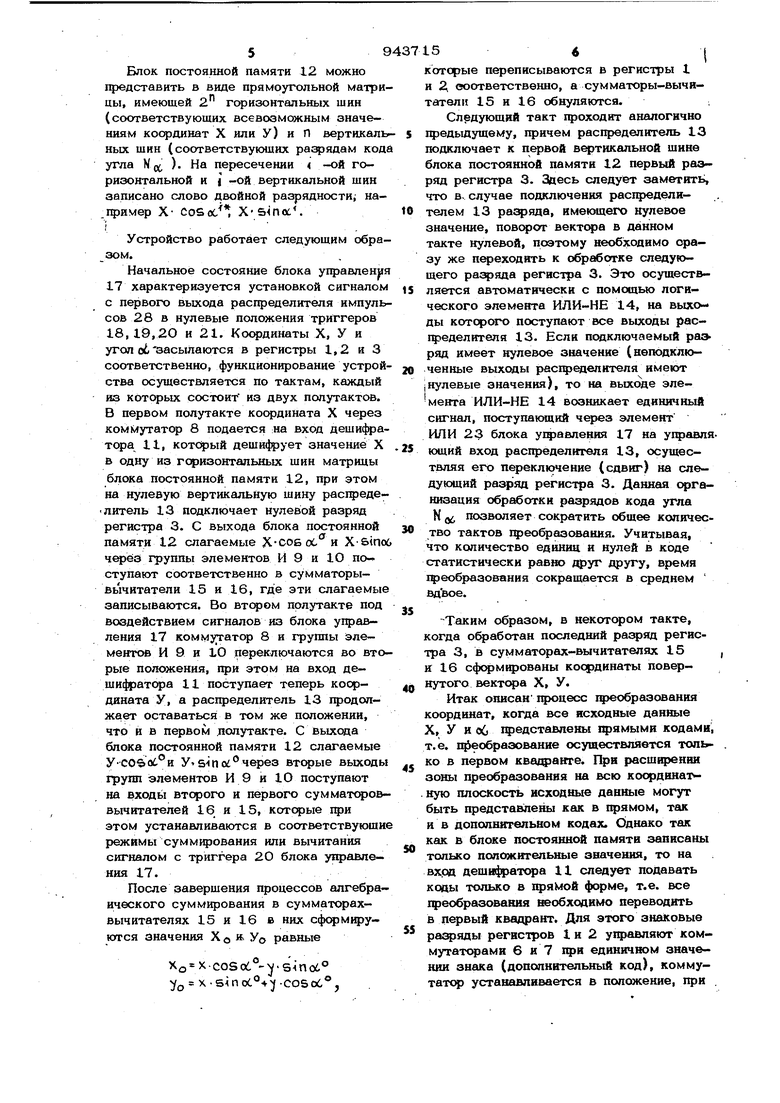

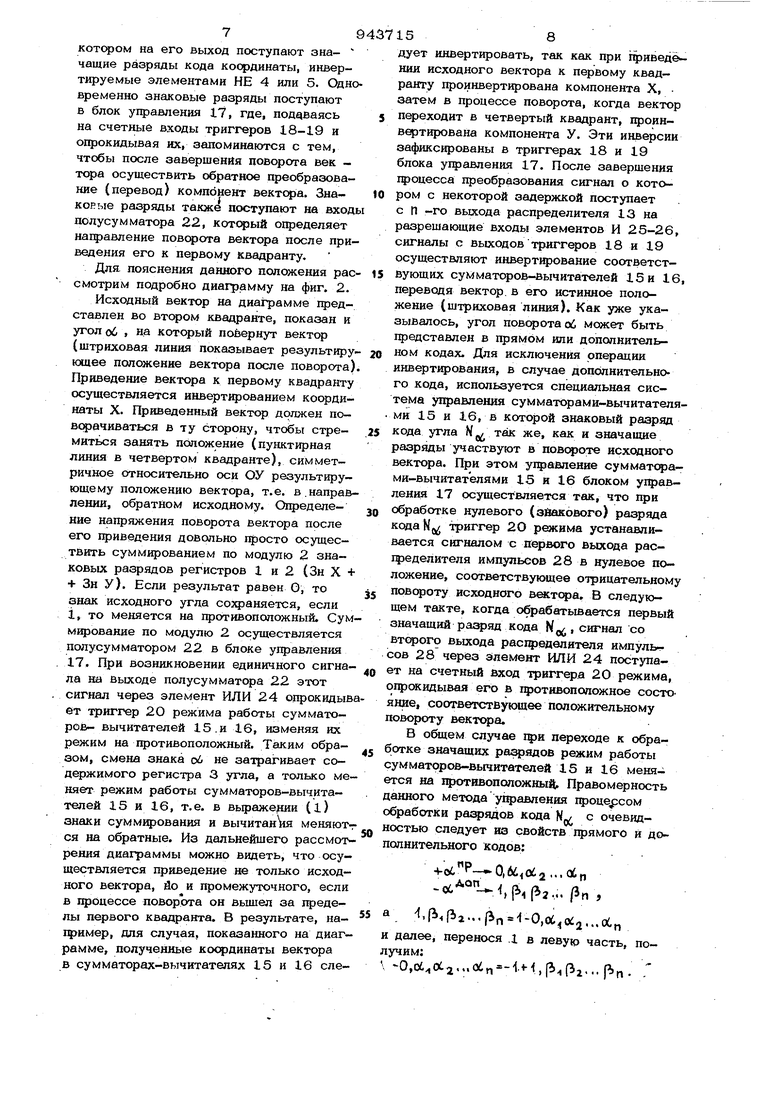

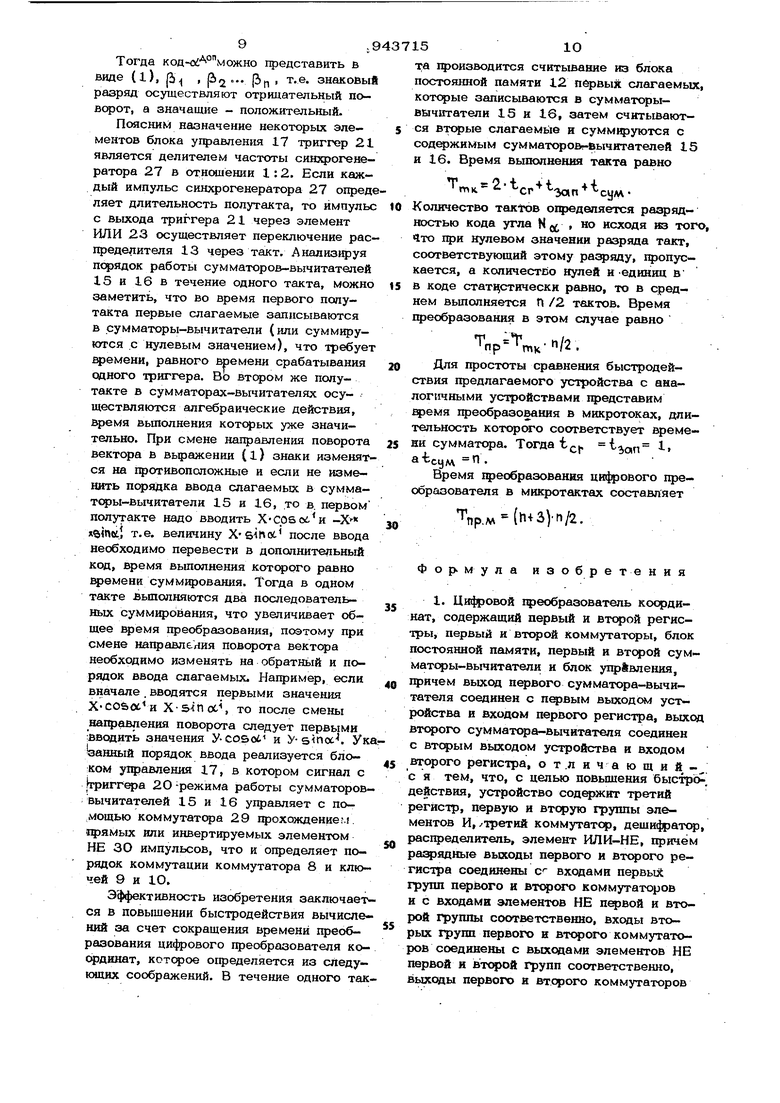

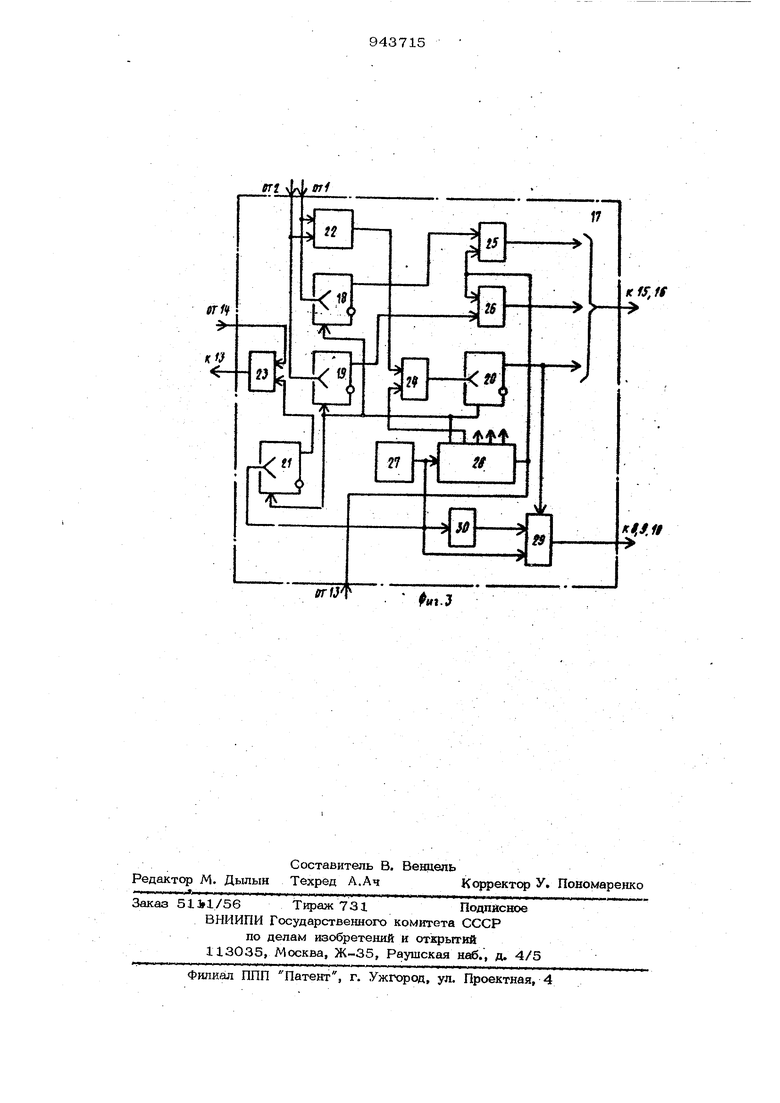

Поставленная цель достигается тем, Что в греобразовател координат, сод жаишй и регистры, первый и второй коммутаторы блок постоянной памяти, первый и второй сумматсфы-вычитатели и блок управления, причем выход сумматора,Р вычитателя соединен с первым выходом устройства и входом первого регистра, выход второго сумматора-вычитателя соединен с вторым выходом устройства и входом вторсяго регистра, дополнительJ5 IK) введены третий регистр, первая и втекая грухшы элементов И, третий коммутатор, дешифратор, расщюделитель, элемент ЙЛИ-НЕ, щзичем ра ядные Выходы нового в BTqporo регистра сое20 динены с входами первых групп первого и второго коммутаторов и с входами элементов НЕ первой я второй группы соответственно, входы вторых групп первого и втор( коммутаторов соединены 394 с выходами элементов НЕ первой и вто-. рой групп соответственно, выходы первого и второго коммутатсров соединены соответственно с первым и вторым входами групп третьего коммутатора, выход которого соединен с входом деши4ратс а, выходы которого соединены с соответств ющими входами горизонтальных шин блока постоянной памяти, первый и втсрой выходы которого соединены с входами со ответственно первой и второй групп элементов И, первые выходы которых соединены с первыми входами соответственно первого и второго сумматсроввычитателей, вторые входы которых соединены с вторыми выходами соответствен но второй и первой групп элементов И, управляющие входы которых соединены с первым выходом блока управления, второй выход Korqporo соединен с управляющими входами первого и второго сумматсроЁ-вычитателей, третий выход блока управления соединен с узравляющим. входом распределителя, выходы которого соединены с соответствующими входами вертикальных шин блока постоянной памяти и входами элемента ИЛИ-НЕ, выход . соединен с первым входом блока управления, второй вход которого со&динен с первым входом элемента ИЛИ-НЕ третий вход блока управления соединен с выходом знакового разряда первого регистра и с управляющим входом первого коммутат(5)а, вход блока управления соединен с выходом знакового разряда второго регистра и управляющим входом второго коммутатора, управляющий вход третьего коммутатора соединен с первым выходом блока управпвния, причем блок управления содержит первый, второй, третий и четвертый триггеры, полусумматор, первый и втсрой элементы ИЛИ, первый и втярой элементы И, синхрогенератср, распределитель импульсов, KOMMyTaTqp и элеме(Н1г НЕ, причем первый вход первого элемента ИЛИ соединен с первым входом блока управления, второй вход которого соединен с первым входом распределителя импульсов и первыми входами первого и втсрого элементов И, вторые входы которых соединены соответственно с выходами первого и второго триггеров, входы которых соединены соответственно с третьим и четвертым вход ми блока утфавления, первый выход рас1феделителя импульсов соединен с установочными входами первого, второго, третьего и четвертого триггеров, выход коммутатора соединен с первым выхо54дом устройства, второй выход которого соединен с выходами первого и второго элементов И, выходом третьего триггера и первым входом коммутатора, второй вход которого соединен с выходом элемента НЕ, вход которого соединен с третьим входом коммутатора, выходом сиюфогенератора и входом рас15)еделителя импульсов, второй выход которого соединен с входом второго элемента ИЛИ, втсрой вход которого съе динен с выходом полусумматора, первый и второй входы которого соединены соответственно с третьим и четвертым входами блока утфавления, третий выход которого соединен с выходом первого элемента ИЛИ, второй вход которого соединен с выходом четв ггого триггера, вход которого соединен с входом элемента НЕ, второго элемента ИЛИ соединен с входом четвертого триггера. На фиг. 1 щэиведена структурная схема устрсЛства; на фиг. 2 - диаграмма 14}иведения аекте а к первому квадрату; на фиг. 3 - структурная схема устрой ства ущ ввпеи«я. Устройство (фиг. l) содержит регистры 1,2 и 3, элементы НЕ 4 и 5, коммутаторы 6,7 и 8, группы элементов И 9 и Ю, дешифратор Ц, блок постоянной памяти 12, распределитель 13, элемент ИЛИ-НЕ 14, сумматоры-вычитатели 15 и 16 и блок у1 равле1шя 17. Структурная схема (фиг. З) бло«а ущзавления 17 содержкгг триггеры 18, 19,20 и 21 со счетными входами полусумматора 22, элементы ИЛИ 23 и 24, И 25 и 26, синхрогенератор 27, рас1Чределитель импульсов 28, коммутатор 29, элемент НЕ 30. Г инцил функиионЕ5)Ов1ания устройства основан на реализации выражений: 4 X-coSo6 y.eino6 у«у-совой+х-в по6 с использованием постоянной памяти,, в кoтqpoй апксатл значения С соБсх. C-e-in 06 , где С - значение координаты или У; « - приааак приформирования (по некотсрому адресу постоянной памяти записано слово двойной разрядности, первые П ,которого определяют значение С- cosot., а вторые ГУ разрядов С S-i П ОА); ot - значение угла, соот- ветствующее i -му разр5шу кода угла NQ. При кодировании угла в диапазоне от ,Ot 211/2, { 1,2... п. 5 Блок постоянной памяти 12 можно представить в виде прямоугольной матри цы, имеющей 2 горизонтальных шин (соответствующих всевозможным значениям координат X или У) и П вертикаль ных щин (соответствующих код угла N (1 ). На пересечении 4 -ой горизонтальной и I -ой вертикальной шин записано слово двойной разрядности; на гфимер Х- CoSoc .. Устройство работает следующим обра зом. Начальное состояние блока управлени 17 характеризуется установкой сигналом с первого выхода распределителя импуль сов 28 в нулевые положения триггеров 18,19,20 и 21. Ко динаты X, У и угол otзасылаются в регистры 1,2 и 3 соответственно, функционирование устрой ства осуществляется по тактам, каждый из которых состоит из двух полутактов. В первом полутакте кoqpдиHaтa X через коммутатор 8 подается :На вход дешифра тора 11, который деши(|рует значение X в одну из гс изонтальных шин матрицы блока постоянной памяти 12, при этом на нулевую вертикальную шину расщэедеЛитель 13 подключает нулевой разряд регистра 3. С выхода блока постоянной памяти 12 слагаемые Х-соеоС и X&ino группы элементов И 9 и Ю поступают соответственно в сумматорывычитатели 15 и 16, где эти слагаемые записываются. Во BTqjoM полутакте под воздействием сигналов из блока управления 17 8 и группы элементов И 9 и 10 переключаются во вто рые положения, при этом на вход дешифратора 11 поступает теперь координата У, а распределитель 13 продолжает оставаться в том же положении, что и в первом .полутакте. С выхода блока постоянной памяти 12 слагаемые У С09 о6° и У s-i П об через выходы групп элементов И 9 и 10 поступают на входы второго и первого сумматсроваычитателей 16 и 15, которые щу1 этом устанавливаются в соответствующи режимы суммирования или вычитания сигналом с триггера 20 блока управления 17. После завершения процессов алгебраического суммирования в сумматорахвычитателях 15 и 16 в них сфсфмируются значения X ль Уд равные Хо Х-со5о:°- -5чпо6° Уо X 5 п оС°+ -COSoC, 154j которые переписываются в регистры 1 и 2 соответственно, а сумматоры-вычятатели 15 и 16 обнуляются. Следующий такт 1фоходит аналогично 1федьщущему, причем распределнггель 13 подключает к вертикальной щнне блока постоянной памяти 12 первый разряд регистра 3. Здесь следует заметить, что в. случае подключения распределителем 13 разряда, имеющего нулевое значение, поворот вектсфа в данном такте нулевой, поэтому необходимо сразу же преходить к обработке следукм щего регистра 3. Это осуществляется автоматически с помощью логического элемента ИЛИ-НЕ 14, на выхо- ды которого поступают все выходы расщэеделнггеля 13. Если подключаемый разряд имеет нулевое значение (неподключенные выходы расЕределнтеля имеют jнулевые значения), то на выходе элемента ИЛИ-НЕ 14 возникает единичный сигнал, поступающий элемент ИЛИ 23 блока ущэавленяя 17 на управляющий вход распределителя 13, осуществляя его переключение (сдвиг) на следующий разряд регистра 3. Данная организация обработки разрядов кода угла N 0 позволяет сократить общее количество тактов 1феобразования. Учитывая, что количество единиц и нулей в коде статистически равно фуг другу, время 1феобразования сокращается в среднем вдвое. -Таким образом, в некотором такте, когда обработан последний разряд регистра 3, в сумматорах-вычитателях 15 н 16 сформ1фованы координаты повернутого вект{фа X, У. Итак описанпроцесс щюобразования координат, когда все исходные данные X, У и об хфедставпены прямыми кодами, т.е. п обраэование осуществляется только в первом кващзаегге. При расщирении зоны преобразования на всю координат ную плоскость исходные данные могут быть представлены как в гфямом, так и в дополшггельном кодах. Однако так как в блоке постоянной памяти записаны только положительные значения, то на вход деш«1ратсфа 11 следует подавать коды толысо в щзяМой фсфме, т.е. все тфеобразоваЕшя необходимо переводить в первый ква/фант. Для этого знаковые регистров I и 2 управляют коммутат чзамн 6 и 7 при единичном значении знака (дополнительный код), коммутатсчр устанавливается в положение, при , 79 на его выход поступают значащие разр5щы кода косрдинаты, инвертируемые элементами НЕ 4 или 5. Одно временно знаковые разряды поступают в блок управления 17, где, подаваясь на счетные входы триггеров 18-19 и опрокидывая их, запоминаются с тем, чтобы после завершения поворота век Tqpa осуществить обратное преобразование (перевод) компонент вектора. ЗнакоЕые разряды также поступают на вход полусумматора 22, определяет нагфавление поворота вектора после приведения его к первому квадранту. Для пояснения данного положения рас смотрим подробно диаграмму на фиг. 2. Исходный вектор на диаграмме представлен во втором квадранте, показан и угол об , на который повернут вектср (штриховая линия показывает результиру кяцее положение вектора после поворота) Приведение вектора к первому квадранту осуществляется инвертированием координаты X. Приведенный вектор должен поворачиваться в ту сторону, чтобы стремиться занять положение (пунктирная линия в четвертом квадранте), симметричное Относительно оси ОУ результирующему положению вектора, т.е. в.направ лении, обратном исходному. Определение напряжения поворота вектора после его приведения довольно щросто осуществить суммированием по модулю 2 знаковых разрядов регистров 1 и 2 (Зн X + + Зн у). Если результат равен О, то знак исходного угла сохраняется, если 1, то меняется на противоположный. Сум мирование по модулю 2 осуществляется полусумматором 22 в блоке управления 17. При возникновении единичного сигна ла на выходе полусумматора 22 этот сигнал через элемент ИЛИ 24 опрокидыв ет триггер 2О режима работы суммато ров- вычитателей 15.и 16, изменяя их режим на противоположный. Таким образом, смена знака об не затрагивает содержимого регистра 3 угла, а только ме няет режим работы сумматоров-вычитателей 15 и 16, т.е. в вьфажедии (l) знаки суммирования и вычитан ш меняют ся на обратные. Из дальнейшего рассмот рения диаграммы можно видеть, что осу ществляется приведение не только исход ного вектора, йо и промежуточного, если в процессе поворота он вышел за пределы первого квадранта. В результате, на15 имер, для случая, показанного на диаг рамме, полученные косфдинаты вектора в сумматорах-вычитателях 15 и 16 сле 158 дует инвертировать, так как при гфиведёнии исходного вектора к первому квадранту проинвертирована компонента X, затем в процессе поворота, когда вектор переходит в четвертый квадрант, проинвертирована компонента У. Эти инверсии зафиксированы в триггерах 18 и 19 блока управления 17. После завершения Щ)оцесса преобразования сигнал о котором с некоторой задержкой поступает с П -го выхода распределителя 13 на разрешающие входы элементов И 25-26, сигналы с выходов триггеров 18 и 19 осуществляют инвертирование соответствующих сумматоров-вычитателей 15 и 16, переводя вектор, в его истинное положение (штриховая линия). Как уже указывалось, угол поворота of, может быть представлен в прямом или дополнительном кодах. Для исключения операции инвертирования, в случае дополнительного кода, используется специальная система управления сумматорами-вычитателями 15 и 16, в которой знаковый разряд кода угла N так же, как и значащие разряды участвуют в повсроте исходного вектора. При этом улравление сумматярами-вычитателями 15 и 16 блоком управления 17 осуществляется так, что при обработке нулевого (зйакового) разряда кода Nj триггер 2О режима устанавливается сигналом с первого выхода расipeделителя импульсов 28 в нулевое положение, соответствующее отрицательному повороту исходного вектсра. В следующем такте, когда обрабатьюается первый значащий кода Н , сигнал со второго выхода расщэеделителя импульгсов 28 через элемент ИЛИ 24 поступает на счетный вход триггер.а 20 режима, опрокидывая его в 1фотивоположное состо яние, соответствующее положительному повороту вектора. В общем случае при. переходе к обработка значащих разрадов режим работы сумматоров-вычитателей 15 и 16 меняется на противоположны. Правомерность данного метода угфавлення проце ;сом обработки кода с очевидностью следует на свойств прямого и дополнительного кодов: 4-об Р- ОЛ ой2-0 п ,(i,(i,,. р„, а .(Ь(52...рпИ-0,...оС„ и далее, перенося .1 в левую часть, получим: -0,o6(X2...(.f,fi(bi.... . Тогда код-о ° можно гфедставить в виде (1), |5, , р Рп знаковый разряд осуществляют отрицательный поворот, а значащие - положительный. Пояскк л назначение некоторых элементов блока управления 17 триггер 21 является делителем частоты сишфогенератора 27 в отнсилёнии 1:2. Если каждый импульс синхрогенератора 27 опреде ляет длительность полутакта, то импульс с выхода триггера 21 через элемент ИЛИ 23 осуществляет переключение распределителя 13 через такт. Анализируя порядок работы сумматоров-вычитателей 15 и 16 в течение одного такта, можно заметить, что во время первого полутакта первые слагаемые записываются в сумматоры-вычитатели (или суммируются с нулевым значением), что требует времени, равного времени срабатывания одного триггера. Во втором же полутакте в сумматорах-вычитателях осуществляются алгебраические действия, время выполнения которых уже значительно. При смене направления поворота вектора в вьфажении (1} знаки изменятся на гфотивоположные и если не изменить порядка ввода слагаемых в сумматс ы-вычитатели 15 и 16, то в. первом полутакте надо вводить Х-СОйоб и -Х xsmttj т.е. величину X-sitiot после ввода необходимо перевести в дополнительный код, время выполнения которого равно времени сум м ования. Тогда в одном такте Вьшолняются два последовательных сумм1фования, что увеличивает общее время преобразования, поэтому при смене направления поворота вектора необходимо изменять на обратньгй и порядок ввода слагаемых. Например, если вначале . вводятся первыми значения Х-с05 х и X-S-tnot то после смены направления поворота следует первыми «водить значения У-cosot и У-sinoc. Ук занный порядок ввода реализуется блоком у1фавления 17, в котором сигнал с Ьригг а 20 -режима работы сумматоров вычитателей 15 и 16 управляет с помощью коммутатора 29 прохождением прямых или инвертируемых элементом НЕ 30 импульсов, что и определяет порядок коммутации коммутатора 8 и ключей 9 и 1О. Эффективность изобретения заключает ся в повышении быстродействия вычисле ний за счет сокращения времени преобразования цифрового преобразователя косрдшют, котсрое определяется из следующих соображений. В течение одного так та производится считывание из блока постоянной памяти 12 первых слагаемых, которые записываются в сумматорыВйчитатели 15 и 16, затем считываются втсрые слагаемые и суммируются с содержимым сумматоровг-вычитателей 15 и 16. Время выполнения такта равно Т -2-t +1 4 . - сг Зап сум Количество raKtoe ощюдепяется разрядностью кода угла NQ , но исходя из того, Что при нулевом значении разряда такт, соответствующий этому , пропускается, а количест 5о нулей иединиц в в коде статистически равно, то в среднем выполняется П /2 тактов. Время 14}еобразования в этом случае рбшно . Для простоты сравнения быстродействия предлагаемого устройства с аналогичными устройствами 1федставим емя преобразования в микротоках, длительность которого соответствует времени сумматора. Тогда t.,. oin 1 а-ЬсудА Время 1феобразования цифрового преобразователя в микротактах составляет Vv). мула изобретения 1. Цифровой 1феобразователь координат, содержащий первый и второй регистры, первый и второй коммутаторы, блок постоянной памяти, первый и второй сумматоры-вычитатели и блок упрйвлешш, 15)ичем выход первого сумматора-вычитателя соединен с первым выходом устройства и входом первого регистра, выход суммат ра-вычитатеяя соединен с вторым выходом устройства и входом второго регистра, о т .л и ч а ю щ и и -, с я тем, что, с целью повьпиения быстро действия, устройство содержит третий регистр, первую и вторую группы элементов И, /третий коммутатор, дещифратор, распределитель, элемент ИЛИ-НЕ, причем ра ядкые выходы первого и второго регистра соединены С входами первьиЬ групп первого и второго коммутаторов и с входами элементов НЕ первой и второй Группы соответственно, входы вторых групп первого и коммутаторов соединены с выходами элементов НЕ первой к групп соответственно, выходы первого н второго коммутаторов соединены соотйетствешю с первым и втсрым вкопамн групп третьего коммутатара, вьисоа которого соединен с входом дешиф атсфа, выходы которого соединены с первой группой выходов блока постоянной памяти, первый и второй выходы которого соединены с входами соответственно первой и групп элементов И, первые .выходы которых со€ динёны с первыми входами соответствен { но первого и второго cyMMaTqpoB-чВычитателей, вторые входы соединен с вторыми выходами соответственно вто рой и первой групп элементов И, yiqjaBляющие входы которых соединены с первым выходом блока управления, выход которого соедшюн с управляющим входами первого и суммат чюввычитателей, третий выход блока управления соединен с управляющим входом расгфеделителя, вьаоды которого соединены с второй группой входов блока постоянной памяти и входами элемента ИЛИ-НЕ, выход которого соединен с nqp вым входом блока у1д авления, второй вход которого соединен с первым входом элемента ИЛИ-НЕ, третий вход блока У1фавления соединен с выходом знакового разряда первого регистра и с утфавляющим входом первого коммутатора, четвертый вход блока утфавления соединей с. выходом знакового разряда второго регистра и удфавляющим входом второго коммутатора, управляющий вход третьего коммутатора соединен с первы вьссодом блока у1фавления. 2. Устройство по п. 1, о т л и ч а ю щ е е с я тем, что блок управления содержит первый, второй, третий и четвертый триггеры, полусумматор, первый и второй элементы ИЛИ, первый и второй элементы И, сишфогенератор, распределитель импульсов, коммутатор и элемент НЕ, причем первый вход первого элемента ИЛИ соединен с первым вх(адом блока управления, второй вход которого соединен с первым входом рас15)еделителя импульсов и первыми входами первого и втсрого элементов И, вторые входы которых соединены соответственно с выходами первого и второго триггеров, входы которых соединены соответственно с третьим и четвертым входами блока управления, первый выход распределителя, импульсов соединен с установочными входами первого, второго, третьего и четвертого триггеров, выход коммутатс а соединен с первым выходом устройства, второй выход ко- . торого соединен с выводами первого и второго элементов И, выходом третьего триггера и первым входом коммутатора, втсрой вход которого соединен с выходом элемента НЕ, вход которого соединен с третьим входом коммутатора, выходом синхрогенератора и вторым входом рас ределителя импульсов, второй выход которого соединен с первым входом втсрого элемента ИЛИ, второй вход которого соединен с выходом полусумматора, и второй входы которого соединены соответственно с третьим и четвертым входами блока управления, третий выход которого соединен с вь1ходом первого элемента ИЛИ, втсрой вход которого соединен с выходом четвертого триггера, вход которого соединен с входом элемента НЕ, выход второго элемента ИЛИ соединен с входом четвертого триггера. Источники информации, принятые во внимание при экспертизе 1.Байков В. Д., Смолов В. Б. Аппаратурная реализация элементарных функций в ЦВМ. Л., 1975. с. 71, рис. За. 2.ABTt wKoe свидетельство СССР( М 59186О, кл. Q Об F 15/20, 1978. ;(1цэототип).

OTW

К 1S,1S

иг.З

Авторы

Даты

1982-07-15—Публикация

1980-11-19—Подача