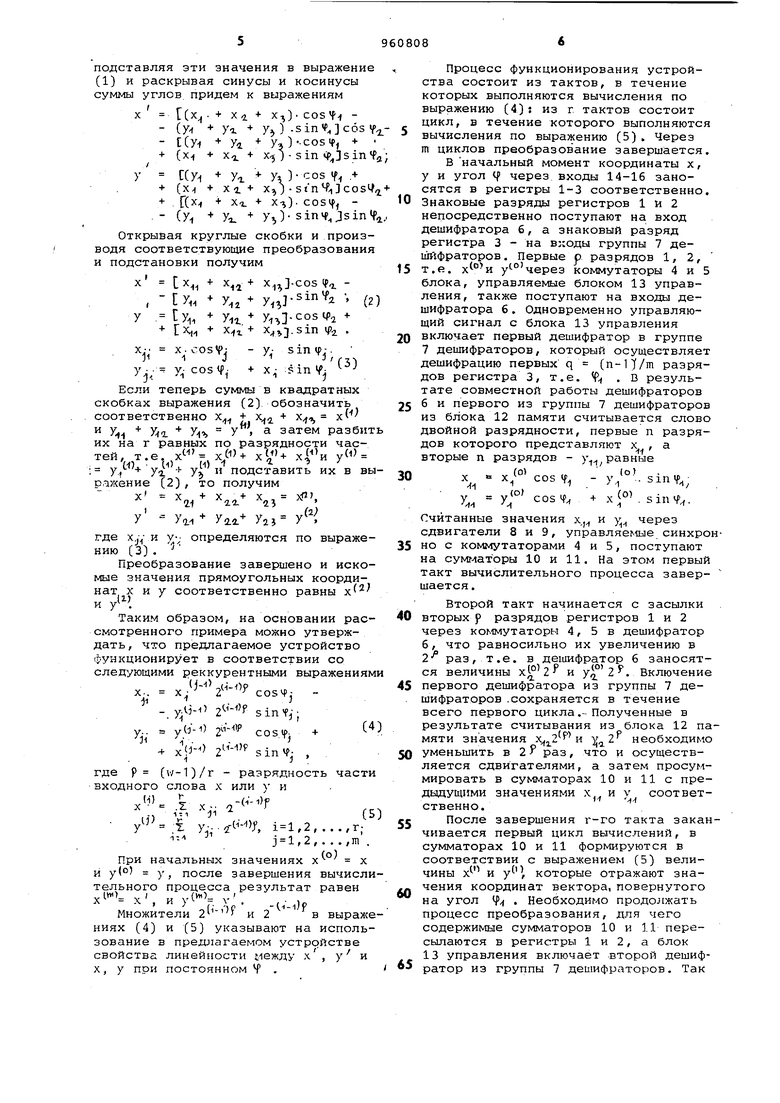

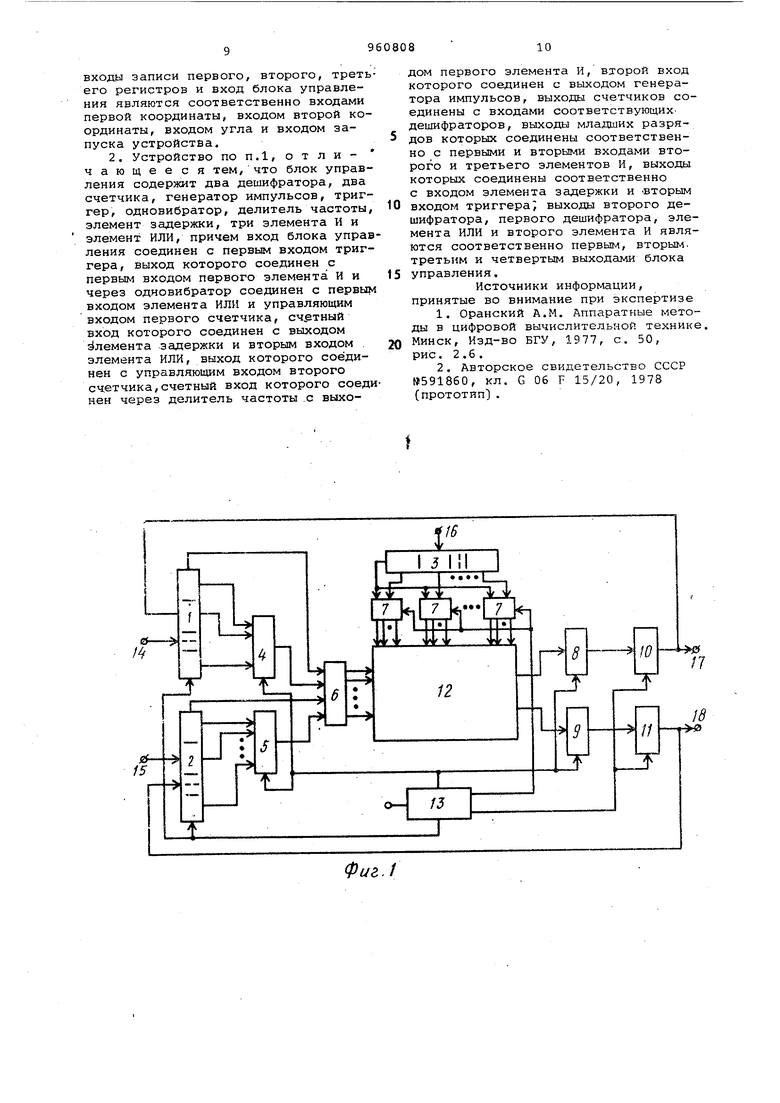

Изобретение относится к цифровой вычислительной технике и может быть использовано для аппаратурной реализации операций преобразования прямоугольных или полярных координат в системах управления роботами и манипуляторами, а также в системах навигации, наведения и т.п. Известно синусно-косинусное устройство таблично-алгоритмического типа, содержащее три блока -постоянной памяти, четыре умножителя и два сумматора. Основным содержанием этого устройства является разбиение аргумента на части, функции от которых хранятся в блоках постоянной памяти. В процессе вычисления значения функций считываются из блоков постоянной памяти и, подвергаясь в умнО жителях и сумматорах дополнительной алгоритмической обработке, приводят в конечном итоге к искомому результату Г1}. Недостатком известного устройства являются ограниченные функционал ные возможности. Наиболее близким к изобретению по технической сущнорти является устройство для вычисления значений координат вектора, содержйщее четыре сдвигающих регистра, три сумматора-вычитателя, два KONtMyTaTopa и блок постоянной памяти, причем группа выходов первого сдвигающего регистра через первый кo 1мyтaтop соединена с первым входом первого сумматора-вычитателя, группа выходов второго сдвигающего регистра через второй коммутатор подключена к первому входу второго сумматора-вычитателя, выход которого соединен с первым выходом устройства и входом первого сдвигающего регистра, выход младшего разряда которого соединен с вторым входом второго сумматора-вычитателя, выход младшего разряда второго сдвигающего регистра соединен с вторым входом первого сумматора-вычитателя, выход которого подключен к входу второго сдвигающего регистра и к второму выходу устройства. Первый вход третьего сумматора-вычитателя соединен с выходом третьего сдвигающего регистра, второй вход - с выходом четвертого сдвигающего регистра, выход подключен к третьему выходу устройства и к входу третьего сдвигающего регистра, выходы блока постоянной памяти соединены с соответствующими входами четвертого сдвигающего регистра. Первый вход элемента И подключен к входу устройства, второй вход соединен с соответствую щим выходом четвертого сдвигающего регистра, вход которого соединен с выходом элемента И. Управление процессом функционирования устройства осуществляется в блоках управления Недостатком этого устройства является низкое быстродействие. Цель изобретения - повышение быстродействия устройства. Поставленная цель достигается тем,что в устройство, содержащее три регистра, два кo лмyтaтopa, блок управления, блок памяти и два сумма тора, выходы которых соединены с вы ходами устройства и информационными входами соответственно первого и второго регистров, кодовые входы которых соединены соответственно с информационными входами первого и второго коммутаторов, дополнительно введены дешифратор, два сдвигателя и группа дешифраторов, причем входы дешифратора соединены со знаковыми выходами первого и второго регистров и выходами коммутаторов, выходы дешифратора и группы дешифраторов соединены с адресным входом блока памяти, первый и второй выходы кото рого соединены с информационными входами соответственно первого и второго сдвигателей, управляющие входы которых соединены с ервым вы ходом блока управления и управляющи ми входами кo iмyтaтopOБ, входы дешифраторов группы соединены с вторым выходом блока управления, знако вым выходом третьего регистра и выходами соответствующих разрядов третьего регистра, выходы сдвигателей соединены с информационными входами соответствующих сумматоров, управляющие входы которых соединены с третьим выходом блока управления, четвертый вход которого соединен с управляющими входами первого и второго регистров, входы записи первого, второго, третьего регистров и вход блока управления являются соот ветстйенно входами первой координаты, входом второй координаты, входом угла и входом запуска устройства. Причем блок управления содержит два Дешифратора, два счетчика, генератор импульсов, триггер, одновиб ратор, делитель частоты, элемент задержки, три элемента И и элемент ИЛИ, причем вход блока управления соединен с первым входом триггера, выход которого соединен с первым входом первого элемента И М через одновибратор соединен с первым входом элемента ИЛИ и управляющим входом первого счетчика, счетный вход которого соединен с выходом элемент задержки и вторым входом элемента ИЛИ, выход которого соединен с управляющим входом второго счетчика, счетный вход которого соединен через делитель частоты с выходом первого элемента И, второй вход которого соединен с выходом генератора импульсов, выходы счетчиков соединены с входами соответствующих дешифраторов, выходы младших разрядов которых соединены соответственно с первыми и вторыми входами второго и третьего элементов И, выходы которых соединены соответственно с входом элемента задержки и вторым входом триггера, выходы второго дешифратора, первого дешифратора, элемента ИЛИ и второго элемента И являются соответственно первым, вторым, третьим и четвертым выходами блока управления. На фиг, 1 представлена предлагаемая блок-схема устройства) на фиг. 2 - блок-схема блока управления. Цифровое устройство для вычисления координат содержит регистры 1-3 коммутаторы 4 и 5, дешифратор б, группу 7 дешифраторов, сдвигатели 8 и 9, сумматоры 10 и 11, блок 12 памяти, блок 13 управления, входы 14 и 15 координат х и у, вход 16 угла, выходы 17 и 18 координат х и у Блок 13 управления содержит триггер 19, одновибратор 20, генератор 21 импульсов, элементы И 22-24, делитель 25 частоты, счетчики 26 и 27, дешифраторы 28 и 29, элемент ИЛИ 30, элемент 31 задержки и вход 32 запуска. Определение результата пре бразования координат осуществляется в соответствии с известными выражения X. cos Ч - у S in V, y-cosM + X sin. Если коды координат х и у разбить на г равных по разрядности частей, а код угла на m частей, то исходные данные запишутся в виде X х х + У У Уг У / /и, Ч Чи 4 + . . . + Т . Подставляя эти выражения в уравнение (1) и после ряда преобразований можно прийти к реккурентным соотношениям, по которым функционирует предлагаемое устройство. Пример. . Тогда исходные данные представляются в виде - X У У У у, If У, + f г , подставляя эти значения в выражение (1) и раскрывая синусы и косинусы суммы углов придем к выражениям X (Х . + Xi + X,). COSHl -(У Уг - Xj ) -sinV Jcos -tCy-f Уг У5)--со5Ч + + (x + Xi + х ) - sin У CCy-i + Уг cos if .+ +(x-( X г - X, j stnЧ,cos +Г(х + Xo. x). cosif, -(У1 - Уо- - ,,). sin4,Jsin Открывая круглые скобки и произ водя соответствующие преобразовани и подстановки получим tx + х + x J-cos Фа , - У,, - ( У . Су,, У1г - У1: -со51р, + Х, - x.sin ф . Х-. X. COSV; - у- sin «р.-. ) y,- + ;sin V.J Если теперь суммы в квадратных скобках выражения (2) обозначить соответственно х + х. и у -ь yj + у, у , а затем разби их на г равных по разрядности частей т.е у ; у, + Уг - У ч подставить их в в ражение (2), то получим X Х, Х Х, ХП, (}.) у УН Уи Уи у где XjY и у-- определяются по выраже нию (3) . Преобразование завершено и иско мые значения прямоугольных координат X и у соответственно равны х и .. Таким образом, на основании рас смотренного примера можно утверждать, что предлагаемое устройство функционирует в соответствии со следующими реккурентными выражения X,. .,- -.У, SinVj; .. s y{o-l) .-..m 4- ( у.. S yU УЯ v ;(j-) sinV- , , где Р (v/-1)/r - разрядность част входного слова х или у и .z x. . :/ 1- ( / i У,. i l,2,...,r; j l,2,...,m При начальных значениях х ° х и у(° ), после завершения вычисл тельного процесса результат равен X ltv,i , (И,) с с -(.i-i)f Множители и 2 в выраис ниях (4) и (5) указывают на исполь зование в предлагаемом устройстве свойства линейности между х , у и X, у при постоянном V . Процесс функционирования устройства состоит из тактов, в течение которых выполняются вычисления по выражению (4): из г тактов состоит цикл, в течение которого выполняются вычисления по выражению (5). Через m циклов преобразование завершается. В начальный момент координаты х, у и угол Ч через входы 14-16 заносятся в регистры 1-3 соответственно. Знаковые разряды регистров 1 и 2 непосредственно поступают на вход дешифратора б, а знаковый разряд регистра 3 - на входы группы 7 дешифраторов. Первые р разрядов 1, 2, т.е. у°через коммутаторы 4 и 5 блока, управляемые блоком 13 управления, также поступают на входы дешифратора 6. Одновременно управляющий сигнал с блока 13 управления включает первый дешифратор в группе 7 дешифраторов, который осуществляет дешифрацию первых q (п-1)/т разрядов регистра 3, т.е. . В результате совместной работы дешифраторов б и первого из группы 7 дешифраторов из блока 12 памяти считывается слово двойной разрядности, первые п разрядов которого представляют х , а вторые п разрядов - у равные (f - у .. sinf, cos4 + х(° . . Считанные значения х,, и у через сдвигатели 8 и 9, управляемые синхронно с коммутаторами 4 и 5, поступают на сумматоры 10 и 11. На этом первый такт вычислительного процесса завершается. Второй такт начинается с засылки вторых р разрядов регистров 1 и 2 через коь1мутаторн 4, 5 в дешифратор б, что равносильно их увеличению в 2 раз, т.е. в дешифратор 6 заносятся величины и . Включение первого дешифратора из группы 7 дешифраторов .сохраняется в течение всего первого цикла.-Полученные в результате считывания из блока 12 памяти значения х,2Ри необходимо уменьшить в 2 раз, что и осуществляется сдвигателями, а затем просуммировать в сумматорах 10 и 11 с предыдущими значениями х и у соответственно. После завершения г-го такта заканчивается первый цикл вычислений, в сумматорах 10 и 11 формируются в соответствии с выражением (5) величины и , которые отражают значения координат вектора, повернутого на угол . Необходимо продолжать процесс преобразования, для чего содержимые сумматоров 10 и 11 пересылаются в регистры 1 и 2, а блок 13 управления включает второй дешифратор из группы 7 дешифраторов. Так

начинается второй цикл преобразования и осуществляется он аналогично предыдущему и т,д.

Через m циклов процесс преобразования заканчивается , в сумматорах 10 и 11 содержимые соответственно равны X и у , Эти значения через выходы 17 и 18 выводятся.

Рассмотрим работу блока 13 управления .

Первоначально исходные данные х, у и f заносятся в регистры 1-3 соответственно.

Работа устройства начинается с подачи сигнала запуска на вход 32 триггера 19, единичный сигнал с которого открывает элемент И 22, Сигнал перепада с выхода триггера 19 поступает на вход одновибратора 20, .одиночный импульс с выхода которого осуществляет сброс счетчика 27, а через элемент ИЛИ - сброс счетчика 26 и сумматоров 10 и 11. Нулевые .значения счетчиков 26 и 27 дешифрируются дешифраторами 28 и 29 в сигналы на младших выходах этих дешифраторов, которые соответственно осуществляют синхронное управление коммутаторами 4 и. 5, сдвигателями 8 и 9 и включение первого дешифратора в группе 7 дешифраторов. В первом такте сигнал с младшего выхода дешифратора 29 тактов устанавливает коммутаторы 4 и 5 в положения, в котором они подключают первые Р разрядов регистров 1 и 2 на входы дешифратора б, а сдвигатели 8 и 9 устанавливаются в положения, в ко торых они без сдвига передают считанные из блока 12 памяти значения в сумматоры 10 и 11. Сигнал с младшего выхода дешифратора 29 поступает на первый дешифратор из группы 7 дешифраторов, осуществляя дешифрацию первых q разрядов регистра 3. Начинается выполнение первого такта

Импульсы,поступающие с генератора 21 через элемент И 22 на делитель 25 частоты,определяют длительность выполнения такта.

Импульс делителя 25 частоты поступает на счетчик тактов, увеличивая его содержимое на единицу„ Содержимое счетчика 26 поступает на входдешифратора 28, в результате чегосигнал появляется на следующем выходе дешифратора, т,е. выполняется следующий вычислительный такт и После завершения г-го такта на г-ом выходе дешифратора 28 появляется сигнал, который через элемент И 24 осуществляет перезапись содержимого сумматоров 10 и 11 в регистры 1 и 2 Этот же сигнал через время, определяемое элементом 31 задержки и необходимое для полного завершения процесса перезаписи содержимых сумматоров 10 и 11 в регистры 1 и 2, поступает на вход счетчика 27, увеличивая его на единицу, а через элемент ИЛИ 30 сбрасывает счетчик 26 и сумматоры 10 и 11.

Увеличенное значение счетчика 27 поступает на вход дешифратора 29 и на его следующем выходе появляется сигнал, начиная выполнение следующего вычислительного цикла и т,д. При выполнении т-го цикла на (т-1)-ом

выходе дешифратора 29 появляется сигнал, который закрывает элемент И 24, поэтому по окончании г-го такта сигнал с г-го выхода дешифратора 28 не поступает на перезапись содержимых

сумматоров 10 и 11 в регистры 1 и 2. То есть содержимые сумматоров сохраняются, так как являются конечным результатом вычислений, в то же время этот же сигнал через элемент К 23

сбрасывает триггер 19, запрещая дальнейший процесс преобразования до ввода новых исходных данных.

Данное устройство имеет более высокое быстродействие, чем известные аналогичные устройства.

Формула изобретения

Q 1. Цифровое устройство для преобразования координатf содержащее три регистра, два ком1-/1утатора, блок . управления, блок памяти и дза cyMyiaтора, выходы которых сое.пннены с выходами устройства и информационными входами соответственно пе рвого и второго регистров, кодовые входы которых соединены соответственно с информационны «ш . входами первого и второго коммутаторов, о т л и ч а ю щ е е с я тем, что, с целью повышения быстродействия, s него введены дешифратор, два сдвигателя и группа дешифраторов, причем входы дешифратора соединены со знаковы1ди выходами

5 первого и второго регистров и выходами .коммутаторов, выходы дешифраторов и группы дешифраторов соединены с адресным входом блока памяти, пэрвый и второй выходы которого соеди0 иены с информационными входами соответственно первого и второго сдвигателей, управляющие входы которых соединены с первым выходом блока управления и управляющими входами комг у5 таторов, входы деишфраторов группы соединены с вторьа выходом блока управления, знаковым выходом третьего регистра и выходами соответствующих разрядов третьего регистра, зыходы сдвигателей соединены с информационными входами соответствчжщих сумматоров, управляющие входы которых соединены с третьим выходом блока управления, четвертый выход которого соединен с управляющими

входами первого и второго регистров.

входы записи первого, второго, третьего регистров и вход блока управления являются соответственно входами первой координаты, входом второй координаты, входом угла и входом запуска устройства.

2. Устройство ПОП.1, ОТЛИчающее ся тем, что блок управления содержит два дешифратора, два счетчика, генератор импульсов, триггер, одновибратор, делитель частоты, элемент задержки, три элемента И и элемент ИЛИ, причем вход блока управления соединен с первым входом триггера, выход которого соединен с первым входом первого элемента И и через одновибратор соединен с первым входом элемента ИЛИ и управляющим входом первого счетчикаf счетный вход которого соединен с выходом : лемента задержки и вторым входом . элемента ИЛИ, выход которого соединен с управляющим входом второго счетчика,счетный вход которого соединен через делитель частоты .с выходом первого элемента и, второй вход которого соединен с выходом генератора импульсов, выходы счетчиков соединены с входами соответствующихдешифраторов, выходы младших разрядов которых соединены соответственно с первыми и вторыми входами второго и третьего элементов И, выходы которых соединены соответственно с входом элемента задержки и вторым

0 входом триггера выходы второго дешифратора, первого дешифратора, элемента ИЛИ и второго элемента И являются соответственно первым, вторым. третьим и четвертым выходами блока

5 управления.

Источники информации, принятые во внимание при экспертизе

1.Оранский A.M. Аппаратные методы в цифровой вычислительной технике, Минск, Изд-во БГУ, 1977, с. 50,

рис. 2.6.

2.Авторское свидетельство СССР №591860, кл. G 06 F 15/20, 1978 (прототип .

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для цифрового преобразования координат | 1982 |

|

SU1019445A1 |

| Устройство для преобразования координат | 1984 |

|

SU1179324A1 |

| Устройство для преобразования координат | 1985 |

|

SU1254475A1 |

| Устройство для вычисления элементарных функций | 1983 |

|

SU1160429A1 |

| Устройство для вычисления элементарных функций | 1982 |

|

SU1141399A1 |

| Устройство для обработки приращений вектора | 1984 |

|

SU1203510A1 |

| Ассоциативный параллельный процессор | 1981 |

|

SU1166128A1 |

| Арифметическое устройство | 1978 |

|

SU687982A1 |

| Устройство для отображения информации на экране электронно-лучевой трубки | 1982 |

|

SU1053139A1 |

| Специализированный процессор для вычисления элементарных функций | 1984 |

|

SU1265764A1 |

Фиг.1

Фиг.2

Авторы

Даты

1982-09-23—Публикация

1981-02-20—Подача