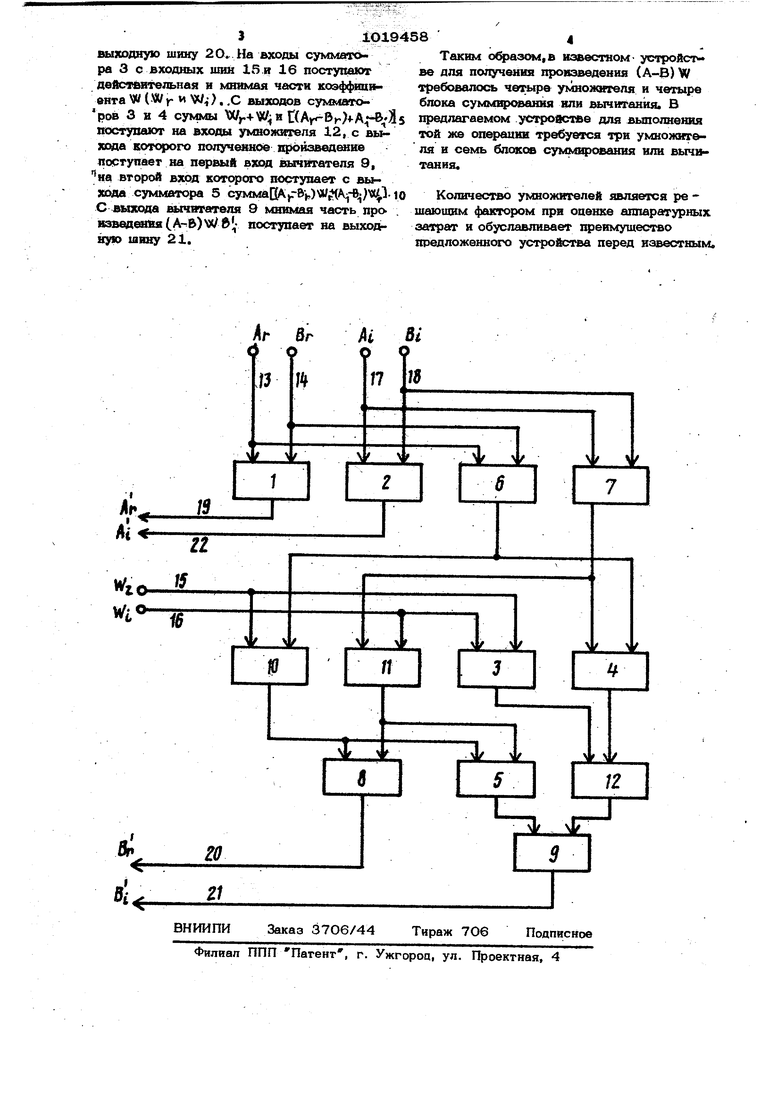

Изобретение относится к автоматике . и вычислительной технике и предназначено для аппаратурной реализации быстрого преобразования Фурье (БПФ), Известно арифметическое устройство для выполнения базовой операции БПФ, содержащее многоярусную цепь из блоков перемножения комплексных чисел, сумматоров комплексных чисел и блоков изм&нения знака комплексного числа fIj Недостатком данного устройства явпяв ся невысокое быстродействие и большое количество аппаратуры. Наиболее близким к изобретению по техшгаеской сущности является арифметвческое устройство для процессора быстро го преобразования Фурье, состоящее из трех вычитателей и четырех умножителей 2 . Недостатком известного устройства является его сложность. Целью изобретения является упрощени устройства. Поставленная цель достигается тем, что ар1и})метическое устройство для процессора быстрого преобразования Фурье, содержащее первый, второй и третий сум маторы, первый, второй и третий вычитатели, первый, второй и третий умножители, причем вход действительной части первого операнда устройства подключен к первому входу первого сумматора и к суммирующему входу первого вычитателя, вход мнимой части первого операцда ycf ройства подключен к первому входу BTopo го сумматора и к суммирующему входу второго вьгчситателя, вход действительной части второго операнда устройства подключен к второму входу первого сумматоре и к вычитающему входу первого.вычит теля, вход мнимой части второго опера да устройства подключен к второму входу второго сумматора и к вычитающему входу второго вычитателя, выходы перво го и второгч) суммат чзов являются соот ветственно выходом действительной и выходом мнимой частей суммы устройства, вход действительной части коэфф циента устройства и выход первого вьгч тателя подключены, к входам первогчэ ум ножителя, вход мнимой части коэффидиеш та устройства в выход второго вычитателя подключены к входам второго умно-жшгеля, выход первого и выход второго умножителей подключены соответственно к суммирующему и вычитающему входу третьего вьп итате,тя, выхоД которо1ЧЭ является выходом действительной результата устройства, содержит четвертый в пятый сумматоры н четвертый Ёычвтатель, причем входы действительной и мнимой частей коэффициенте устройстаа подключены к входам третье 1X3 сумматора, выходы первого и второго вычитателей подключены к входам четвертого сумматора, выходы первого и второго умножителей подключены к входам пятого cyt viaTopa, выход которого нодключен к суммирующему входу четв гого вычитателя, выходы третьего и четвертого сумматоров подключены к входам третьего умножителя, выход которого подключен к вычитающему входу четвертого вычитателя, выход четверто хэ вычитателя является вьтодом мнимой части реаульт«1та устройства. На чертеже представлена функциональная схема арифметического устройства для процессора быстрого преобразованйя Фурье. Устройство содержит сумматоры 1-5, вычтаатели 6-9, умножители 1012, входные швны 13-18, выходные шины ,19-22. Устройстэо работает следующим образом. На входы сумматора 1 и вьмитателя 6 по входным шинам 13 и 14 подаются действительные части комплексных чисел А и B{AV .и В У-), на входы сумматора 2 и вычигателя 7 по входным шинам 17 и 18 поступают мнимые, части чисел А и В С И В ) соответственно. На выходе сумматора 1 соединенного с выходной шиной 19, образуется действительная часть суммы А + В (Ау,+ БК.). На выходе сумматс а 2, соединенном с выходной шиной 22, образуется мнимая часть суммы А В ( A;J + В). С выхода ыычитателя 6 разность действителыплх частей комплексных чисел Аи В { А у,- В V-) поступает на один на входов сумматора 4 и на вход, умножитэля Ю, на другой вход которого по входной шине 15 подается дейстВ5«тельная часть коэф4ящиента y(Wr). С выхода вычитателя 7 разность мнимых частей чиселАиВ поступает на второй вход сукшатора 4 и на вхои умножителя 11, на другой вход которого по входной шине 16 поступает мнимая часть коэффициента W .С выходов умножителей 1О и 11 произведения (AyrB)Vf- и (Af- B,j )V/i поступают на входы сумматора 5 и вычитателя 6, с выхода вычитателя 8 действительная часть произведенная (А-В) W {В V ) поступает на

выходную шину 2О..На входы суммато ра 3 с входных шин 15 и 16 поступают действительная и мнимая части коэффициента W (Wt- и W). ,С JUfXoaoB сула«а(горов 3 и 4 суммы W +«/4HnA &r)A;-B.35 поступают на входы умножителя 12, с выхода которого получевноб и| 6йаведакне поступает на первый вход вычитателя 9|

второй вход которого поступает с выХО Да сумматора 5 cyMMaD frB-pW AjjHEkj V l-10 С выхода вйьгавтателя 9 мнимая часть пронаведе1Н&я()й( поступает на выходв; шину 21.

Таким офазом.в иаааестном- устройстве для получения произведения (А-В)W требовалось чечшре умнологгепя и четыре блока суколфования или вычитания. В предлагаемся устроастве для выполнения той же операции требуется три умножителя и семь блоков суммирования или вычитания.

Количество умножителей является ре шаюшим фактором при опенке аппаратурных затрат и обуславливает щ}еимушество предложенного устройства перед известным.

| название | год | авторы | номер документа |

|---|---|---|---|

| Арифметическое устройство для обработки комплексных чисел | 1984 |

|

SU1223249A1 |

| Устройство для реализации алгоритма быстрого преобразования фурье | 1975 |

|

SU607213A1 |

| Вычислительное устройство для цифровой обработки сигналов | 1985 |

|

SU1295414A1 |

| Устройство для быстрого преобразования Фурье | 1981 |

|

SU1013971A1 |

| Устройство для вычисления коэффициентов Фурье | 1982 |

|

SU1059578A1 |

| Устройство для вычисления коэффициентов-фурье | 1982 |

|

SU1049920A1 |

| Устройство для быстрого преобразования Фурье | 1984 |

|

SU1206802A1 |

| Устройство для преобразованияфуРьЕ | 1978 |

|

SU794637A1 |

| Устройство для умножения двоичных комплексных чисел | 1987 |

|

SU1424015A1 |

| Устройство для умножения комплексных чисел | 1987 |

|

SU1418707A1 |

АРИФМЕТИЧЕСКОЕ УСТРОЙСТВО ДЛЯ ПРОЦЕССОРА БЫСТРОГО ПРЕОБРАЗОВАНИЯ ФУРЬЕ, содержащее первый, второй и третий сумматоры, первый, шюрой и третий вычитатепи, первый, второй и третий умножители, причем вход действительной части первого оп&ранда устройства подключен к Первому входу первого сумматора и к суммирук щему входу первого вычитателя, вход мнимой части первого операнда устройства подключен к первому входу второго сумматора и к суммирующему входу второго вычитателя, вход действительной части второго операнда устройства подключен к второму входу первого сумматора и к вычитающему входу первого вычитателя, вход мнимой части второго операнда устройства подключен к второму входу второго сук матора и к вычитающему входу второго вычигателя, выходы первого и второго сумматоров являются соответственно выходом действительной и выходом мнимой частей суммы устройств ва, вход действительной части коэффициента устройсггва и выход первого вычитателя подключены к входам первого умножителя, вход мнимой части коэ(} фициента устройства и выход второго вычитателя подалючены к входам второго умножителя, выход первого и выход второго умножителей подключены соответственно к суммирующему и вычитающему входам третьего вычитателя, выход которого является выходом действительной части результата устройства, отлиа 9 чающееся тем, что, с целью (Л упрощения устройства, оно содержит четвертый и пятый сумматоры и четвертый вычигатель, причем входы действительной и мнимой частей коэффициента устройства подключены к входам TpieTbего сумматора, выходы первого и второ го вычитателей поключе 1ы к входам четвертого сумматора, выходы первого и . второго умножителей подключены к входам пятого сумматора, выход которого подключен к суммирующему входу четверсо тоЬо вычитателя, выходы третьего и чет 4 вертого сумматоров подключены к входам сл третьего умножителя, выход которого под00 ключен к вычитающему входу четвертого выч1Ргателя, выход четвертого вычитателя является выходом мнимой части результата устройства.

Дг вг Ai Bi

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Механический грохот | 1922 |

|

SU41A1 |

| Способ сопряжения брусьев в срубах | 1921 |

|

SU33A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Способ крашения тканей | 1922 |

|

SU62A1 |

Авторы

Даты

1983-05-23—Публикация

1982-01-06—Подача