СО

К

«

сл

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для умножения комплексных чисел | 1987 |

|

SU1418707A1 |

| Устройство для умножения комплексных чисел | 1987 |

|

SU1501044A1 |

| Вычислительное устройство для цифровой обработки сигналов | 1985 |

|

SU1295414A1 |

| Устройство для декодирования с исправлением ошибок | 1990 |

|

SU1797165A1 |

| Устройство для вычисления обратного гиперболического тангенса | 1987 |

|

SU1456952A1 |

| Устройство для выполнения быстрого преобразования Фурье | 1981 |

|

SU1020833A1 |

| Устройство для быстрого преобразования Фурье | 1988 |

|

SU1524066A1 |

| Устройство для вычисления функции @ | 1987 |

|

SU1456954A1 |

| Арифметическое устройство для быстрого преобразования Фурье | 1983 |

|

SU1149275A1 |

| Арифметическое устройство для процессора быстрого преобразования Фурье | 1982 |

|

SU1019458A1 |

Изобретение относится к цифроной вь числительной технике и может бн1ть использовано в специа/гиэиронаниых процессорах обработки цифровой информации. Целью изобретения является сокращение аппаратурных затрат. Поставленная цель достигается тем, что устройство для умножения двоичньсх кo mлeкcныx чисел, содержащее входные блоки 1, 2 сумматоров, умножители 3-5, выходной блок 11 сумматоров, дополнительно содержит умножители с соответству101 шми связями. 4 з.и. ф-лы, 5 ил.

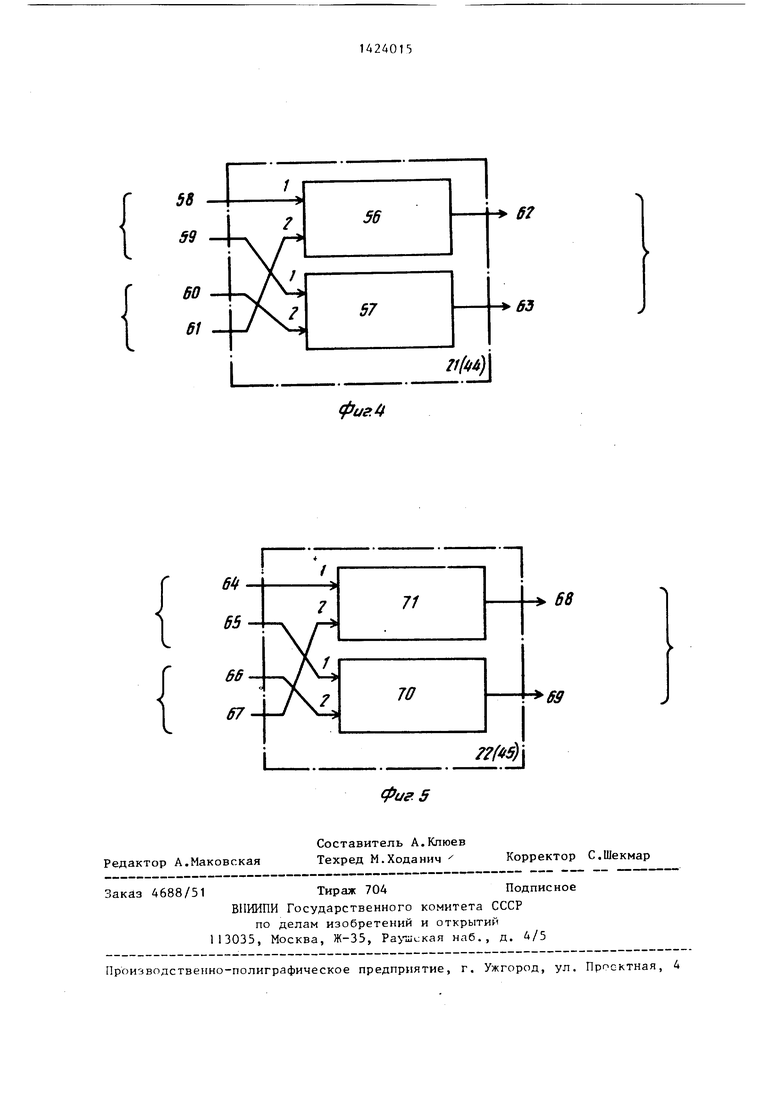

J}ue.1

Изобретение относится к Щ1фровой вычислительной технике и может быть использовано в высокопроизводительных цифровых вьпислительных процессорах, прежде всего специализированных, предназначенных для цифровой обработки сигналов.

Целью изобретения является сокращение аппаратурных затрат.

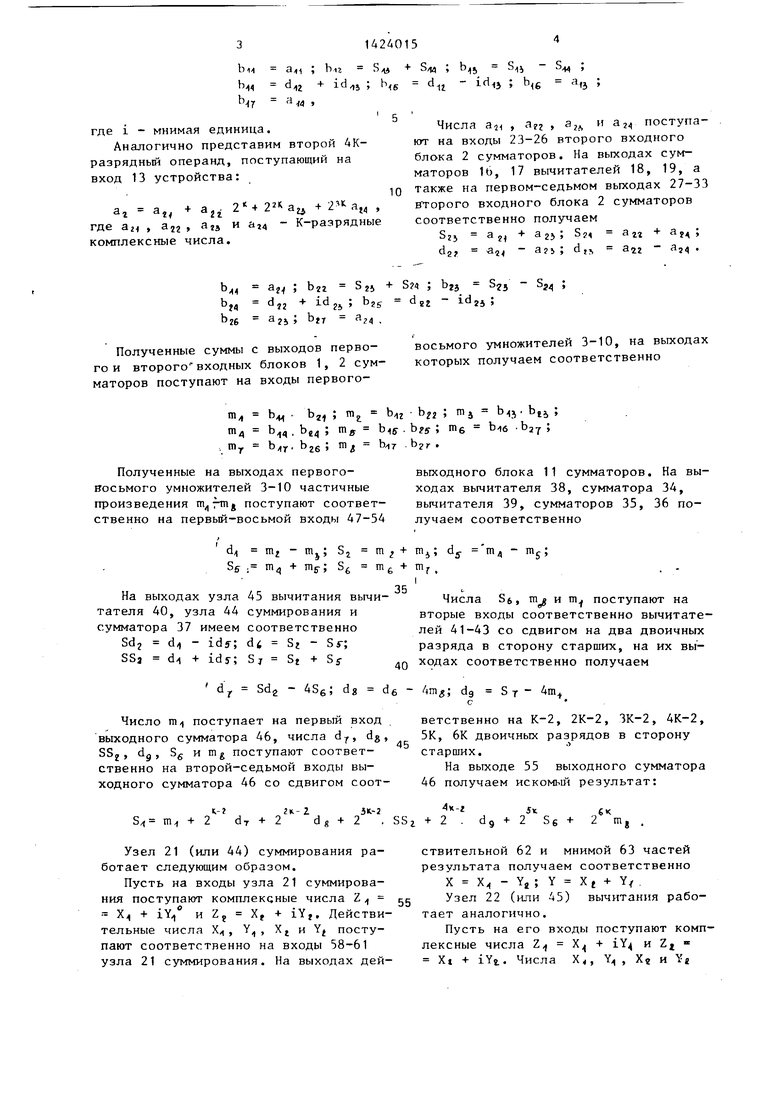

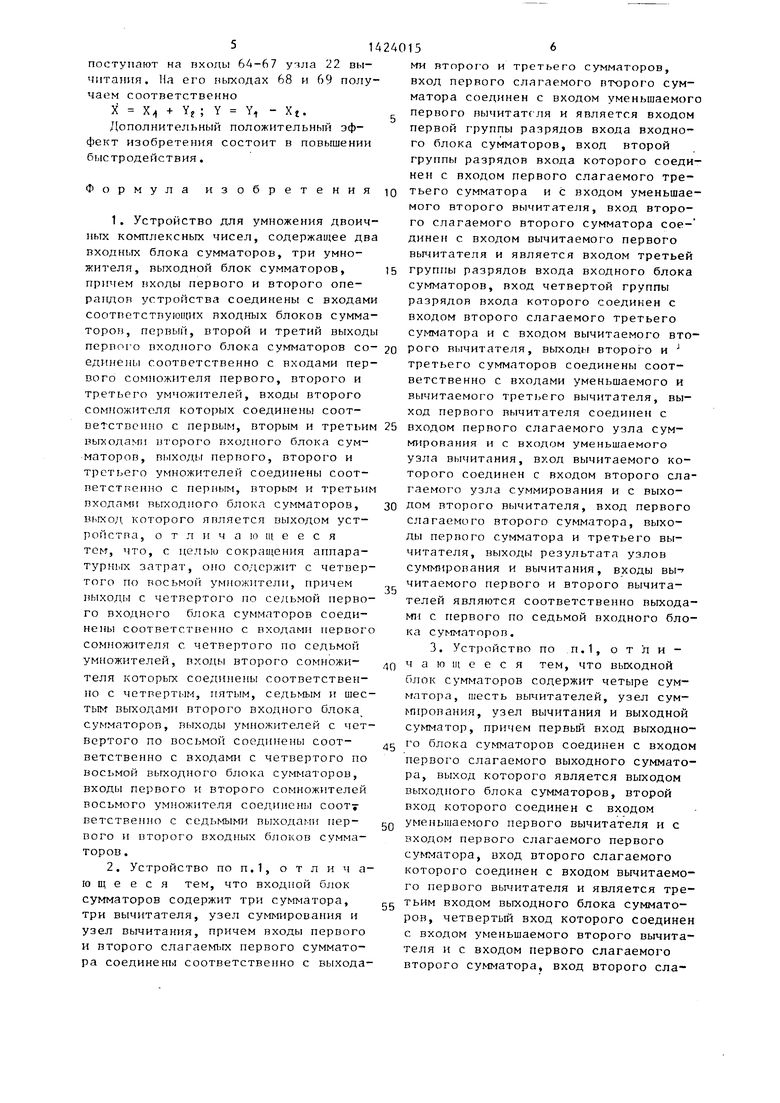

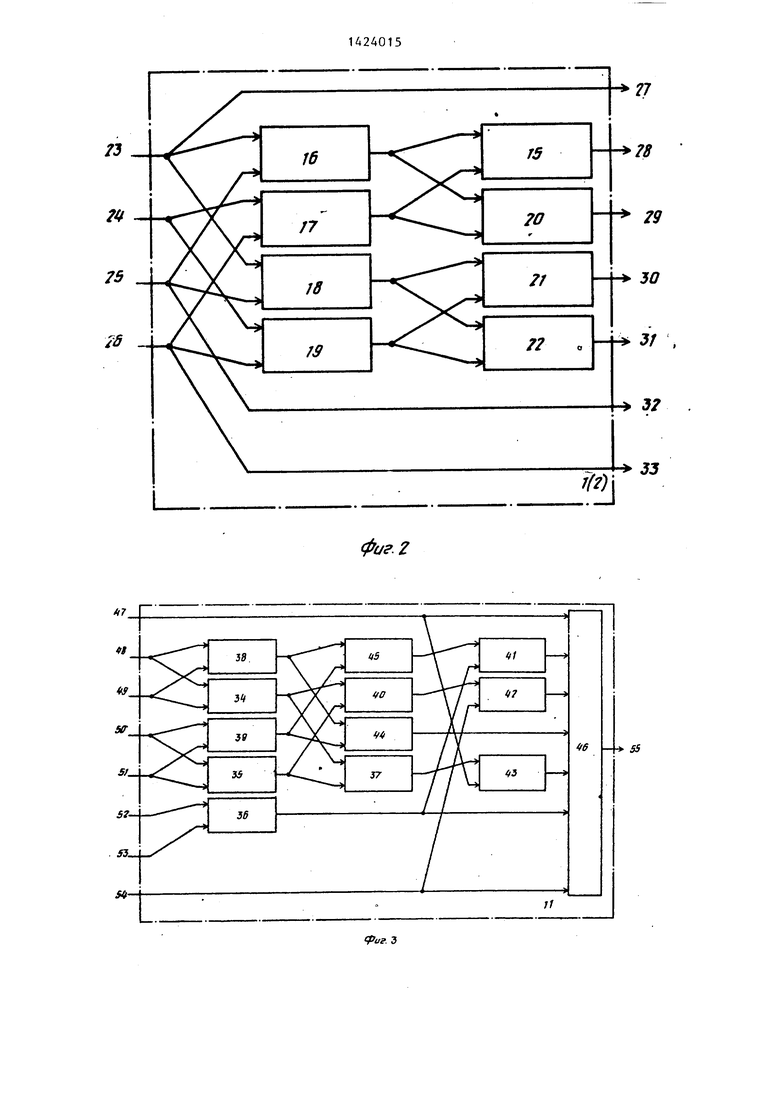

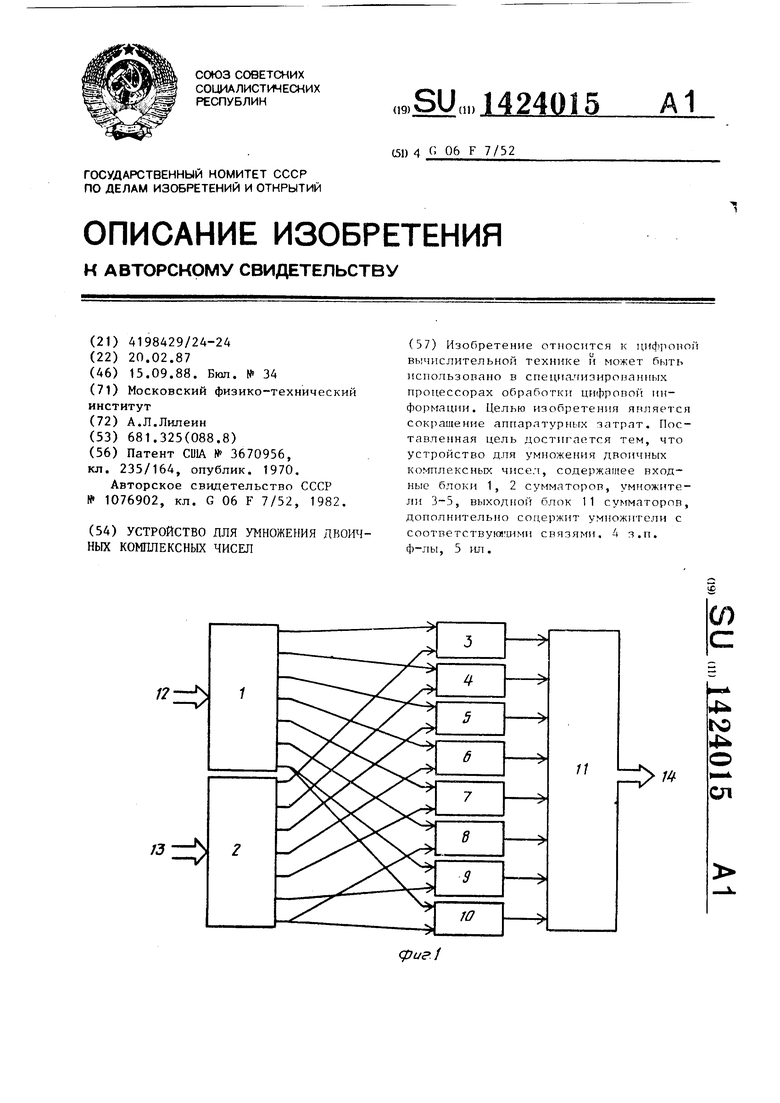

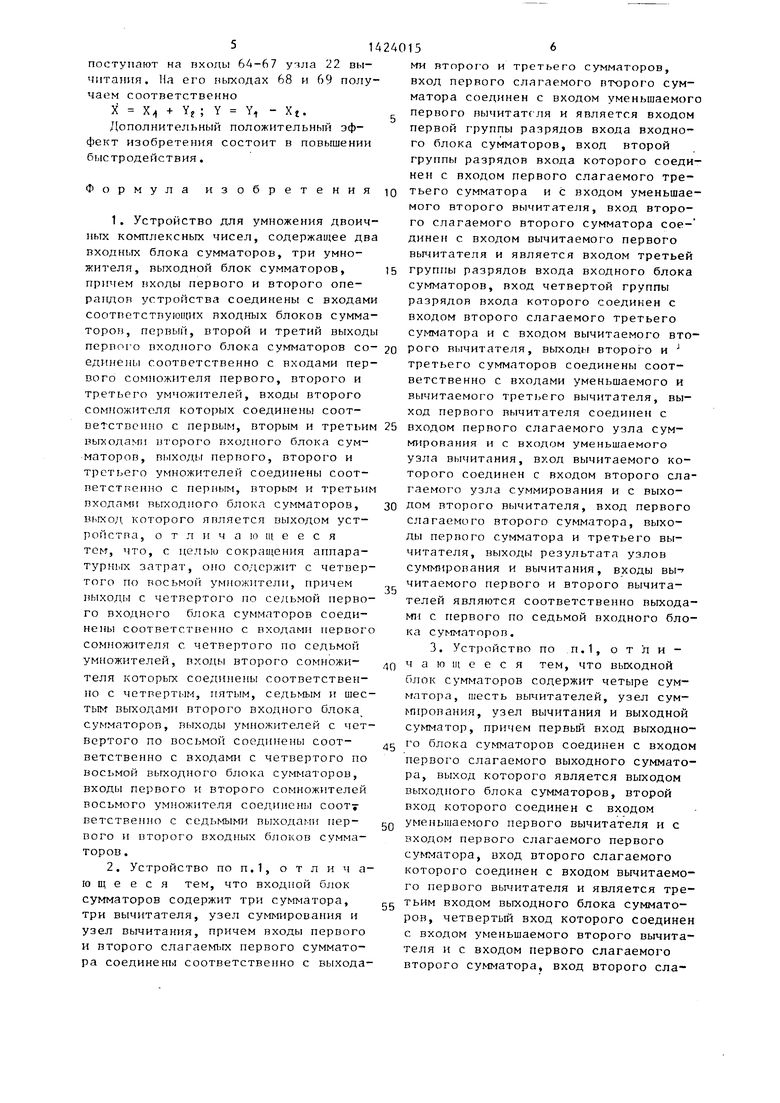

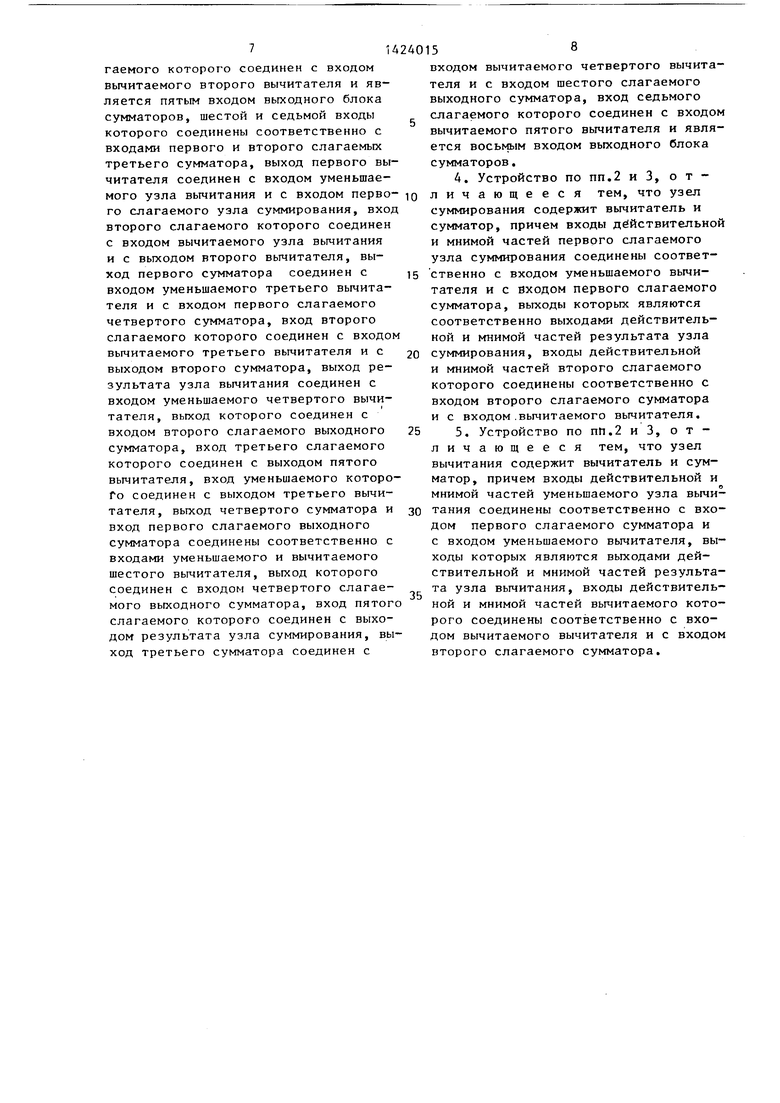

На фиг.1 приведена схема устройства для умножения двоичных комплексных чисел; на фкг.2 и 3 - схемы входного и выходного блоков сумматоров, соответственноJ на фиг.4 и 5 - схемы узлов суммт1рования и вычитания соответственно.

Устройство для умножения двоичных комп; ексных чисел (фиг.1) содержит первьй 1 и второй 2 входные блоки сумматоров, первый-восьмой умножители 3-10, выходной блок 11 сумматоров и имеет входы 12, 13 операндов и выуод 14.

Входной блок 1 (или 2) сумматоров 25 третьим, четвертым, пятым, шестым и

(фиг.2) содержит сумматоры 15-17, вычитатели 18-20, узел 21 суммирования, узел 22 вычитания и имеет входы 23-26 групп разрядов входа входного блока сумматоров, выход1 1 27-33 входного 30 блока сумматоров.

Вмходной блок 11 сумматоров (фиг .З) содержит сумматоры 34-37, вычитатели 38-43, узел 44 суммирования.

седьмым входами выходного сумматора 46 со сдвигом соответственно на N/4-2, N/2-2, 3N/4-2, N-2, 5N/4 и 6N/4 разрядов, где N - разрядность операндов. Сдвиг производится в сторону старших разрядов, младшие разря ды при этом заполняются нулями.

Первый-восьмой умножители 3-10 яв ляются умножителями комплексных чисел.

узел 45 вьмитания, выходной сумматор 46 и имеет входы 47-54 выходного блока сумматоров и выход 55 выходного блока сумматоров.

Узел 21 (или 44) суммирования (фиг.4) содержит вычитатель 56, сум- матор 57 и имеет входы 58, 59 соответственно действительной и мнимой частей первого слагаемого узла суммирования, входы 60, 61 соответственно действительной и мнимой частей вто- рого слагаемого узла суммирования, выходы 62,63 соответственно действительной и мнимой частей результата узла суммирования.

Узел 22 (или 45) вычитания (фиг.5) имеет входы 64, 65 соответственно действительной и мнимой частей уменьшаемого узла вычитания, входы 66, 67 соответственно действительной и мнимой частей вычитаемого узла вычитания, выходы 68, 69 соответственно действительной и мнимой частей результата узла вычитания и содержит пычитатель 70 и сумматор 71.

Сумматоры 15-17, 34-37, 46 (вьпш- татели 18-20, 38-43) являются сумматорами (вычитателями) комплексньк чисел, т.е. суммируют (вычитают) отдельно действительные и отдельно мнимые части чисел на их входах для образования действительной и мнимой частей результата.

Сумматоры 57, 71 и вычитатели 56, 70 выполняют действия над действительными числами.

Выходы сумматора 36, восьмого 10 и первого 3 умножителей соединены с вxoдaм вычитаемого соответственно вычитателей 41, 42 и 43 со сдвигом на два двоичных разряда в сторону старших, при этом на два младших разряда на входе вычитаемого указанных вычитателей поступает логический нуль

Выходы вычитателя 41, вычитателя 42, узла 44 суммирования, вычитателя 43, сумматора 36 и умножителя 10 соединены соответственно с вторым.

0

5

седьмым входами выходного сумматора 46 со сдвигом соответственно на N/4-2, N/2-2, 3N/4-2, N-2, 5N/4 и 6N/4 разрядов, где N - разрядность операндов. Сдвиг производится в сторону старших разрядов, младшие разряды при этом заполняются нулями.

Первый-восьмой умножители 3-10 яв ляются умножителями комплексных чисел.

Устройство для умножения двоичных комплексных чисел работает следующим образом.

а

II

iZ

« .

44

- К-разрядные комплексные числа, образованные соответственно первой, второй, третьей и четвертой четвертью разрядов 4К-разрядного первого операнда

Ч

т.е. а.

22 а.

+ ,

-f ц it 13 - М

Первый операнд поступает на вход 12 устройства, или более подробно, числа а , а li 14 поступают соответственно на входы 23, 24, 25 и 26 первого входного блока 1 сумматоров. На выходах сумматора 16, сумматора 17, вычитателя 18 и вычитателя 19 получаем соответственно

а

а.

+ аи - м

а + 3 J1 - На первом, втором, третьем, четвертом, пятом, шестом и седьмом выходах 27-33 первого входного блока 1 сумматоров получаем соответственно

а,

d«

а

; Ьп + ;

(4

где 1 - мнимая единица.

Аналогично представим второй АК- разрядный операнд, поступающий на вход 13 устройства:

а

11

+ а

гг

где 321 , ajj , ajj и комплексные числа.

а,

72

sjj ;

гг - 24

djj ; bjj

btT aj4 .

Полученные суммы с выходов первого и второго входных блоков 1, 2 сумматоров поступают на входы первого

b

-и

. b,

zi 4;

26;

i

m

m ,

Полученные на выходах первого- восьмого умножителей 3-10 частичные произведения поступают соответственно на первый-восьмой входы А7-54

m - S m + d,,- т -

m

mg-;

Sfe me +

m

r,

Ha выходах узла 45 вычитания вычитателя 40, узла 44 суммирования и сумматора 37 имеем соответственно

Sd; d - ids-; di Зг - Sr;

SSj + idy; Sj Sj

Sf

dy - Sdg - 45б; dg d - dg S т - 4m

Число га,) поступает на первый вход выходного сумматора 46, числа d, dg, SS, dg, Sg и mg поступают соответственно на второй-седьмой входы выходного сумматора 46 со сдвигом соот k-i

m + 2 dy +

ги-2 2 d

+ 2

Узел 21 (или 44) суммирования работает следующим образом.

Пусть на входы узла 21 суммирования поступают комплексные числа Z - X + iY и Zj X, -t- iY,. Действительные числа Х, , У , Xj и Yj поступают соответственно на входы 58-61 узла 21 суммирования. На выходах дей

+ S

d

11

DIS

- id

S

ii

- S,

13

44

a

«3

Числа а-ц , , , и aj

10

е

поступают на входы 23-26 второго входного блока 2 сумматоров. На выходах сумматоров 16, 17 вычитателей 18, 19, а также на первом-седьмом выходах 27-33 второго входного блока 2 сумматоров соответственно получаем

+ a

A

- aj4

восьмого умножителей 3-10, на выходах которых получаем соответственно

bxiz biff.

п ;

Ш;

; П1б -

b.

2Г

выходного блока 11 сумматоров. На выходах вычитателя 38, сумматора 34, вычитателя 39, сумматоров 35, 36 получаем соответственно

m

r,

Числа 8б, m и m поступают на вторые входы соответственно вычитателей 41-43 со сдвигом на два двоичных разряда в сторону старших, на их выходах соответственно получаем

ветственно на К-2, 2К-2, ЗК-2, 4К-2,

5К, 6К двоичных разрядов в сторону 45.

старших.

На выходе 55 выходного сумматора 46 получаем искомьш результат:

SS:

4к-л

+ 2 .

5к

+ 2 Se +

2 m I

ствительной 62 и мнимой 63 частей результата получаем соответственно X Х - Yj ; Y Хг + YI , Узел 22 (или 45) вычитания работает аналогично.

Пусть на его входы поступают комплексные числа Z Х + iY и Zj Xt + iYt. Числа Х, Y , Хе и Yj

поступают на входы 64-67 узла 22 вычитания. На его выходах 68 и 69 полу- часзм соответственно

X Х + Y Y, - Хг. Дополнительный положительный эффект изобретения состоит в повышении быстродействия.

Формула изобретения

третьего сумматоров соединены соответственно с входами уменьшаемого и вычитаемого третьего вычитателя, выход первого вычитателя соединен с

первого входного блока сумматоров со- 20 рого вычитателя, выходы второго и единены соответственно с входами первого сомножителя первого, второго и третьего умножителей, входы второго сомножителя которых соединены соответственно с nepBLiM, вторым и третьим 25 входом первого слагаемого узла сум- выходами второго входного блока сум- мирования и с входом уменьшаемого маторов, выходы первого, второго и узла вычитания, вход вычитаемого ко- третьего умножителей соединены соот- торого соединен с входом второго сла- ветстпенно с первым, вторым и третьим гаемого узла суммирования и с выхо- входами выходного блока сумматоров, ЗО Дом второго вычитателя, вход первого

слагаемого второго сумматора, выходы первого сумматора и третьего вычитателя, выходы результата узлов суммирования и вычитания, входы вы35

В(1ход которого является выходом устройства, о т л и ч а 10 щ е е с я тем, что, с целью сокращения аппаратурных затрат, оно содержит с четвертого по восьмой умножители, причем ныходы с четвертого по седьмой первого входного блока сумматоров соединены соответственно с входами первого сомножителя с четвертого по седьмой умножителей, входы второго сомножителя которых соединены соответственно с четвертым, пятым, седьмым и шее- тьм выходами второго входного блока сумматоров, выходы умножителей с четвертого по восьмой соединены соответственно с входами с четвертого по восьмой выходного блока сумматоров, входы первого и второго сомножителей восьмого умножителя соединены соотт ветственно с ceдьмы ш выходами первого и второго входных блоков сумматоров .

gQ уменьшаемого первого вычитателя и с входом первого слагаемого первого сумматора, вход второго слагаемого которого соединен с входом вычитаемого первого вычитателя и является треgg тьим входом выходного блока сумматоров, четвертый вход которого соединен с входом уменьшаемого второго вычитателя и с входом первого слагаемого второго сумматора, вход второго елами второго и третьего сумматоров, вход первого слагаемого второго сумматора соединен с входом уменьшаемого первого вычитатсля и является входом первой группы разрядов входа входного блока сумматоров, вход второй группы разрядов входа которого соединен с входом первого слагаемого третьего сумматора и с входом уменьшаемого второго вычитателя, вход второго слагаемого второго сумматора сое- динен с входом вычитаемого первого вычитателя и является входом третьей группы разрядов входа входного блока сумматоров, вход четвертой группы разрядов входа которого соединен с входом второго слагаемого третьего сумматора и с входом вычитаемого втотретьего сумматоров соединены соответственно с входами уменьшаемого и вычитаемого третьего вычитателя, выход первого вычитателя соединен с

рого вычитателя, выходы второго и входом первого слагаемого узла сум- мирования и с входом уменьшаемого узла вычитания, вход вычитаемого ко- торого соединен с входом второго сла- гаемого узла суммирования и с выхо- Дом второго вычитателя, вход первого

читаемого первого и второго вычита- телей являются соответственно выходами с первого по седьмой входного блока сум |аторов.

уменьшаемого первого вычитателя и с входом первого слагаемого первого сумматора, вход второго слагаемого которого соединен с входом вычитаемого первого вычитателя и является третьим входом выходного блока сумматоров, четвертый вход которого соединен с входом уменьшаемого второго вычитателя и с входом первого слагаемого второго сумматора, вход второго ела

гаемого которого соединен с входом вычитаемого второго вычитателя и является пятым входом выходного блока сумматоров, шестой и седьмой входы которого соединены соответственно с входами первого и второго слагаемых третьего сумматора, выход первого вычитателя соединен с входом уменьшаемого узла вычитания и с входом перво го слагаемого узла суммирования, вхо второго слагаемого которого соединен с входом вычитаемого узла вычитания и с выходом второго вычитателя, выход первого сумматора соединен с входом уменьшаемого третьего вычитателя и с входом первого слагаемого четвертого сумматора, вход второго слагаемого которого соединен с входо вычитаемого третьего вычитателя и с выходом второго сумматора, выход результата узла вычитания соединен с входом уменьшаемого четвертого вычитателя, выход которого соединен с входом второго слагаемого выходного сумматора, вход третьего слагаемого которого соединен с выходом пятого вычитателя, вход уменьшаемого которого соединен с выходом третьего вычитателя, выход четвертого сумматора и вход первого слагаемого выходного сумматора соединены соответственно с входами уменьшаемого и вычитаемого шестого вычитателя, выход которого соединен с входом четвертого слагаемого выходного сумматора, вход пятог слагаемого которого соединен с выходом результата узла суммирования, выход третьего сумматора соединен с

15

IQ240158

входом вычитаемого четвертого вычитателя и с входом шестого слагаемого выходного сумматора, вход седьмого слагаемого которого соединен с входом вычитаемого пятого вычитателя и является восьмым входом выходного блока сумматоров,

и мнимой частей второго слагаемого которого соединены соответственно с входом второго слагаемого сумматора и с входом .вычитаемого вычитателя.

с входом уменьшаемого вычитателя, выходы которых являются выходами действительной и мнимой частей результата узла вычитания, входы действительной и мнимой частей вычитаемого которого соединены соответственно с входом вычитаемого вычитателя и с входом второго слагаемого сумматора.

20

25

30

35

/J

16

П

18

75

J9

HI

7

Г5

8

70

79

J

30

72

3f .

- J7

rf7r

33

чт

фиг. 2

55

фиг

6

63

;/И|

71

- 68

70

(5)

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Упругая металлическая шина для велосипедных колес | 1921 |

|

SU235A1 |

| Кинематографический аппарат | 1923 |

|

SU1970A1 |

| Матричное устройство для умножения | 1982 |

|

SU1076902A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1988-09-15—Публикация

1987-02-20—Подача