ю

(Л

8

11

00

о |

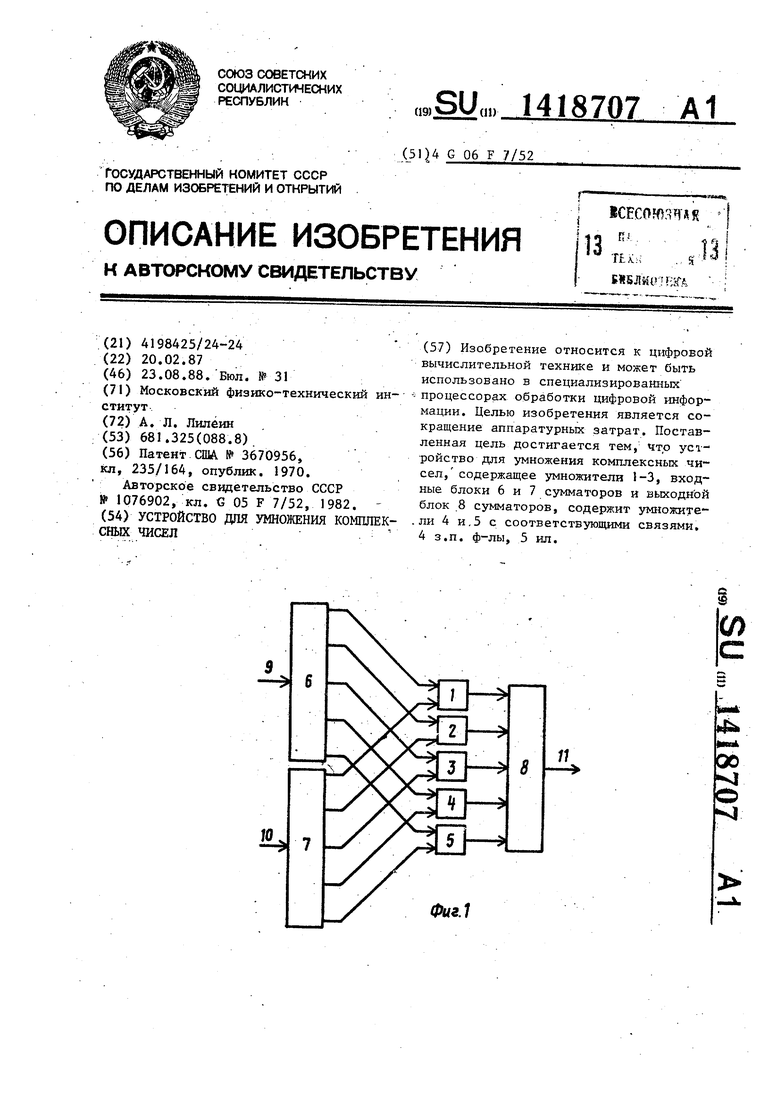

Фиг.1

Изобретение относится к цифровой :зычислительной технике и может быть :1спо льзовано в высокопроизводительных цифровых вычислительных процессорах, Ьрежде всего, специализированных, предназначенных для цифровой обработ- kn сигналов.

: Целью изобретения является сокра- |цение аппаратурных затрат,

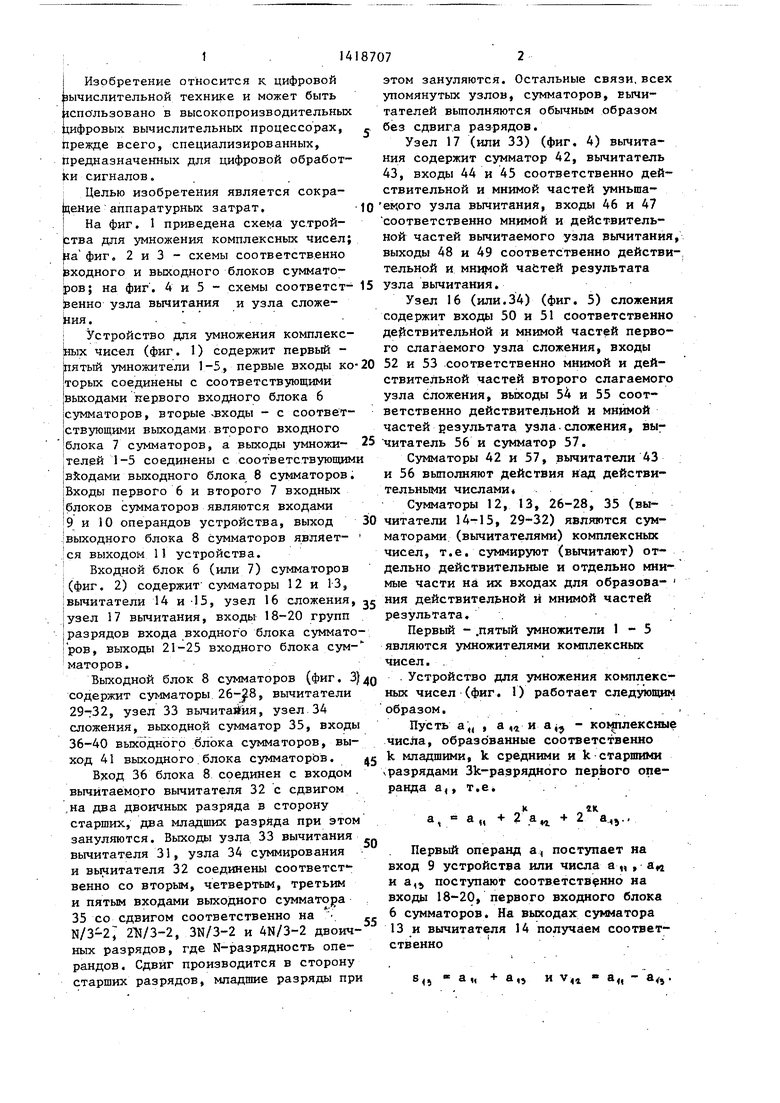

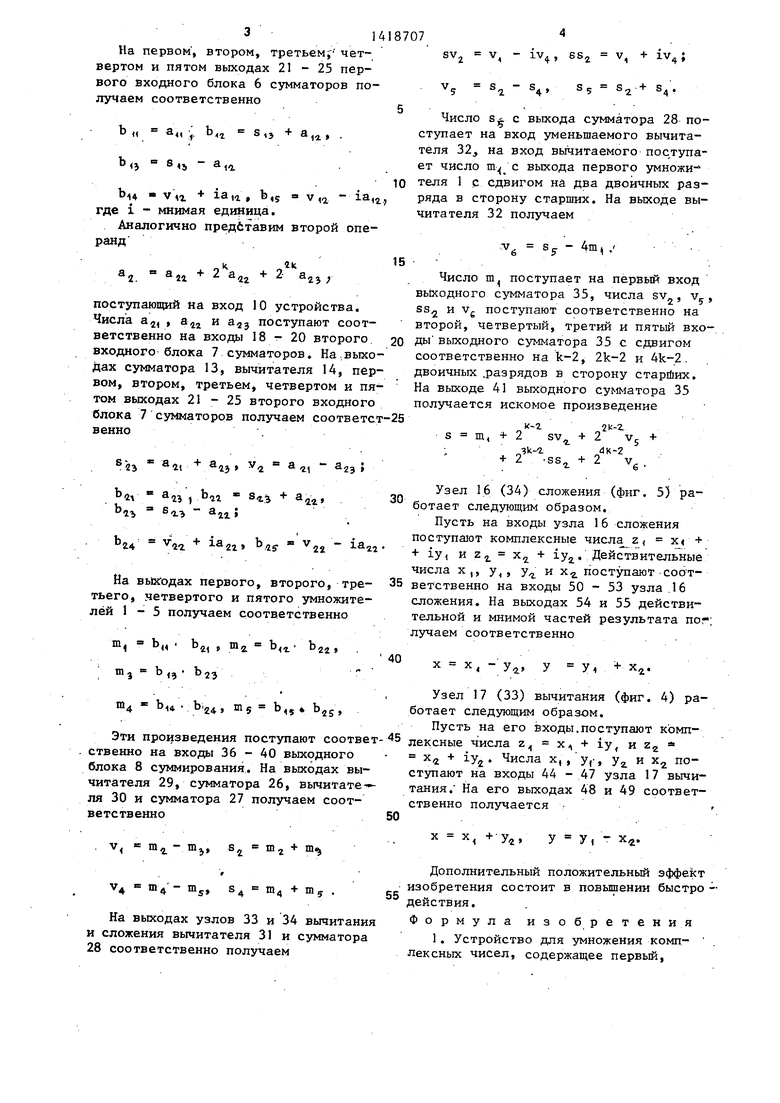

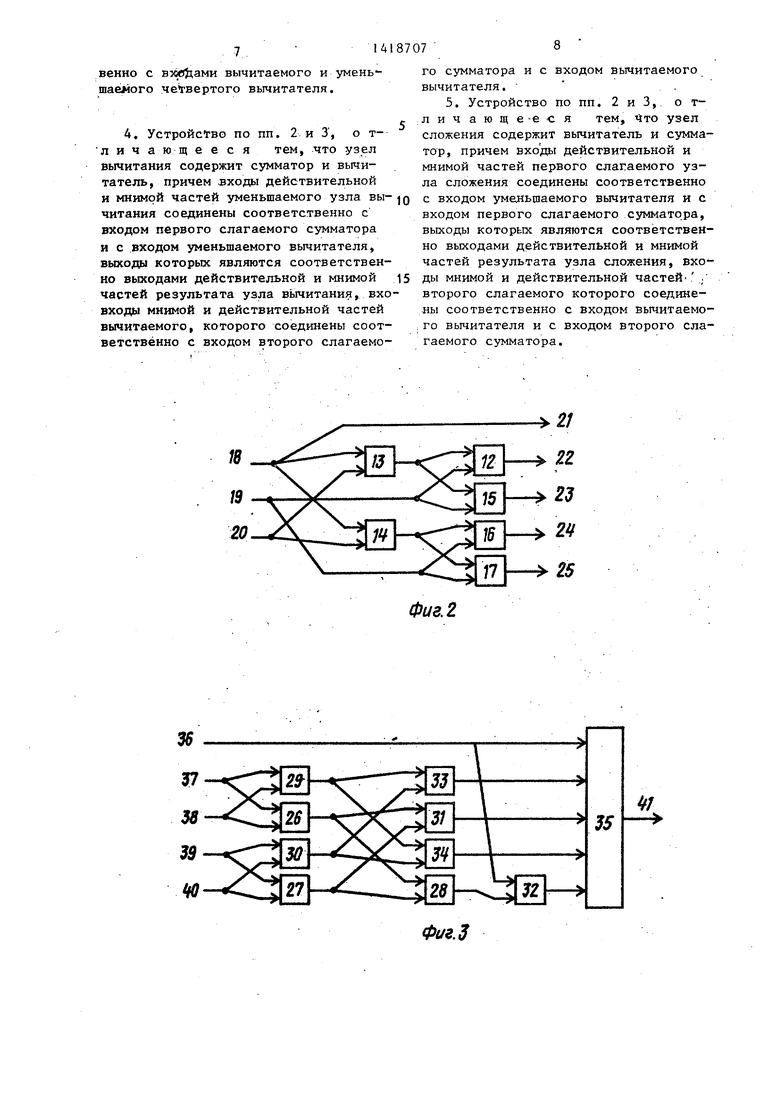

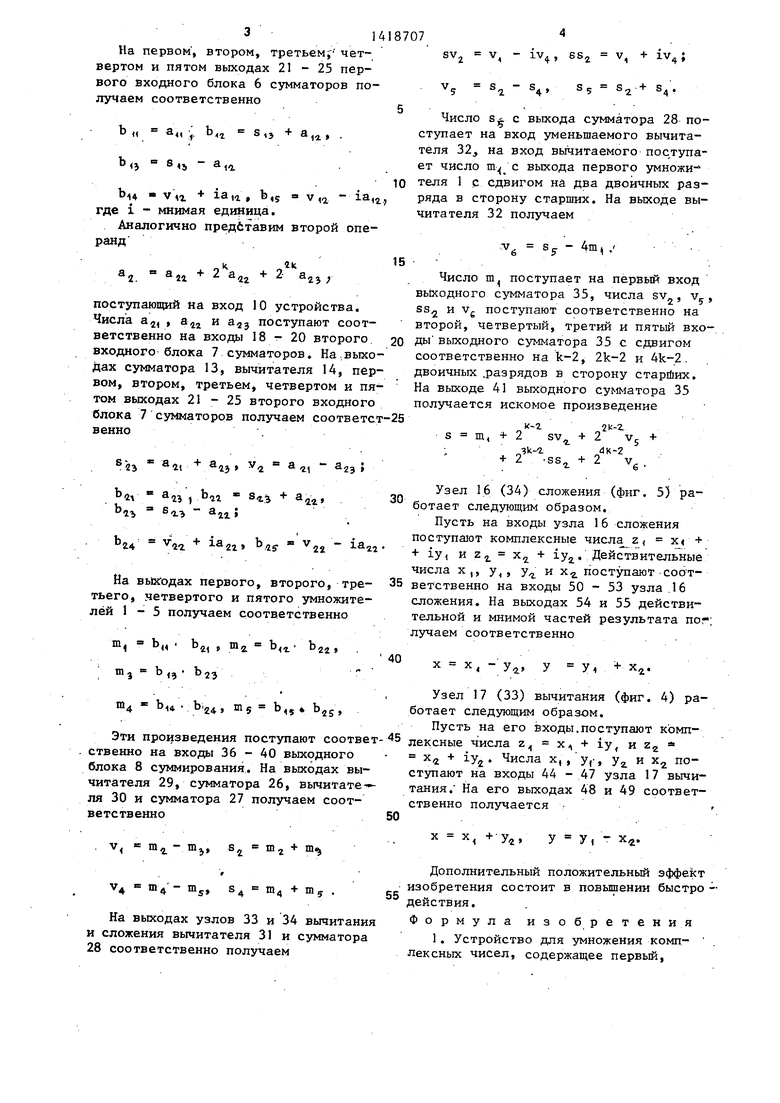

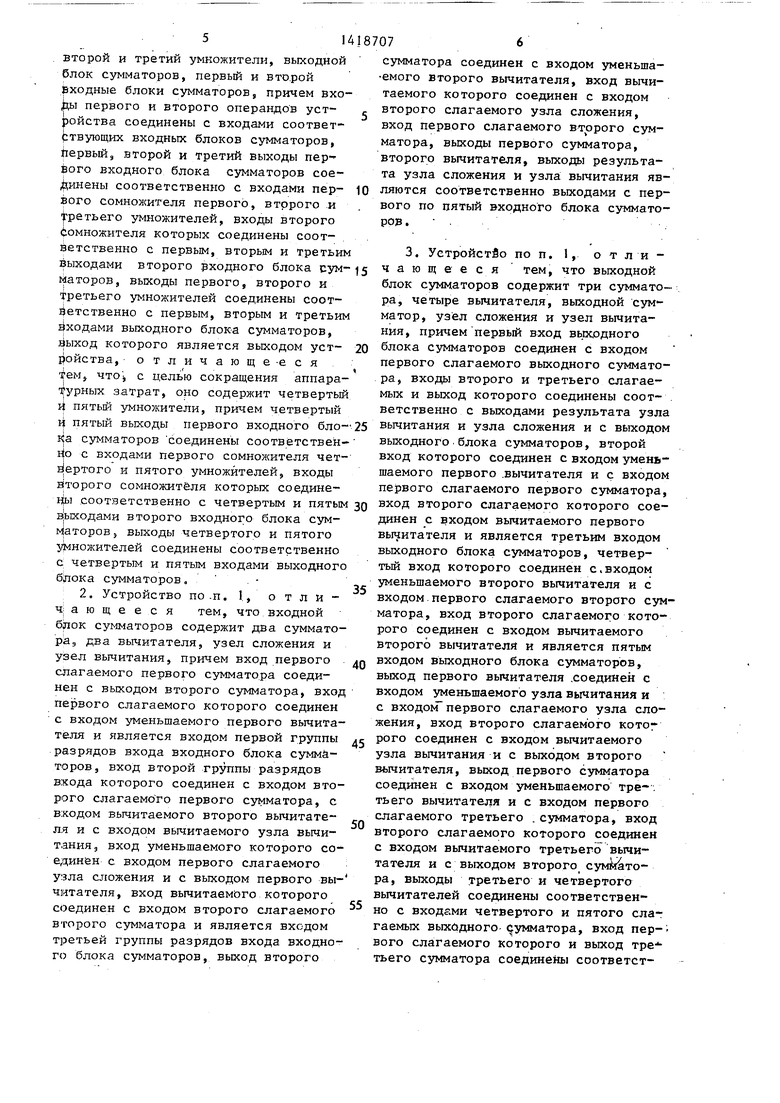

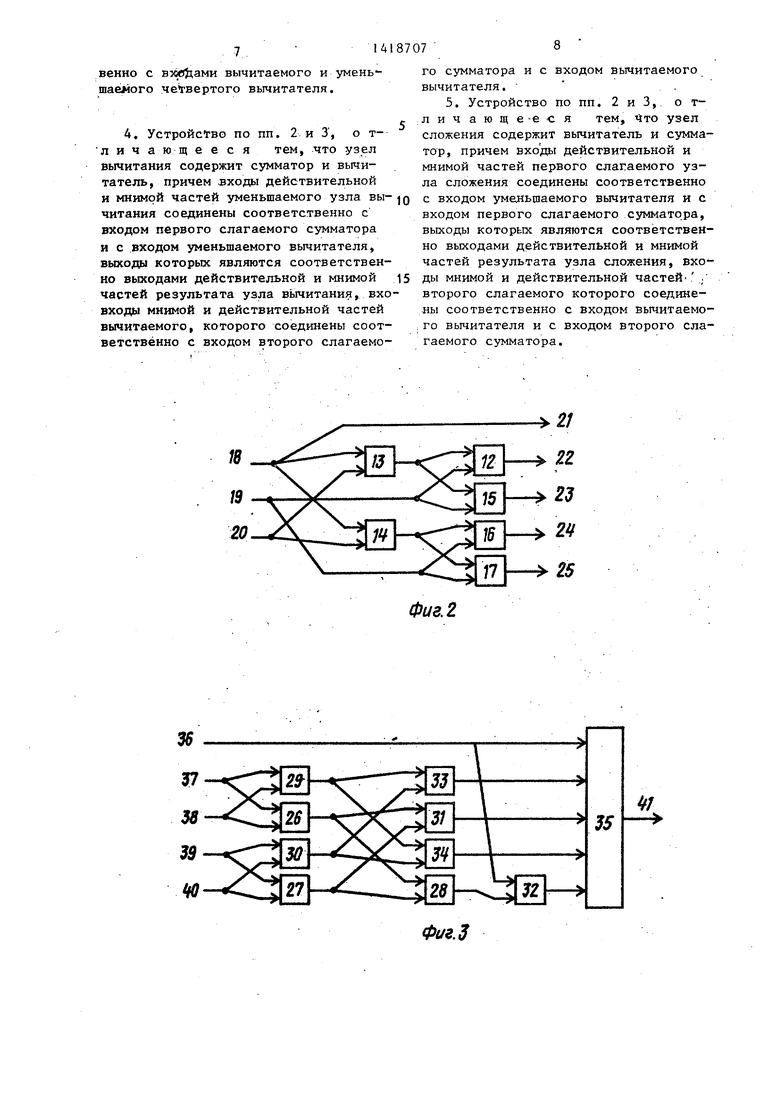

I На фиг. 1 приведена схема устрой- ртва для умножения комплексных чисел; Иа фиГо 2 и 3 - схемы соответственно входного и выходного блоков сумматоров; на фиг . 4 и 5 - схемы соответст- венно узла вычитания и узла сложе- кня, .

; Устройство для умножения комплекс- Ьых чисел (фиг. 1) содержит первый - Ьятый умножители 1-5, первые входы ко |Торых соединены с соответствующими выходами первого входного блока 6 сумматоров, вторые входы - с соответствующими выходами второго входного блока 7 сумматоров, а выходы умножи- |телей 1-5 соединены с соответствующим |вХодами выходного блока 8 сумматоров. |Входы первого 6 и второго 7 входных |блоков сумматоров являются входами i9 и 10 операндов устройства, выход |выходного блока 8 сумматоров я вляет- JcH выходом 11 устройства. ; Входной блок 6 (или 7) сумматоров ;(фиг. 2) содержит сумматоры 12 и 13, Вычитатели 14 и -15, узел 16 сложения, узел 17 вычитания, входы 18-20 групп I разрядов входа входного блока суммато IpoB, выходы 21-25 входного блока сум маторов.

Выходной блок 8 сумматоров (фиг. 3 содержит сумматоры , вычитатели 29-32, узел 33 вычитайия, узел 34 сложения, выходной сумматор 35, входы 36-40 выходного блока сумматоров, выход 41 вькодного.блока сумматоров.

Вход 36 блока 8 соединен с входом вычитаемого вычитателя 32 с сдвигом ,на два двоичных разряда в сторону старших, два младших разряда при этом зануляются. Выходы узла 33 вычитания вычитателя 31, узла 34 суммирования и вычитателя 32 соединены соответственно со вторым, четвертым, третьим и пятым входами выходного сумматора 35 со сдвигом соответственно на N/3-2; 211/3-2, 3N/3-2 и 4N/3-2 двоичных разрядов, где N-разрядность операндов. Сдвиг производится в сторону старших разрядов, младшие разряды при

этом зануляются. Остальные связи,всех упомянутых узлов, сумматоров, ЕЫЧИ- тателей выполняются обычным образом без сдвига разрядов.

Узел 17 (или 33) (фиг. 4) вычитания содержит сумматор 42, вычитатель 43, входы 44 и 45 соответственно действительной и мнимой частей умньша- емого узла вычитания, входы 46 и 47 соответственно мнимой и действительной частей вычитаемого узла вычитания выходы 48 и 49 соответственно действи тельной и чайтей результата узла вычитания,

Узел 16 (или.34) (фиг. 5) сложения содержит входы 50 и 51 соответственно действительной и мнимой частей первого слагаемого узла сложения, входы 52 и 53 соответственно мнимой и действительной частей второго слагаемого узла сложения, вьгходы 5Д и 55 соответственно действительной и мнимой частей результата узла.сложения, вы- читатель 56 и сумматор 57.

Сумматоры 42 и 57, вычитатели 43 и 56 вьшолняют действия над действительными числами

Сумматоры 12, 13, 26-28, 35 (вычитатели 14-15, 29-32) являются сумматорами (вьгаитателями) комплексных чисел, т.е. суммируют (вычитают) отдельно действительные и отдельно мнимые части на их входах для образова- НИН действительной и мнимой частей результата. .

Первый - .пятый умножители 1 - 5 являются умножителями комплексных чисел. .

Устройство для умножения комплексных чисел (фиг. 1) работает следующим образом. .

Пусть а„ , а, и а - комтлексные числа, образо ванные соответственно k младшими, k средними и k старшими чразрядами Зk-paзpяднoгo первого операнда а,, т.е .

2

«.

,,1К

+ 2 а

15

Первый операнд а, поступает на вход 9 устройства или числа а , , а и а, поступают соответственно на входы 18-20, первого входного блока 6 сумматоров. На вькодах: сумматора 13 и вычитателя 14 получаем соответственно .

+ а

tj

и V

4г

- av,

ъ3141

На первом , втором, третьем четвертом и пятом выходах 21-25 первого входного блока 6 сумматоров получаем соответственно

Ь«

8,э + а

11

5

- а

la

bi4 V г ia,a , Ь,5 v ,а ia,,, где i - мнимая единица.

Аналогично представим второй операнд

г.

aj + 2 + 2 а„

поступающий на вход 10 устройства. Числа a , а и поступают соответственно на входы 18 г- 20 второго входного блока 7 сумматоров. На.выходах сумматора 13, вычитателя 14, первом, втором, третьем, четвертом и пятом выходах 21 - 25 второго входного блока 7 су шаторов соответственно.

«3

«г, + v а, - аг, ;

8707

SVV, - IV,

ssj V, +

«1 - 4

Sc So + S

4

Число s с выхода сумматора 28 поступает на вход уменьшаемого вычитателя 32J на вход вычитаемого пос,тупа- ет число т с выхода первого умножи- теля 1 с сдвигом на два двоичных разряда в сторону старших. На выходе вычитателя 32 получаем

15

6 SF

4т

Число ш поступает на первый вход вьгходного сумматора 35, числа sv, v, ss и Vg поступают соответственно на второй, четвертый, третий и пятый вхо0 дьГ выходного сумматора 35с сдвигом соответственно на k-2, 2k-2 и 4k-2. двоичных .разрядов в сторону старйих. На выходе 41 выходного сумматора 35 получается искомое произведение

5

т, + 2

«-г

sv + 2

2k-Z

V, -Ь

3k-1 dK-2

+ 2 ss + 2 Vg

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для умножения комплексных чисел | 1987 |

|

SU1501044A1 |

| Устройство для умножения двоичных комплексных чисел | 1987 |

|

SU1424015A1 |

| Арифметическое устройство для быстрого преобразования Фурье | 1983 |

|

SU1149275A1 |

| Арифметическое устройство для обработки комплексных чисел | 1984 |

|

SU1223249A1 |

| Устройство для выполнения быстрого преобразования Фурье | 1981 |

|

SU1020833A1 |

| Арифметическое устройство для процессора быстрого преобразования Фурье | 1982 |

|

SU1019458A1 |

| Арифметическое устройство для процессоров быстрого преобразования Фурье | 1983 |

|

SU1116434A1 |

| Устройство для вычисления модуля комплексного числа | 1985 |

|

SU1259259A1 |

| Арифметическое устройство для быстрого преобразования Фурье | 1982 |

|

SU1101835A1 |

| Специализированный процессор | 1977 |

|

SU684550A1 |

Изобретение относится к цифровой вычислительной технике и может быть использовано в специализированных -i процессорах обработки цифровой информации. Целью изобретения является сокращение аппаратурных затрат. Поставленная цель достигается тем, что устройство для умножения комплексных чисел, содержащее умножители 1-3, входные блоки 6 и 7 сумматоров и выходной блок 8 сумматоров, содержит умножите.ли 4 и.5 с соответствующими связями. 4 з.п. ф-лы, 5 ил.

2л « 1 b-ii - s + а,

14

7ъ s-j. -

bz4 + 22. 22 - i

fia выхгодах первого, второго, третьего, .четвертого и пятого згмножите- лёй 1 - 5 получаем соответственно

т, Ь„ . bj, , m Ьгг, . ; ш, Ь,

104 bi24, mj b,5 bjs.

Эти произведения поступают соотве ственно на входы 36 - 40 выходного блока 8 суммирования. На выходах вычитателя 29, сумматора 26, вычитателя 30 и сумматора 27 получаем соответственно

. v т,. - mj, Sj, m + mij

v m, s m + ni5 .

Ha выходах узлов 33 и 34 вычитания и сложения вычитателя 31 и сумматора 28 соответственно получаем

30

Узел 16 (34) сложения (фиг. 5) работает следующим образом.

Пусть на входы узла 16 сложения поступают комплексные числа z х + + iy, и z. х, + 1у2, Действительные числа X,, у,, у и х поступают соот- 35 ветственно на входы 50 - 53 узла. 16 сложения. На выходах 54 и 55 действительной и мнимой частей результата nor; лучаем соответственно

40

Vi ч

45

50

Узел 17 (33) вычитания (фиг, 4) работает следующим образом.

Пусть на его входы.поступают комплексные числа ,KZ х + iy , Числа X,, у,-, у и х поступают на входы 44 - 47 узла 17 вычитания, На его выходах 48 и 49 соответственно получается

+ У2

у, - х.

55

Дополнительный положительный эффект ; изобретения состоит в повышении быстро - действия. Формула изобретен и я

5

второй и третий умкожител блок сумматоров, первый и Входные блоки сумматоров, );ы первого н второго опер

ройства соединены с входами соответ- ртвующих входных блоков сумматоров, йервый, второй и третий выходы пер Ёого входного блока сумматоров сое- инены соответственно с входами первого сомножителя первого, второго и i peTbero умножителей, входы второго Сомножителя которых соединены соответственно с первым, вторым и третьим

выходами второго рходного блока чающееся тем, что выходной

kaторов, выходы первого, второго и Третьего умножителей соединены соот- йетственно с первым, вторым и третьим ходами выходного блока сумматоров, йыход которого является выходом уст- 20

блок сумматоров содержит три суммато ра, четыре вычитателя, выходной сумматор, узел сложения и узел вычитания, причем первый вход вькрдного блока сумматоров соединен с входом первого слагаемого выходного суммато ра, входы второго и третьего слагаемых и выход которого соединены соответственно с выходами результата узл

роиства,

о тличающе-еся

тем, что ; с целью сокращения аппара- typHbnc затрат, оно содержит четвертый и пятый умножители, причем четвертый

и пятый выходы первого входного бло-25 вычитания и узла сложения и с выходом

сумматоров соединены соответствен- KJo с входами первого сомножителя чет- EJepToro и пятого умножителей, входы Второго сомножителя которых соедине1т(ы соответственно с четвертым и пятым зо второго слагаемого которого сое

В ыходами второго входного блока сум- iN aTopOBj выходы четвертого и пятого у множителей соединены соответственно с четвертым и пятым входами выходного блока сумматоров о

cjT iMaTopa соединен с входом уменьша- емого второго вычитателя, вход вычитаемого которого соединен с входом второго слагаемого узла сложения, вход первого слагаемого второго сумматора, выходы первого сумматора, второго вычитателя, выходы результата узла сложения и узла вычитания являются соответственно выходами с первого по пятый входного блока сумматоров . .

выходного.блока сумматоров, второй вход которого соединен с входом уменьшаемого первого .вычитателя и с входом первого слагаемого первого сумматора.

5

Q с

0

5

динен с входом вычитаемого первого вычитателя и является третьим входом выходного блока сумматоров, четвертый вход которого соединен с.входом уменьшаемого второго вычитателя и с входом.первого слагаемого второго сумматора, вход второго слагаемого которого соединен с входом вычитаемого второго вычитателя и является пятым входом выходного блока сумматоров, выход первого вычитателя .соединен с входом уменьшаемого узла вычитания и с входом первого слагаемого узла сложения, вход второго слагаемого котог рого соединен с входом вычитаемого узла вычитания и с выходом второго вычитателя, выход первого сумматора соединен с входом уменьшаемого тре-. тьего вычитателя и с входом первого слагаемого третьего . сумматора, вход второго слагаемого которого оединен с входом вычитаемого третьего вычитателя и с выходом второго pa, выходы третьего и четвертого вычитателей соединены соответственно с входами четвертого и пятого слагаемых выхйдного умматора, вход пер-- вого слагаемого которого и выход тре- тьего сумматора соединены соответственно с вычитаемого и уменьшаемого четвертого вычитателя.

с входом умельшаемого вычитателя и с входом первого слагаемого сумматора, выходы которых являются соответственно выходами действительной и мнимой частей результата узла сложения, входы мнимой и действительной частей .,, второго слагаемого которого соединены соответственно с входом вычитаемо- ,го вычитателя и с входом второго слагаемого сумматора.

Фиг. 2

Фиг.З

ffZ

IMIiHI

MBMi

ff3

3

Фuг,f

SO,

S2. 51

S3

Фиг.$

| Патент ОМ № 3670956, кл, 235/164, опублик | |||

| Кинематографический аппарат | 1923 |

|

SU1970A1 |

| Матричное устройство для умножения | 1982 |

|

SU1076902A1 |

| Кипятильник для воды | 1921 |

|

SU5A1 |

| Видоизменение прибора для получения стереоскопических впечатлений от двух изображений различного масштаба | 1919 |

|

SU54A1 |

Авторы

Даты

1988-08-23—Публикация

1987-02-20—Подача