транзистор 4 оказывается выбранным только по базе, и он тоже закрывается.

Затем на вход ключей блока 9 подается строб тока второго направления, который открывает дешифратором 7 один ключ блока 9, подключаюп ий группу концов адресных обмоток 3 соответствующего столбца к шине 10.

Транзистор 4 выбирается в этом случае по базе и коллектору и работает в инверсном режиме. По цепи: шина 10, открытый ключ блока 9, адресная обмотка 3, коллектор и база выбранного транзистора 4, корпус, потечет ток второго направления, длительность которого определяется длительИзобретение относится к вычислительной технике и может быть использовано при построении запоминающих устройств с линейной выборкой информации.

Цель изобретения - повышение на- 5 дежности блока.

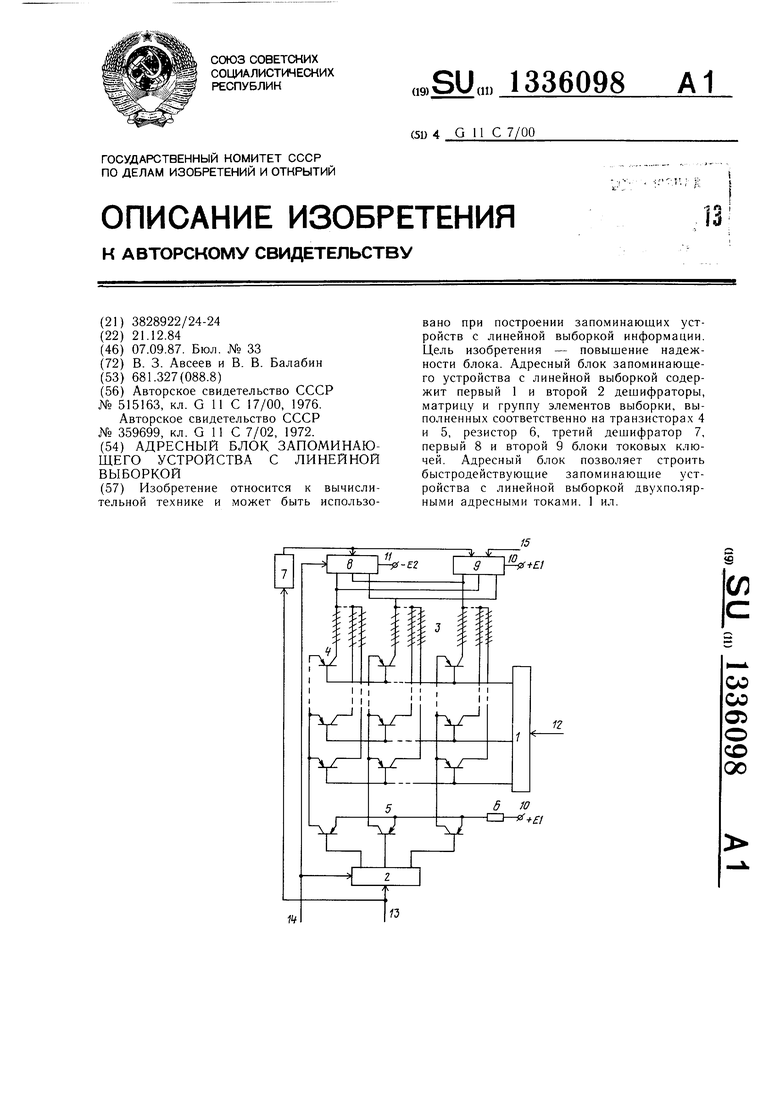

На чертеже изображена структурная схема адресного блока.

Адресный блок содержит первый 1 и второй 2 дешифраторы. Выходы адресного бло- ,„ ка подключают к адресным обмоткам 3 элементов памяти запоминающего устройства, в качестве которых могут быть выбраны биаксы. Устройство также содержит матрицу элементов выборки, выполненных на транзисторах 4, группу элементов выборки, 15 ностью строба тока второго направления, выполненных на транзисторах 5, токозадающий элемент, выполненный на резисто-Формула изобретения

ре 6, третий дешифратор 7, первый 8 и

второй 9 блоки токовых ключей.Адресный блок запоминающего устройстБлоки 9 и 8 подключены по пита-ва с линейной выборкой, содержащий пернию соответственно к щине 10 положитель- 20 вый и второй дешифраторы, входы которых ного потенциала -|- EI и к шине 11 отри-являются соответственно первым и вторым

информационными входами блока, токоза- дающий элемент, выполненный в виде резистора, матрицу элементов выборки и груп- 25 пу элементов выборки, выполненных в виде транзисторов, причем коллекторы транзисторов каждого столбца матрицы являются соответствующими выходами блока для подключения выбранных адресных об.моток, базы транзисторов каждой строки матрицы

цательного потенциала -Еа. Блок имеет первый 12 и второй 13 информационные входы, первый 14 и второй 15 стробирую- щие входы.

Адресный блок работает следующим образом.

На входы первого 1, второго 2 и третьего 7 дешифраторов поступает код адреса. Срабатывает дешифратор 1 и на одном из

его выходов появляется потенциал, близкий ЗО объединены и подключены к соответствующему выходу первого дешифратора, эмиттеры транзисторов каждого столбца матрицы объединены и соединены с коллектором соответствующего транзистора группы, базы транзисторов группы подключены к соответ- Затем на входы дешифратора 2 и ключи 35 ствующим выходам второго дешифратора, блока 8 подается строб тока первого на-отличающийся тем, что, с целью повышения

правления, по которому возбуждается одиннадежности блока, в него введены третий

из выходов дещифратора 2 и выбираетдешифратор и первый и второй блоки тосоответствующий транзистор 5, который . ковых ключей, причем вход третьего дешиф- выбирает соответствующий столбец транзис-ратора соединен с вторым информационным

торов 4, а также этот строб открываетвходом блока, выходы третьего дешифратора соединены соответственно с одноименными входами выборки первого и второго блоков токовых ключей, управляющие входы которых являются соответственно первы.м и

к корпусу, тем самым осуществляется выборка по базе одной из строк транзисторов 4. Срабатывает также дешифратор 7, который разрешает выборку одного из ключей блоков 8 и 9.

выбранный ключ блока 8. Таким образом, выбирается по базе и эмиттеру один транзистор 4, находящийся на пересечении выбранного столбца и выбранной строки.

а группа концов адресных обмоток 3 в д вторым стробируюшими входами блока, вхо- этом столбце через открытый ключ блока 8 подключается к шине 11. По цепи: шина 10, резистор 6, выбранный транзистор 5, выбранный транзистор 4, адресная обмотка 3, вь бранный ключ блока 8, шина 11, потечет адресный ток первого направления, 50 щими выходами блока для подключения

ды питания второго и первого блоков токовых ключей соединены соответственно с шиной положительного и шиной отрицательного потенциалов блока, выходы блоков токовых ключей являются соответствуювыбранных групп адресных обмоток, эмиттеры транзисторов группы через резистор соединены с шиной положительного потенциала блока. Составитель В. Рудаков

Техред И. ВересКорректор Л. Натай

Тираж 589Подписное

ВНИИПИ Государственного комитета СССР поделай нзобретени1°1 и открытий

1 13035, Москва, Ж -35, Раушская наб., д. 4/5 Производствеиио-полиграфическоо предприятие, г. Уи город, ул. Проектная, 4

длительность которого определяется длительностью строба тока первого направления. По окончании этого строба закрываются все транзисторы 5 и все ключи блока 8,

Редактор Н. Бобкова Заказ 3809/49

транзистор 4 оказывается выбранным только по базе, и он тоже закрывается.

Затем на вход ключей блока 9 подается строб тока второго направления, который открывает дешифратором 7 один ключ блока 9, подключаюп ий группу концов адресных обмоток 3 соответствующего столбца к шине 10.

Транзистор 4 выбирается в этом случае по базе и коллектору и работает в инверсном режиме. По цепи: шина 10, открытый ключ блока 9, адресная обмотка 3, коллектор и база выбранного транзистора 4, корпус, потечет ток второго направления, длительность которого определяется длительностью строба тока второго направления,

вторым стробируюшими входами блока, вхо- щими выходами блока для подключения

ды питания второго и первого блоков токовых ключей соединены соответственно с шиной положительного и шиной отрицательного потенциалов блока, выходы блоков токовых ключей являются соответствую

| название | год | авторы | номер документа |

|---|---|---|---|

| Запоминающее устройство | 1976 |

|

SU690564A1 |

| Блок адресной выборки для запоминающего устройства | 1980 |

|

SU982083A1 |

| Запоминающее устройство (его варианты) | 1983 |

|

SU1133621A1 |

| Трансформаторное постоянное запоминающее устройство | 1985 |

|

SU1310901A2 |

| Резервированное запоминающее устройство с самоконтролем | 1982 |

|

SU1070609A1 |

| Адресная система постоянногозАпОМиНАющЕгО уСТРОйСТВА СлиНЕйНОй ВыбОРКОй | 1978 |

|

SU796911A2 |

| МНОГОПОЗИЦИОННАЯ МАТРИЦА УПРАВЛЕНИЯ | 1972 |

|

SU337818A1 |

| Адресная система постоянного запоминающего устройства с линейной выборкой | 1982 |

|

SU1067532A2 |

| Постоянное запоминающее устройство | 1982 |

|

SU1112411A1 |

| Оперативное запоминающее устройство | 1979 |

|

SU903972A1 |

Изобретение относится к вычислительной технике и может быть использовано при построении запоминающих устройств с линейной выборкой информации. Цель изобретения - повышение надежности блока. Адресный блок запоминающего устройства с линейной выборкой содержит первый 1 и второй 2 дешифраторы, матрицу и группу элементов выборки, выполненных соответственно на транзисторах 4 и 5, резистор 6, третий дешифратор 7, первый 8 и второй 9 блоки токовых ключей. Адресный блок позволяет строить быстродействующие запоминающие устройства с линейной выборкой двухполяр- ными адресными токами. 1 ил. S сл СО со о: о (Х 00 S Ю

| Постоянное запоминающее устройство | 1975 |

|

SU515163A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

| 0 |

|

SU359699A1 | |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

Авторы

Даты

1987-09-07—Публикация

1984-12-21—Подача