Изобретение-относится к вычис.лит ельной .технике и предназначено для умножения чисел, представленных многоразр;ядными двоячн амм параллельными кодами.

Известно устройство для умножения на два разряда множителя, содержащее регистр мнржимого, регистр множителя, группу элементов и, сумматор, схему управления умножением на два разряда 1.

Наиболее близким к предлагаемому является устройство для умножения, содержащее регистр множимого, регистр множителя, сумматор, три элемента И и блок таблицы умножения, первый и второй входы которого соединены. с выходами двух младших разрядов регистра множителя, а первый, второй и .третий выходы блока та:блицы умножения соединены соответственно с . перзымк входами первого, второго и третьего элементов И,- вторые входы которых подключены к выходам регистра множимого , а выходы элементов И подключены к информационному входу сумматора 2.

Однако в известных устройствах для умножения невозможно умножать одновременно на два разряда множите

ля числа, представленные в виде мнегоразрядньх параллельных золотых кодов.

Целью изобретения является расширение функциональных возможностей и повышение контролеспособности устройства за счет выполнения операции умножения золотых кодов.

Поставленная цель достигается

10 тем, что устройство для умножения, содержащее регистр множимого, регистр множителя, сумматор, три группы элементов И и блок таблицы умножения, первый и второй входы которо15го соединены с выходами дзух младших разрядов регистра множители, а первый, второй и третий выходы блока таблицы умножения соединены соответственно с первыми входами первой,

20 второй и третьей, группы элементов И, вторые входы которых подключены к выходам регистров множимого, а выходы групп элементов И подключены к информационному входу сумматора,

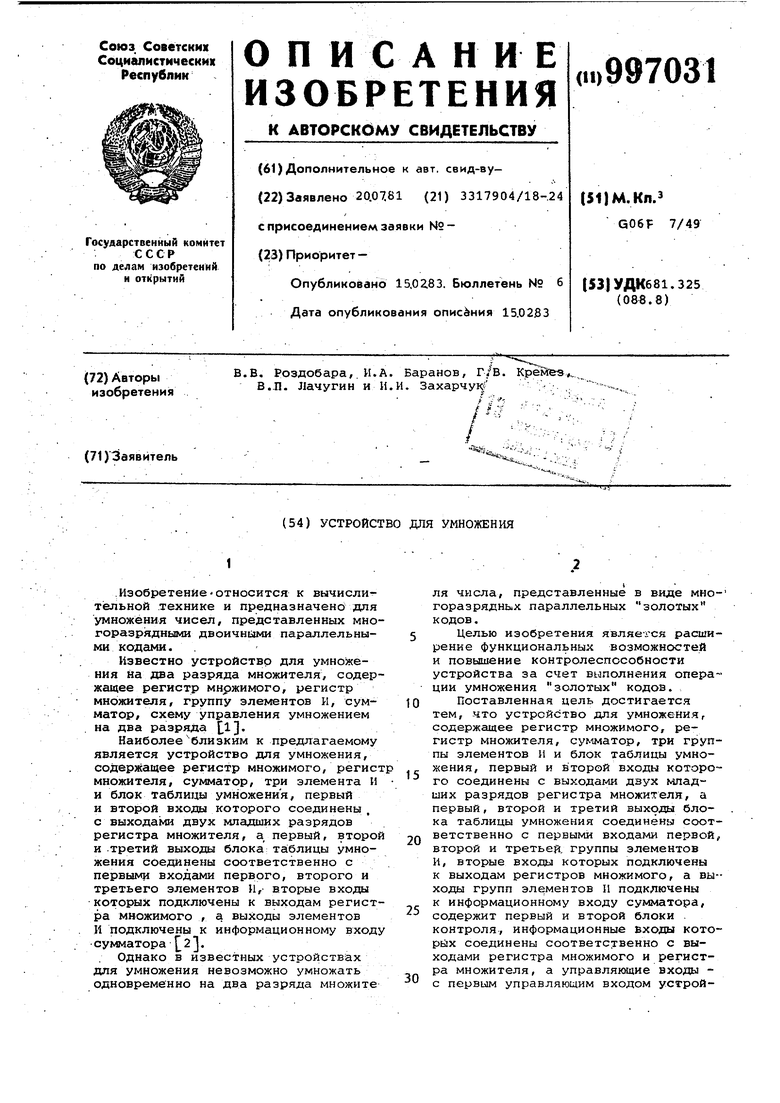

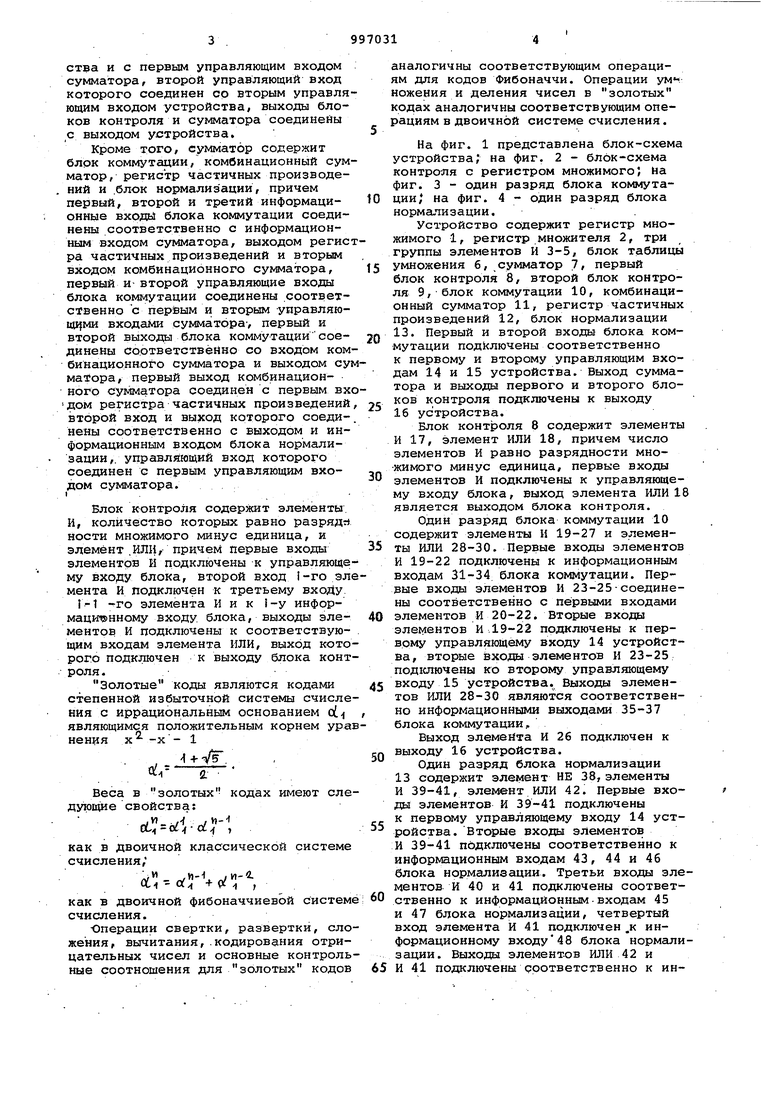

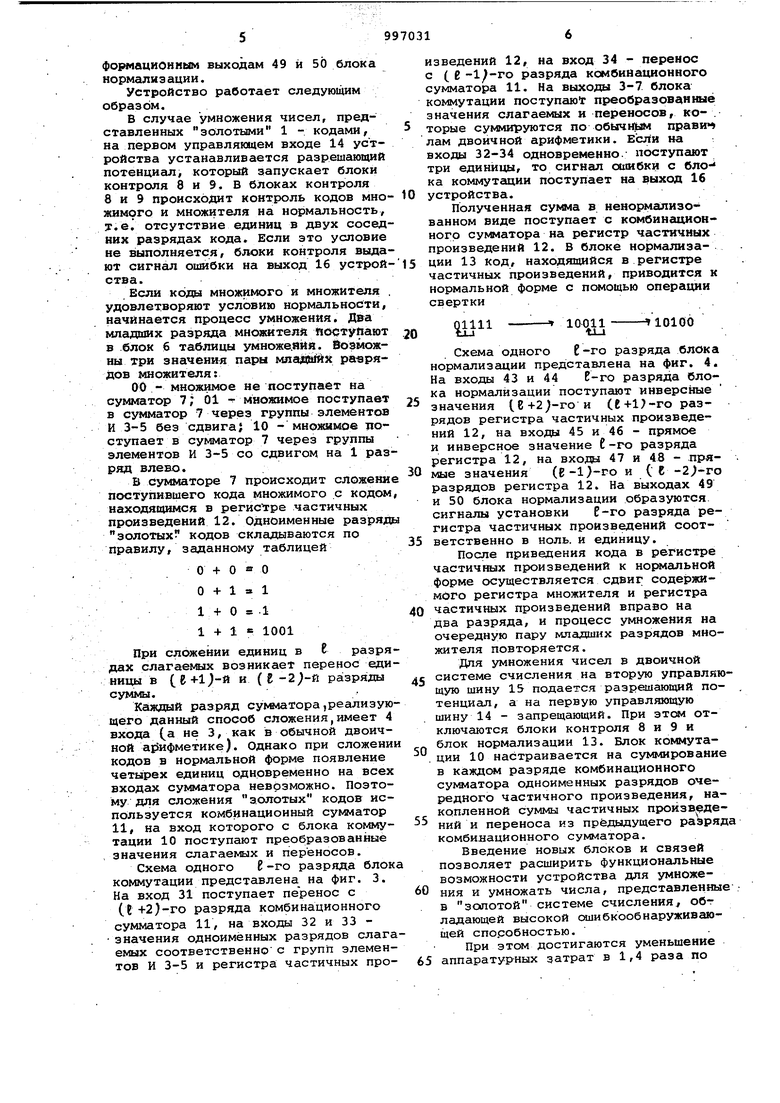

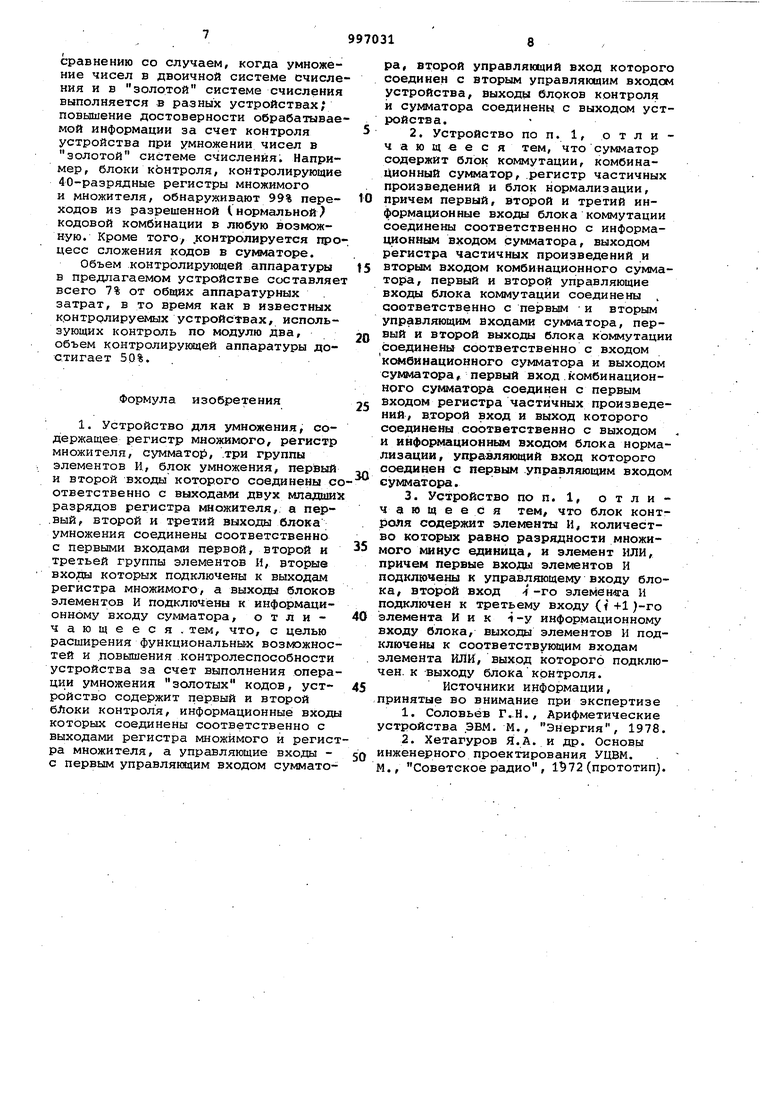

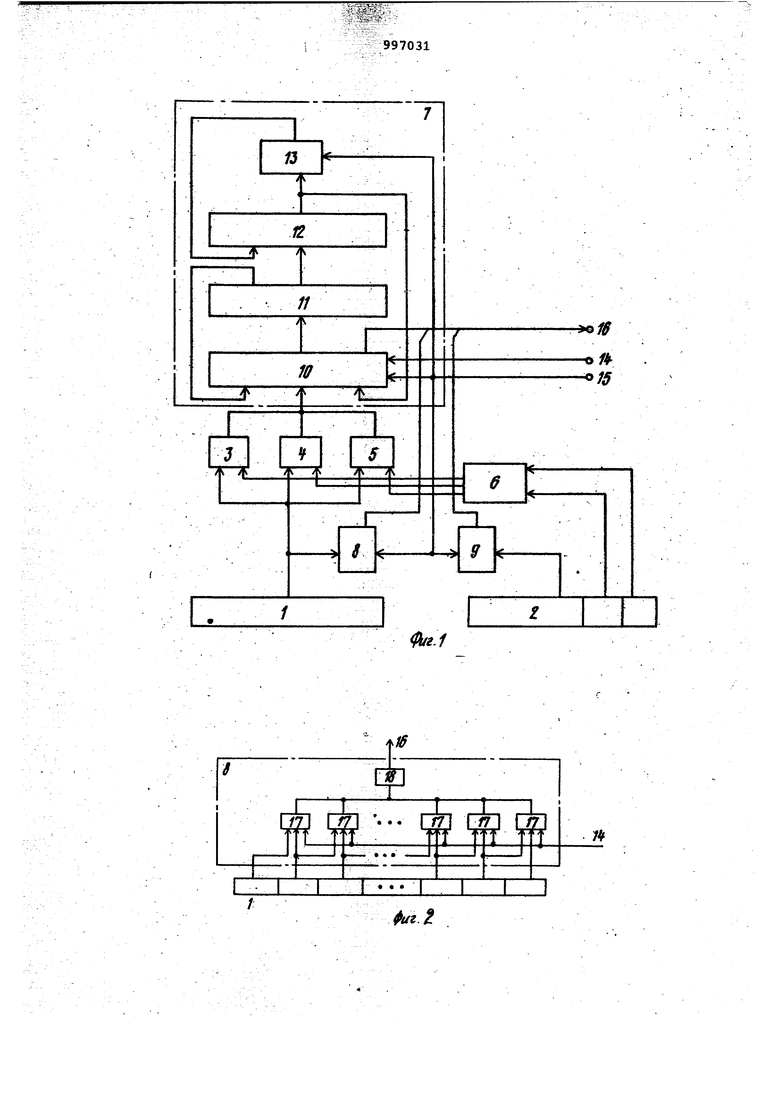

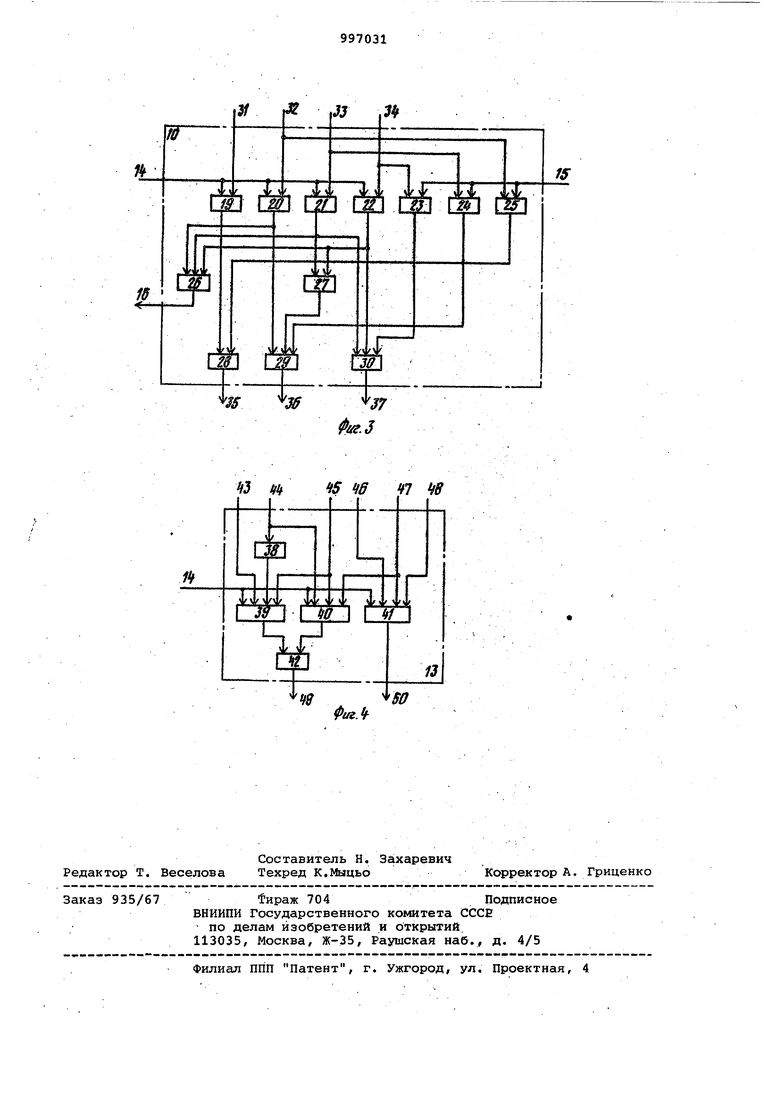

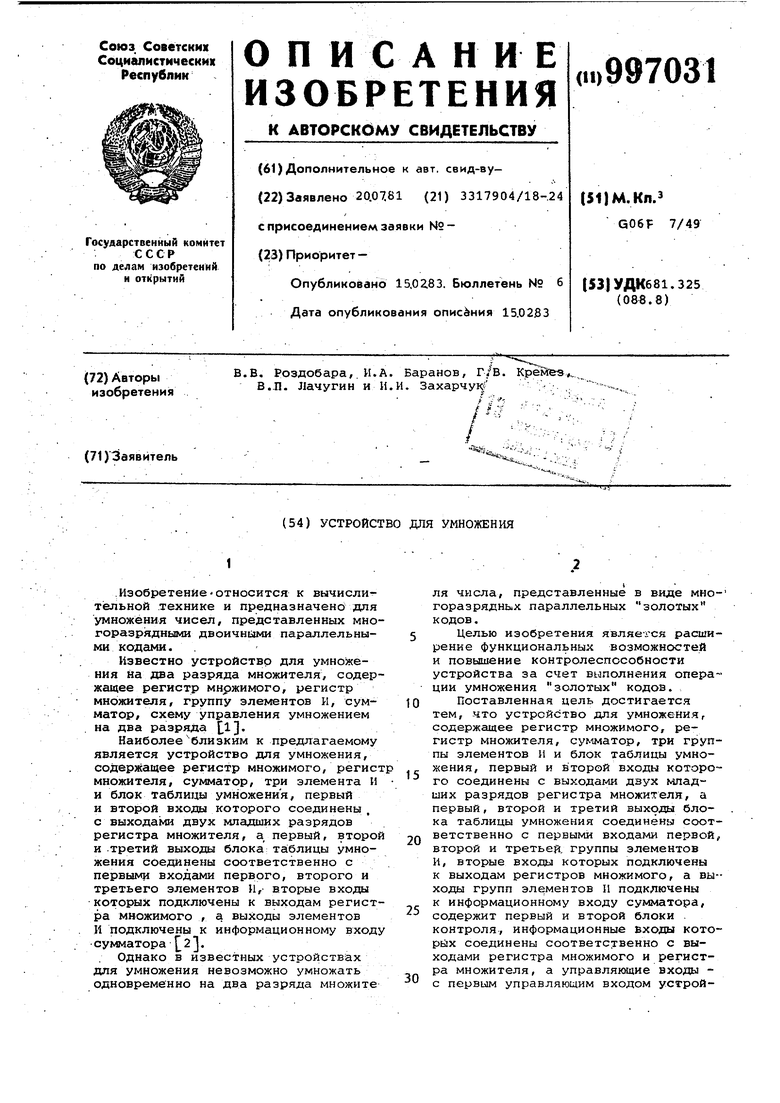

25 содержит первый и второй блоки контроля, информационные входы которйх соединены соответственно с выходами регистра множимого и регистра множителя, а управляющие входы 30с первым управляющим входом устройства и с первым управляющим входом сумматора, второй управляющий вход которого соединен со вторым управля ющим входом устройства, выходы блоков контроля и сумматора соединены ,с выходом устройства. Кроме того, сумматор содержит блок коммутации, комбинационный сум матор, регистр частичных производений и .блок нормализации, причем первый, второй и третий информационные входи блока коммутации соединены соответственно с информационным входом сумматора, выходом регис ра частичных произв.едений и вторым входом комбинационного сумматора, первый и- второй управляющие входы блока коммутации соединены .соответственно с первым и вторым уиравляющ |ми входами сумматора-, первый и второй выхода блока коммутации соединены со.ответствённо со входом ком бинационного сумматора и выходом су матора, первый выход комбинацион ного сумматора соединен с первым вх дом регистра частичных произведений второй вход и выход которого соедииены соответственно с выходом и информационным входом блока нормализации,, управлямщий вход которого соединен с первым управляющим входом сумматора. t . Блок контроля содержит элементы. И, колйчестйо которых равно разряда ности множимого минус единица, и элемент .ИЛИ,- причем первые входы элементов И подключены к управляюще му входу блока, второй вход 1-го эл мента И подключен к третьему входу, i -1 элемента И и к i -у информационному входу блока, выходы элементов И подключены к соответствующим входам элемента ИЛИ, выход кото рого подключен к выходу блока конт роля . Золотые коды являются кодами степенной избыточной системы счисле ния с иррациональным основанием d являющимся положительным корнем ура нения х -х- 1 +. Веса в золотых кодах имеют сле дуювше свойства: t как в двоичной классической системе счисления, . как в двоичной фибоначчиевой систем счисления. Операции свертки, развертки, сло жения, вычитания,.кодирования отрицательных чисел и основные контроль ные соотношения для золотых кодов аналогичны соответствующим операциям для кодов Фибоначчи. Операции ножения и деления чисел в золотых кодах аналогичны соответствующим операциям в двоичной системе счисления. На фиг. 1 представлена блок-схема устройства, на фиг. 2 - блок-схема контроля с регистром множимого} на фиг. 3 - один разряд блока коммутации, на фиг. 4 - один разряд блока нормализации. Устройство содержит регистр множимого 1, регистр множителя 2, три группы элементов и 3-5, блок таблицы умножения б, сумматор 7, первый блок контроля 8, второй блок контроля 9, блок коммутации 10, комбинационный сумматор 11, регистр частичных произведений 12, блок нормализации 13. Первый и второй входы блока коммутации подключены соответственно к первому и второму управляющим входам 14 и 15 устройства. Выход сумматора и выходы первого и второго блоков контроля подключены к выходу 16 устройства. Блок контроля 8 содержит элементы И 17, элемент ИЛИ 18, причем число элементов И равно разрядности множимого минус единица, первые входы элементов И подключены к управляющему входу блока, выход элемента ИЛИ 18 является выходом блока контроля. Один разряд блока коммутации 10 содержит элементы И 19-27 и элементы ИЛИ 28-30. Первые входы элементов И 19-22 подключены к информационным входам 31-34. блока коммутации. Первые входы элементов И 23-25-соединены соответственно с первыми входами элементов И 20-22. Вторые входы элементов И .19-22 подключены к первому управляющему входу 14 устройства, вторые входа элементов и 23-25 подюпочены ко второму управляющему входу 15 устройства. Выходы элементов ИЛИ 28-30 являются соответственно информационными выходами 35-37 блока коммутации. Выход элемента И 26 подключен к выходу 16 устройства. Один разряд блока нормализации 13 содержит элемент НЕ 38, элементы И 39-41, элемент ИЛИ 42. Первые входы элементов И 39-41 подключены к первому управляющему входу 14 устройства. Вторые входы элементов И 39-41 подключены соответственно к информационным входам 43, 44 и 46 блока нормализации. Третьи входы элементов И 40 и 41 подключены соответ ственно к информационнымвходам 45 и 47 блока нормализации, четвертый вход элемента И 41 подключен .к информационному входу 48 блока нормализации. Выходы элементов ИЛИ 42 и И 41 подключены соответственно к информационным выходам 49 и 50 блока нормализации. Устройство работает следующим образом. В случае умножения чисел, представленных золотыми 1 - кодами, на первом управляющем входе 14 устройства устанавливается разрешающий потенциал, который запускает блоки контроля 8 и 9, В блоках контроля 8 и 9 происходит контроль кодов мно жимого и множителя на нормальность, т.е. отсутствие единиц в двух сосед них разрядах кода. Если это условие не выполняется, блоки контроля выда ют сигнал ошибки на выход 16 устрой ства. Если коды множимого и множителя удовлетворяют условию нормальности, начинается процесс умножения. Д&а младших разряда множители По ;ту11ают в блок 6 таблицы умноже.ййя. ЗоЭможны три значения пары млагШгх разрядов множителя: 00 - множимое не поступает на сумматор 7; 01 - множимое поступает в сумматор 7 через группы элементов И 3-5 без сдвига; 10 - мнохшмое лоступает в сумматор 7 через группы элементов И 3-5 со сдвигом на 1 раз ряд влево. В сумматоре 7 происходит сложени поступившего кода множимого с кодом находящимся в регисТре частичных произведений 12. Одноименные разряда золотых кодов складываются по правилу, заданному таблицей 0 + 0 0 О + 1 1 1 + 0 1 При сложении единиц в Е разря дах слагаемых возникает перенос еди ницы в ( и {l-2)-fi разряды cyttMtu. Каждый разряд суивватора,реализую щего данный способ сложения,имеет 4 входа (а не 3, как в обычной двоичной аЕ1Ифметике). Однако при сложени кодов в нормальной форме появление четырех единиц одновременно на всех входах сумматора невозможно. Поэтому для сложения золотых кодов используется комбинационный сумматор 11, на вход которого с блока коммутации 10 поступают преобразованные значения слагаемых и переносов. Схема одного Е-го разряда блок коммутации представлена на фиг. 3. На вход 31 поступает перенос с ({ +2)-го разряда комбинационного сумматора 11, на входы 32 и 33 значения одноимённых разрядов слага емых соответственнос групп элементов И 3-5 и регистра частичных произведений 12, на вход 34 - перенос с (К разряда комбинационного сумматора 11. На выходы 3-7 блока коммутации поступают преобразованные значения слагаемых и переносов, ко- . торые суммируются по обычН ММ прави лам двоич ной арифметики. Если на входы 32-34 одновременно, поступают три единицы, то сигнал сшибки с бло- ка коммутации поступает на выход 16 устройства. Полученная сукма в ненормализованном виде поступает с комбинационного сумматора на регистр частичных произведений 12. В блоке нормализации 13 код, находящийся в регистре частичных произведений, приводится к нормальной форме с помощью операщ1и свертки . Схема одного 6-го разряда блока нормализации представлена на фиг. 4. На входы 43 и 44 В-го разряда блока нормализации поступают инверсные значения (, и ( разрядов регистра частичных произведений 12, на входы 45 и 46 - прямое и инверсное значение 6-го разряда регистра 12, на входы 47 и 48 - прямые значения (C-l)-ro и ( в разрядов регистра 12. На выходах 49 и 50 блока нормализации образуются сигналы установки Е-го разряда регистра частичных произведений соответственно в ноль, и единицу. После приведения кода в ре гистре частичных произведений к нормальной форме осуществляется сдвиг содержимого регистра множителя и регистра частичных произведений вправо на два разряда, и процесс умножения на очередную пару младших разрядов множителя повторяется. Для умножения чисел в двоичной системе счисления на вторую управляющую шину 15 подается разрешающий потенциал, а на первую управляющую шину 14 - запрещающий. При этсм отключаются блоки контроля 8 и 9 и блок нормализации 13. Блок коммутации 10 настраивается на суммирование в каждом разряде комбинационного сумматора одноименных разрядов очередного частичного произведения, накопленной суммы частичных произв дений и переноса из предыдущего разряда комбинационного сумматора. Введение новых блоков и связей позволяет расширить функциональные возможности устройства для умножения и умножать числа, представленные . в золотой системе счисления обг ладающей высокой ошибкообнаруживающей споробностью. При этом достигаются уменьшение аппаратурных затрат в 1,4 раза по

сравнению со случаем, когда умножение чисел в двоичной системе счисления и в золотой системе счисления выполняется в разных устройствах; повышение достоверности обрабатываемой информации за счет контроля устройства при умножении чисел в золотой системе счисления. Например, блоки кЬнтроля, контролирующие 40-раэрядные регистры множимого и множителя, обнаруживают 99% переходов из разрешенной (нормальной кодовой комбинации в любую возможную. Кроме того, .контролируется процесс сложения кодов в сумматоре.

Объем контролирующей аппаратуры в предлагаемом устройстве составляет всего 7% от общих аппаратурных затрат, в то время как в известных контролируемых устройствах, использующих контроль по модулю два, объем коитролирукщей аппаратуры достигает 5D%. ,

Формула изобретения

1. Устройство для умножения, содержащее регистр множимого, регистр

множителя, суммато, .три группы элементов И, блок умножения, первый и второй входы которого соединены сО ответственно с выходами двух младших разрядов регистра множителя,, а пер.вый, второй и третий выходы блока умножения соединены соответственно с первыми входами первой, второй и третьей группы элементов И, вторые входы которых подключены к выходам регистра множимого, а выходы блоков элементов И подключены к информационному входу сумматора, отличающееся, тем, что, с целью расширения функциональных возможностей и повышения контролеспособности устройства за счет выполнения операции умножения золотых кодов, устройство содержит первый и второй бЛоки контроля, информационные входы которых соединены соответственно с выходами регистра множимого и регистра множителя, а управляющие входы с первым управляняцим входом сумматора, второй управляющий вход которого соединен с вторым управляющим входом устройства, выходы блоков контроля и сумматора соединены с выходом устройства.

2. Устройство по п. 1, отличающееся тем, что сумматор содержит блок коммутации, комбинационный сумматор, регистр частичных произведений и блок нормализации,

0 причем первый, второй и третий информационные входы блока коммутации соединены соответственно с информационным входом сумматора, выходом регистра частичных произведений и

5 вторым входом комбинационного сумматора, первый и второй управляющие входы блока коммутации соединены , соответственно с первым и вторым управляющим входами сумматора, перп вый и второй выходы блока коммутации соединены соответственно с входом комбинационного сумматора и выходом сумматора, первый вход комбинационного сумматора соединен с первым

5 входом регистра частичных произведений, второй вход и выход которого соединены соответственно с выходом и информационньа«1 входом блока нормализации, управляющий вход которого соединен с первым управляющим входом сумматора.

3. Устройство по п. 1, отличающееся тем, что блок контроля содержит элементы И, количество которых равно разрядности множи5 мого минус единица, и элемент ИЛИ, причем первые входа элементов И подключены к управляющему входу блока, второй вход -f -го элемента И подключен к третьему входу (f+1 }-го

0 элемента Ник i-у информационному входу блока, выходы элементов И подключены к соответствующим входам . элемента ИЛИ, выход которого подключен, к выходу блока контроля.

5 Источники информации,

принятые во внимание при экспертизе

1.Соловьёв Г.Н., Арифметические устройства ЭВМ. М., Энергия, 1978.

2.Хетагуров Я.А. и др. Основы Q инженерного проектирования УЦВМ.

М., Советское радио , (прототип;.

jj

У1

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для умножения | 1983 |

|

SU1200280A1 |

| Устройство для умножения | 1981 |

|

SU1024906A1 |

| Устройство для умножения | 1982 |

|

SU1059566A1 |

| Устройство для умножения | 1983 |

|

SU1130859A1 |

| Устройство для умножения | 1981 |

|

SU1013946A1 |

| Устройство для умножения чисел в @ -кодах Фибоначчи | 1980 |

|

SU1137459A1 |

| Устройство для умножения | 1984 |

|

SU1226447A1 |

| Вычислительное устройство | 1981 |

|

SU997030A1 |

| УСТРОЙСТВО УМНОЖЕНИЯ | 1998 |

|

RU2148270C1 |

| Устройство для вычисления сумм произведений | 1982 |

|

SU1020818A1 |

IS

УЩЛ

Li

a

iLsi

S$

фаг.З

Авторы

Даты

1983-02-15—Публикация

1981-07-20—Подача