1

Изобретение относится к вычисли- 1 тельной технике и может быть использо вано в устройствах отображения апфа витно-цифровой информа|Ц1И на aiqpaHe ЭЛТ (дисплеях), применяющихся в каче стве буферного эапомннаисщего устр Лства (ЗУ) с произ вольным доступом.

Известно устройство отображения ,в которст преобразование кода адреса экрана в адрес буферного ЗУ реаяяэовано по классическому способу дешифратор - шифратор. В состав бЛока шбора адресов такого устройства входит счетчик позиций, счетчик строк, один многоступенчатый дешифратор, шифратор регистр адреса ЗУ

Недостатками такого устройства являются большие затраты оборудования, необходимого для построения дешифрато ра и шифратора; многоступенчатость схема преобразователя и, как следстви этого, значительные задержки адресных сигналов при прохонщении через эту схему; большое число связей между элементами и связанная с ним сложность их реализации печатным монтажом, а .также значительная мощность, потребляемая блоком выбора сщресов от источников питания.

Известно также устройство, ссадержацее счетчик позиций, счетчик строк, дешн ргатс мпздших разрядов счетчиков поэнций и строк, дешифратсфы старших {хаэридов счетчиков позиций и строк и регистр арреса 2,

Наиболее близким по технической cyveifXffjt к тфедлагаемому является блок управления выбором адресов запойинаюнего устройства, в состав которого вхспят счетчик позиций, счетчик строк и регистр гщрвса ЗУ З.

Однако для адресации ЗУ требуется ввеяеяне в устройство дополнительного несиихронизированного реверсивного счетчика адреса ЗУ и схем, управляющих его работ А; значительная и непостоянная задержка фсфмирования адреса, зависящая от исходного и требуемого щреса, что создает серьезные неудобства 1фи построении таких синxpoHiflbUC устройств, как дисплей.

Цель изобретения - упрощение устройства.

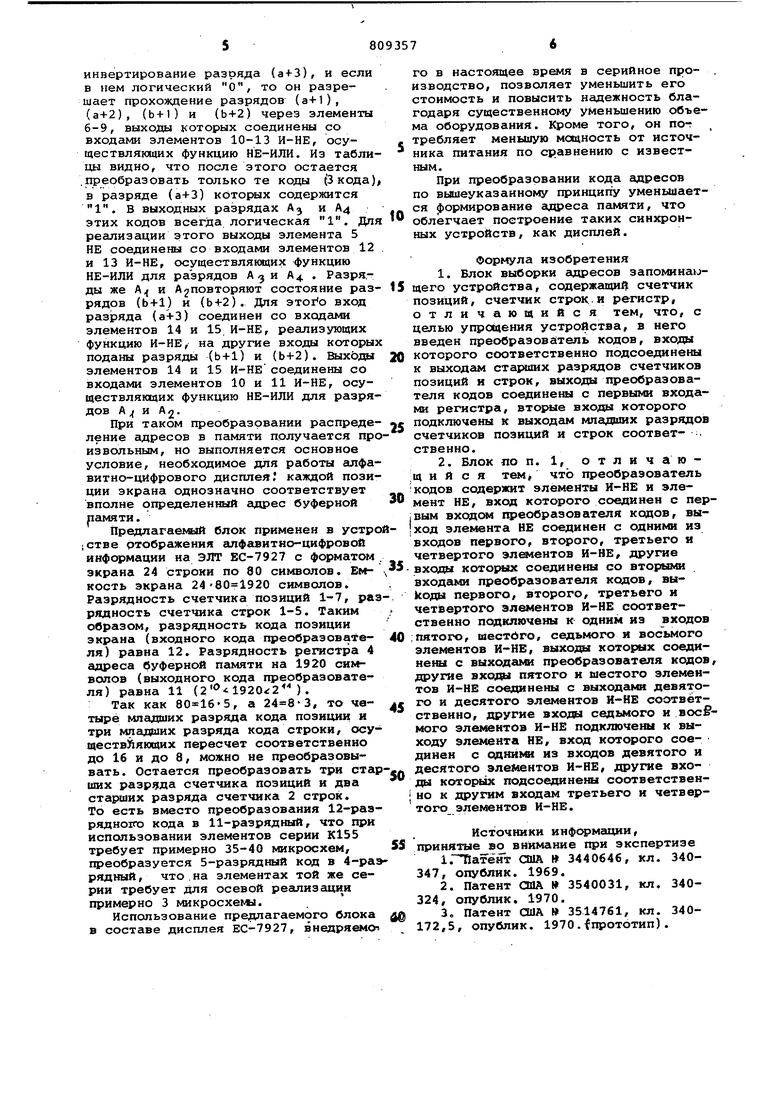

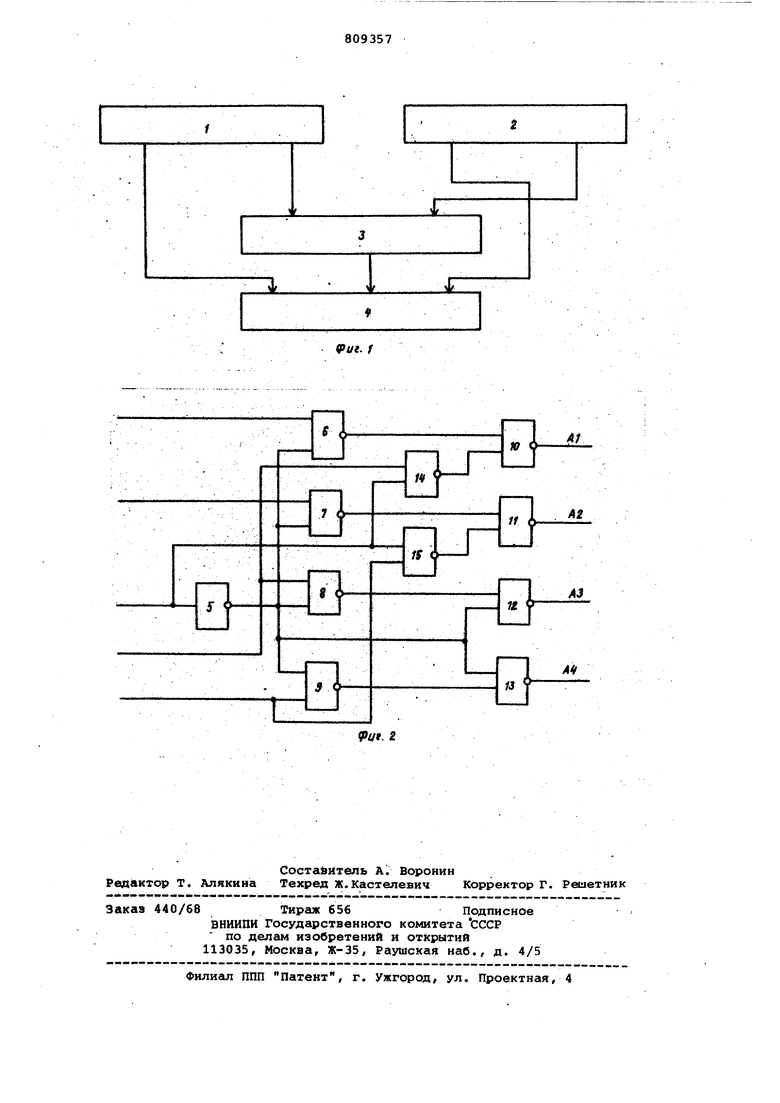

Поставленная цель достигается тем, что в блок выборки адресов запомингиощего устройства, содержащий счетчик позиций, счетчик строк и регистр, введен преобразователь кодов, входы которого соответственно подсоединены к выходамстарших разрядов счетчиков позиций и строк, выходы преобразователя кодов соединены с первыми входами регистра, вторые входы которого подключены к выходам младших разрядов счетчиков позиций и строк соответ ственно, а также тем, что преобразова тель кодов содержит элементы И-НЕ « элемент НЕ, вход которого соединен с первым входом преобразователя кодов выход элемента НЕ соединен с одними из входов первого, второго, третьего и четвертого элементов И-НЕ, другие входы которых соединены со вторыми входами преобразователя кодов, выходы первого, второго, третьего и четвертого элементов И-НЕ соответственно подключены к одним из входов пятого, шесто го, седьмого и восьмого элементов ,И-НЕ, выходы которых соеди-нены с выхо дами преобразователя кодов, другие входы пятого и шестого элементов И-НЕ соединены с выходс1ми девятого и десятого элементов И-НЕ соответственно другие входы седьмого и восьмого элементов И-НЕ подключены к выходу элемента НЕ, вход которого соединен с одними из входов девятого и десятого элементов И-НЕ, другие входы которых подсоединены соответственно к другим входам третьего и четвертого элементов И-НЕ. На фиг. 1 изображена функциональная схема: блока выборки адресов запоминающего устройства/ на фиг. 2 функциональнгш схема преобразователя кодов. Блок выборки ёщресов запоминаихцего устройства содержит счетчик 1 позиций, счётчик 2 строк, преобразователь 3 кодов, регистр 4. Преобразователь кодов содержит эле мент 5 НЕ и элементы 6-15 И-НЕ. Блок работает следуюи им образом. Обозначим количество позиций сим-, волов в строкв алфавитно-цифрового дисплея через М, а количество строк на экране через N. Предположим, что числа М и N состоят из двух сомножителей, один из которых является степенью числа 2, а второй соответствен но равен 5 и 3; т.е. М 2«- 5 N . 2. 3, где аи Ь - любые числа натурального ряда, кроме нуля, т.е. а,,2, 3 / ч. Очевидно, что число разрядов в счетчике 1 позиций равно (4+3). Соответственно число разрядов в счетчике 2 строк равно (Ь+2). Общее количество разрядов в коде позиции экрана равно а+З+Ь+2 а+Ь+5. Количество знакомест на экране, а соответственно и емкость буферной памяти, необходимой для хранения отоб ражаемой на экране информации равно Н -М. Поскольку числа N и М не являются степенью числа 2, то и их произведение также не является степенью числа 2, т.е. 2 iN-М. Отсюда видно, что количество разрядов в коде адреса буферной nat/MTH, содержащей N М ячеек, равно X. Тогда 2 --:2°-5 2 2 152 |2. Отсюда Х а+Ь+4. Поскольку формат адреса экрана (а+Ь+5) не соответствует формату адреса буферной памяти (а+Ь+4), требуется преобразовать код адреса экрана в код-адреса буферной памяти. Так как входной код является избыточным, то при преобразованни его можно минимизировать. Так как а и b - степени числа 2, то в этих разрядах входного кода избыточности нет. сЛедовательно, минимизировать преобразователь 3 за счет этих разрядов невозможно. Значит младшие разряды а счетчика 1 позиций и младише разряды Ь счетчика 2 строк можно подать в регистр 4 буферной памяти без преобразования, т.е. разряды а и Ь входного кода являются составной частью разрядов х выходного кода. Остается преобразовать пять разрядов в четыре разряда. Для этого, старшие три разряда счетчика 1 позиций и старшие два разряда счетчика 2 строк подаются на вход преобразователя 3,с выхода которого четыре преобразованных разряда поступают в регистр 4 адреса буферной памяти. Преобразователь работает следующим образом. Так как разряды (а+1)-(а+3) принимают пять состояний (От О до 4), а разряды (Ь+1) и (Ь+2) - три состояния (от О до 2), то можно записать таблицу состояний для данного преобразователя:Поскольку распределение адресов в памяти может быть произвольным, то таблица строится по принципу максимгшьной похожести кодов. Если во входном разряде (а+3}логический 0,то разряды (а+1), (а+2), (Ь+1) и (Ь+2) повторяются в выходных разрядах А , л , Л , и А. .На элементе 5 осущестрччетсяг

инвертирование разряда (а-ьЗ), и если в нем логический О, то он разрешает прохождение разрядов {а+1), (а+2), (Ь+1) и (Ь+2) через элементы 6-9, выходы которых соединены со входами элементов 10-13 И-НЕ, осуществлякзщих функцию НЕ-ИЛИ. Из таблицы видно, что после этого остается .преобразовать только те коды (Зкода) в разряде (а+3) которых содержится 1. в выходных разрядах Aj и А4 этих кодов всегда логическая 1. Для реализации этого выходы элемента 5 НЕ соединены со входами элементов 12 и 13 И-НЕ, осуществляющих функцию НЕ-ИЛИ для разрядов А4 . Разряды же А и А повторяют состояние разрядов (b+l) и (Ь+2). Для этого вход разряда (а+3) соединен со входами элементов 14 и 15 И-НЕ, реализующих функцию И-НЕ, на другие входы которых поданы разряды (Ь+1) и (Ь+2). Выходы элементов 14 и 15 И-НЕсоединены со входами элементов 10 и 11 И-НЕ, осуществляющих функцию НЕ-ИЛИ для разрядов А и А 2.

При таком преобразовании распределение адресов в памяти получается произвольным, но выполняется основное условие, необходимое для работы алфавитно-цифрового дисплея каждой позиции экрана однозначно соответствует вполне определенный гщрес буферной памяти.

Предлагаемый блок применен в устро|стве отображения алфавитно-цифровой информации на ЭЛТ ЕС-7927 с форматом экрана 24 строки по 80 символов. Емкость экрана 24вО 1920 символов. Разрядность счетчика позиций 1-7, раз рядность счетчика строк 1-5. Таким образом, разрядность кода позиции экрана (входного кода преобразсвателя) равна 12. Разрядность регистра 4 адреса буферной пгиляти на 1920 символов (выходного кода преобразователя) равна 11 (2 -Ч920 :2 ).

Так как , а , то чатырё младших разряда кода позиции и три младших разряда кода строки, осуществУхяющих пересчет соответственно до 16 и до 8, можно не преобразовывать. Остается преобразовать три старших разряда счетчика позиций и два старших разряда счетчика 2 строк. То есть вместо преобразования 12-разРЯДНО1Ю кода в 11-разрядный, что при использовании элементов серии К155 требует примерно 35-40 микросхем, преобразуется 5-разрядный код в 4-раэрядный, что на элементах той же серии требует Для осевой реалиЗс1Ш1и примерно 3 микросхемы.

Использование предлагаемого блока в составе дисплея ЕС-7927, внедряемо

го в настоящее время в серийное производство, позволяет уменьшить его стоимость и повысить надежность благодаря существенному уменьшению объема оборудования. Кроме того, он пог требляет меньшую мощность от источника питания по сравнению с известным.

При преобразовании кода адресов по вышеуказанному принципу уменьшается формирование адреса памяти, что облегчает построение таких синхронных устройств, как дисплей.

Формула изобретения

1.Блок выборки адресов запоминающего устройства, содержсцций счетчик позиций, счетчик строк., и регистр, отличающийся тем, что, с целью упрощения устройства, в него введен преобразователь кодов, входы которого соответственно подсоединены к выходам старших разрядов счетчиков позиций и строк, выходы преобразователя кодов соединены с первыми входами регистра, вторые входа которого подключены к выходам младших разрядов счетчиков позиций и строк соответ- . ственно.

2.Блок лоп. 1, отличающийся тем что преобразователь кодов содержит элементы И-НЕ и элемент НЕ, вход которого соединен с первым входом преобразователя кодов, выход элемента НЕ соединен с одними из входов первого, втсфого, третьего и четвертого элементов И-НЕ, другие вхсдф которых соединены со вторыми входами преобразователя кодов, выКоды первого, второго, третьего и четвертого элементов И-НЕ соответственно подключены к одним из входов пятого, шестого, седьмого и восьмого элементов И-НЕ, выходы которых соединешл с выходами преобразователя кодов другие вхоиоы пятого и шестого элементов И-НЕ соединены с выходами девятого и десятого элементов И-НЕ соответственно, другие входы седьмого и восбмого элементов И-НЕ подключены к выходу элемента НЕ, вход которого соединен с одниАШ из входов девятого и десятого элементов И-НЕ, другие входы которых подсоединены соответственно к другим входам третьего и четвертого элементов И-НЕ.

Источники инфс мации, принятые 9О внимание при экспертизе

1.ТЙате5Гт СЗИА В 3440646, кл. 340347, опублик. 1969.

2. Патент США 3540031, кл. 340324, опублик. 1970.

3„ Патент ОНА 3514761, кл. 340172,5, опублик. 1970.fпрототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| Многоканальный преобразователь амплитуды телевизионного сигнала во временной интервал | 1983 |

|

SU1124452A1 |

| Устройство для отображения информации на экране телевизионного индикатора | 1980 |

|

SU955189A1 |

| Преобразователь двоичного кода в код с произвольным весом младшего разряда | 1985 |

|

SU1325708A1 |

| Запоминающее устройство | 1987 |

|

SU1413674A1 |

| Устройство для управления оперативной памятью | 1985 |

|

SU1291992A1 |

| УСТРОЙСТВО ДЛЯ СЧИТЫВАНИЯ ИЗОБРАЖЕНИЯ | 1992 |

|

RU2045781C1 |

| Устройство для отображения информации на экране телевизионного приемника | 1984 |

|

SU1265834A1 |

| Дисплейный процессор | 1981 |

|

SU1292031A1 |

| Преобразователь телевизионного стандарта | 1980 |

|

SU1238267A1 |

| Устройство для отображения информации на газоразрядной индикаторной панели | 1989 |

|

SU1605279A2 |

Авторы

Даты

1981-02-28—Публикация

1979-02-05—Подача