о:

оо

00 С5

2. Устройство по п. 1, отличающееся тем, что блок контроля содержит две группы сумматоров по модулю два, две группы элементов И и элемент И, причем входы сумматоров по модулю два первой группы объединены и являются первым входом блока контроля, входы элемента И объединены и являются вторым входом блока контроля, а входы сумматора по модулю два второй группы объединены и являются третьим входом блока контроля, выходы сумматоров

по модулю два первой группы соединены с соответствующими входами элементов И первой группы, другие входы которых соединены с соответствующими входами элемента И, выход которого подключен к одним входам элементов И второй группы, другие входы которых подключены к соответствующим выходам сумматоров по модулю два второй группы, а выходы элементов И групп являются соответствующими выходами блока контроля.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для управления каналами | 1984 |

|

SU1372329A2 |

| ОПЕРАТИВНОЕ ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО С ВЫСОКОЙ СТЕПЕНЬЮ ОТКАЗОУСТОЙЧИВОСТИ | 2005 |

|

RU2327236C2 |

| Устройство управления обращением к памяти | 1984 |

|

SU1211737A1 |

| Устройство для формирования команд с аппаратной организацией циклических программ | 1979 |

|

SU942018A1 |

| Устройство для формирования команд | 1978 |

|

SU734686A1 |

| Устройство для сопряжения каналов передачи данных с ЭВМ | 1985 |

|

SU1226476A1 |

| Селекторный канал | 1978 |

|

SU798779A1 |

| Устройство для подключения устройств ввода-вывода к многосегментной магистрали | 1987 |

|

SU1564638A2 |

| Устройство для динамического преобразования адресов | 1980 |

|

SU903878A1 |

| Устройство для адресации буферной памяти | 1978 |

|

SU717771A1 |

1. ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО С САМОКОНТРОЛЕМ, содержащее регистр адреса, основную память, буферную память, причем вход регистра адреса является первым входом устройства, первый выход регистра адреса соединен с соответствующим входом основной памяти, второй выход регистра адреса соединен с первым входом буферной памяти и втЪрым входом основной памяти, первый выход которой соединен с вторым входом буферной памяти, третий вход которой является вторым входом устройства, а выход буферной памяти является первым выходом устройства, отлишющееся тем, что, с целью повышения надежности устройства, оно содержит дополнительную память, регистр слова, регистр поиска, блок контроля, регистр ошибок, группу элементов И, элемент ИЛИ, причем первый вход дополнительной памяти является третьим входом устройства, второй вход дополнительной памяти соединен с вторым входом регистра адреса, а выход соединен с входом регистра слова, которого соединен с первым инверсным входом элементов И группы и первым входом блока контроля, второй вход которого соединен с выходом буферной памяти, выход блока контроля соединен с входом регистра ошибок, выход которого соединен с вторым выходом устройства, выход элемента ИЛИ является i третьим выходом устройства, а вход соединен с выходами элементов И группы, вторые входы которых соединены с выходом регистра поиска, вход которого соединен с вторым выходом основной памяти, третий выход которой соединен с третьим входом блока койтроля.

Изобретение относится к вычислительной технике и .предназначено для организации буферной памяти в устройствах обработки информации с иерархической организацией памяти.

Цель изобретения - повышение надежности устройства.

Изобретение позволяет контролировать правильность работы буферной памяти и исключать из работы неисправные блоки буферной памяти динамически, без вмещательства оператора, что обеспечивает высокую надежность работы буферной памяти.

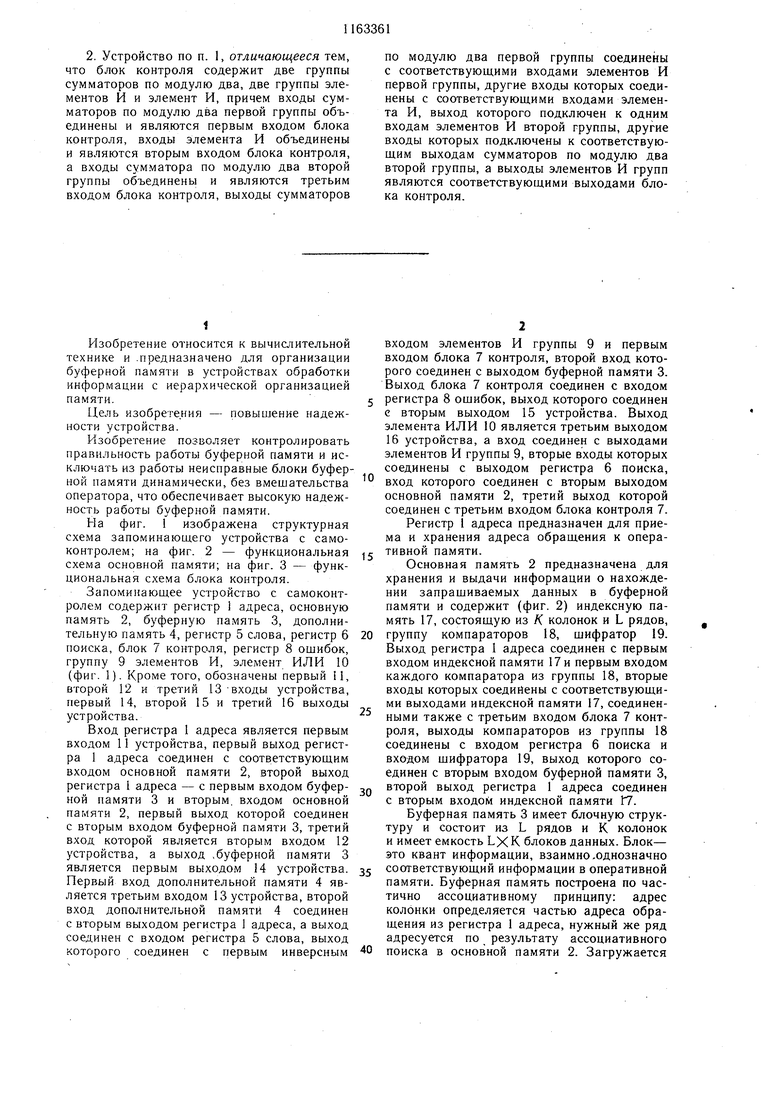

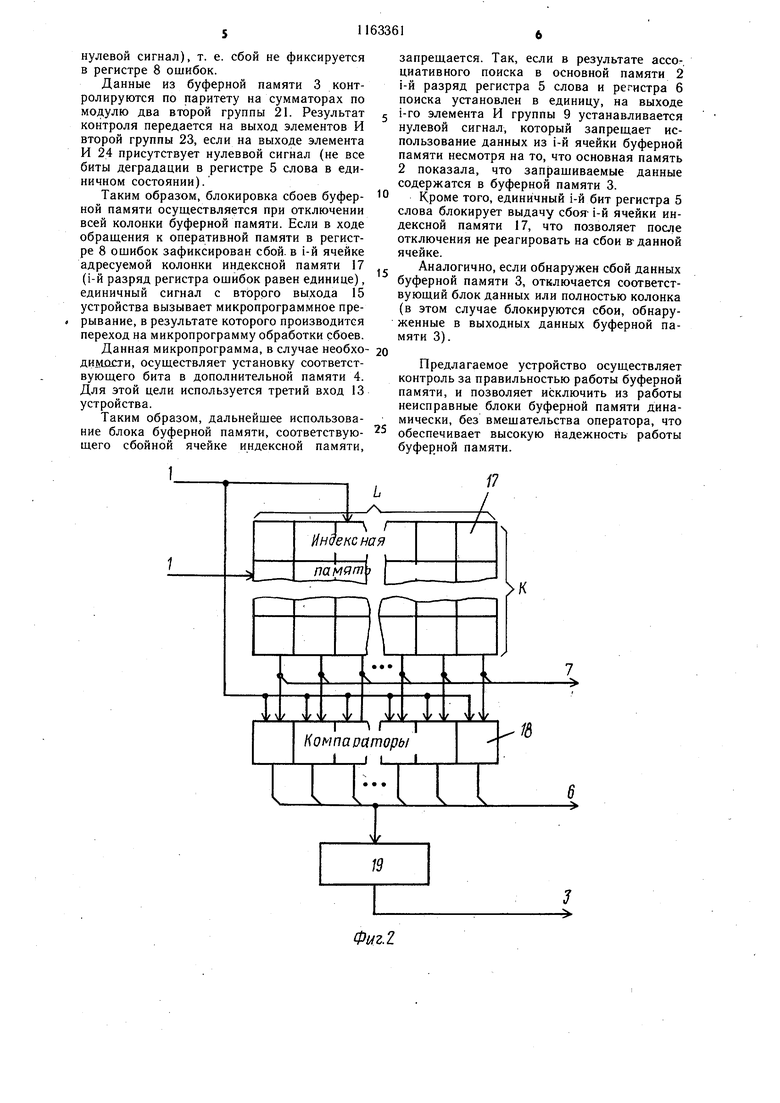

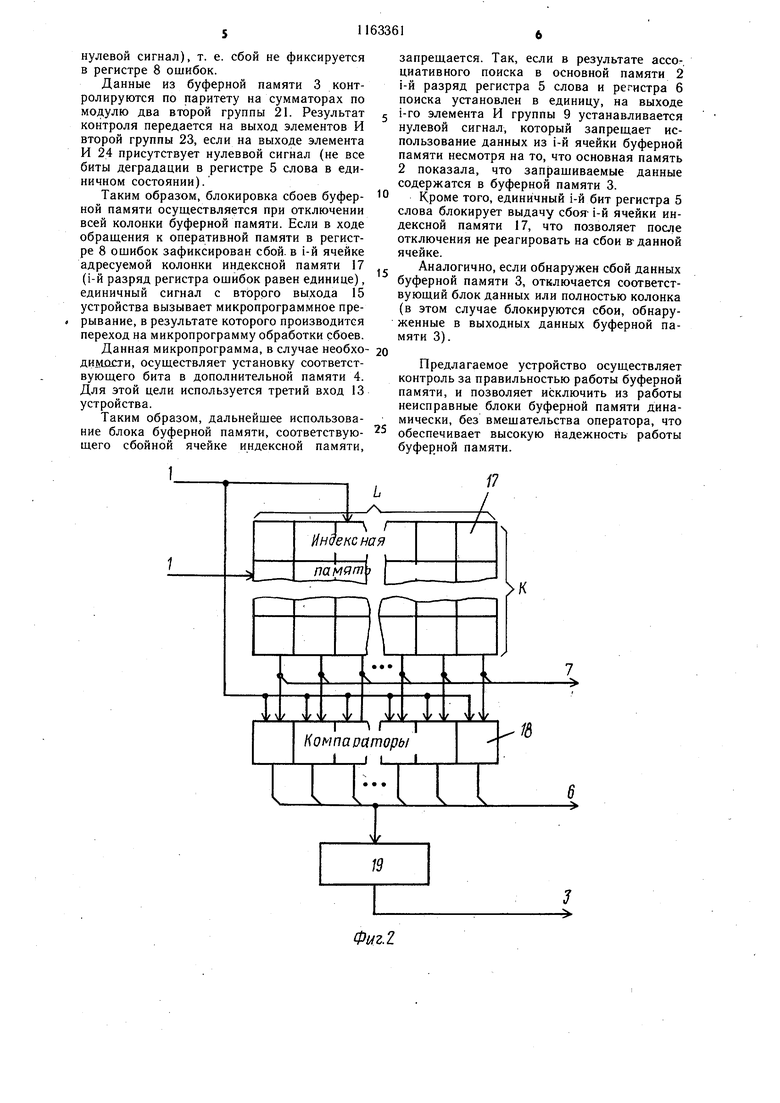

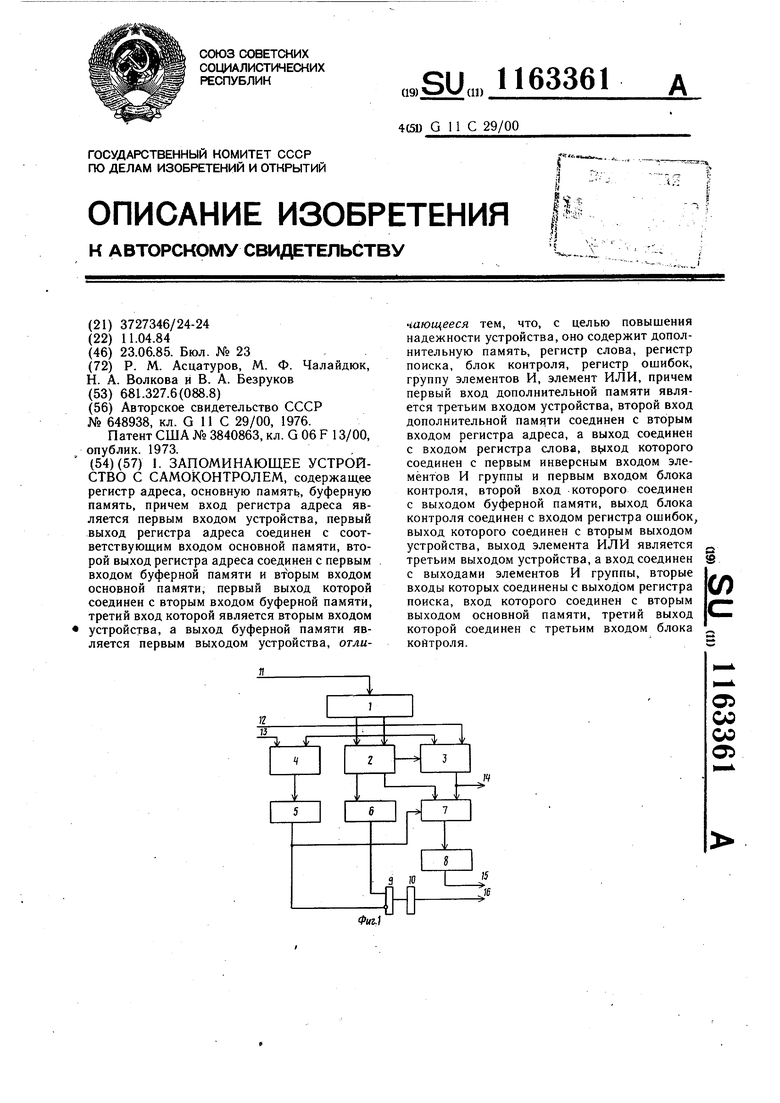

На фиг. 1 изображена структурная схема запоминающего устройства с самоконтролем; на фиг. 2 - функциональная схема основной памяти; на фиг. 3 - функциональная схема блока контроля.

Запоминающее устройство с самоконтролем содержит регистр 1 адреса, основную память 2, буферную память 3, дополнительную память 4, регистр 5 слова, регистр 6 поиска, блок 7 контроля, регистр 8 ощибок, группу 9 элементов И, эле.мент ИЛИ 10 (фиг. 1). Кроме того, обозначены первый 11, второй 12 и третий 13 входы устройства, первый 14, второй 15 и третий 16 выходы устройства.

Вход регистра 1 адреса является первым входом 11 устройства, первый выход регистра 1 адреса соединен с соответствующим входом основной памяти 2, второй выход регистра 1 адреса - с первым входом буферной памяти 3 и вторым, входом основной памяти 2, первый выход которой соединен с вторым входом буферной памяти 3, третий вход которой является вторым входом 12 устройства, а выход ,буферной памяти 3 является первым выходом 14 устройства. Первый в.ход дополнительной памяти 4 является третьим входом 13 устройства, второй вход дополнительной памяти 4 соединен с вторым выходом регистра 1 адреса, а выход соединен с входом регистра 5 слова, выход которого соединен с первым инверсным

входом элементов И группы 9 и первым входом блока 7 контроля, второй вход которого соединен с выходом буферной памяти 3. Выход блока 7 контроля соединен с входом 5 регистра 8 ошибок, выход которого соединен е вторым выходом 15 устройства. Выход элемента ИЛИ 10 является третьим выходом 16 устройства, а вход соединен с выходами элементов И группы 9, вторые входы которых соединены с выходом регистра 6 поиска,

вход которого соединен с вторым выходом основной памяти 2, третий выход которой соединен с третьим входом блока контроля 7. Регистр 1 адреса предназначен для приема и хранения адреса обращения к опера5 тивной памяти.

Основная память 2 предназначена для хранения и выдачи информации о нахождении запрашиваемых данных в буферной памяти и содержит (фиг. 2) индексную память 17, состоящую из /С колонок и L рядов,

0 группу компараторов 18, шифратор 19. Выход регистра 1 адреса соединен с первым входом индексной памяти 17 и первым входом каждого компаратора из группы 18, вторые входы которых соединены с соответствующими выходами индексной памяти 17, соединенными также с третьим входом блока 7 контроля, выходы компараторов из группы 18 соединены с входом регистра 6 поиска и входом шифратора 19, выход которого соединен с вторым входом буферной памяти 3,

„ второй выход регистра 1 адреса соединен с вторым входом индексной памяти Г7.

Буферная память 3 имеет блочную структуру и состоит из L рядов и К колонок и имеет емкость LX К блоков данных. Блок- это квант информации, взаимно .однозначно

соответствующий информации в оперативной памяти. Буферная память построена по частично ассоциативному принципу: адрес колонки определяется частью адреса обращения из регистра 1 адреса, нужный же ряд адресуется по результату ассоциативного

0 поиска в основной памяти 2. Загружается

буферная память 3 по второму входу устройства 12.

Дополнительная память 4 предназначена для хранения информации о деградации блоков буферной памяти 3. Емкость ее LXK битов (К слов длиной L битов). Если i-й бит деградации в J-M слове установлен в «1, то блок данных, находящихся в i-м ряду и j-й колонке буферной памяти 3, является недоступным для использования. Нулевое значение бита деградации разрешает использование соответствующего блока буферной памяти 3.

Регистр слова 5 предназначен для приема и хранения информации, считанной из дополнительной памяти 4; разрядность - L битов.

Регистр поиска 6 предназначен для фиксации результата ассоциативного поиска в основной памяти 2, разрядность - L битов.

Блок 7 контроля предназначен для организации контроля правильности работы буферной памяти 3 и основной памяти 2. В случае организации контроля по паритету выходной информации из буферной памяти 3 и основной памяти 2 блок 7 контроля (фиг. 3) содержит две группы 20 и 21 сумматоров по модулю два, две группы 22 и 23 элементов И и элемент И 24. Входы сумматоров по модулю два первой группы 20 объединены и являются первым входом блока 7 контроля, входы элемента И 24 объединены и являются вторым входом блока 7 контроля, а входы сумматора по модулю два второй группы 21 объединены и являются третьим входом блока 7 контроля.

Выходы сумматоров по модулю два первой группы 20 соединены с соответствующими входами элементов И первой группы 22, другие входы которых соединены с соответствующими входами элемента И 24, выход которого подключен к одним входам элементов И второй группы 23, другие входы которых подключены к соответствующим выходам сумматоров по модулю два второй группы 21. Выходы элементов И групп 22 и 23 являются сс/Ьтветствующими выходами блока 7 контроля и соединены с входом регистра 8 ощибок.

Регистр 8 ошибок предназначен для фиксации сбоев, обнаруженных блоком 7 контроля и передачи в устройство обработки информации.

Устройство работает следующим образом.

При выполнении операции обращения к оперативной памяти адрес обращения к оперативной памяти поступает на первый вход И устройства (фиг. 1) и запоминается в регистре 1 адреса. Младшая часть адреса, определяющая адрес колонки, одновременно поступает на первый вход буферной памяти 3, второй вход основной памяти 2 и второй вход дополнительной памяти 4. Старшая часть адреса из регистра 1 адреса поступает на первый вход основной памяти 2, определяющей наличие или отсутствие затребованных данных в буферной памяти 3.

Младшая часть адреса поступает в индексную память 17 (фиг. 2), где выбирается , одна из К колонок. Считанные L ячеек поступают на входы соответствующих компараторов 18, где сравниваются со старшей частью адреса. Результат ассоциативного поиска (сигналы с выходов компараторов 18) запоминается в регистре 6 поиска. Одновременно сигналы с выходов компараторов 18 поступают на шифратор 19, на выходе которого формируется адрес ряда буферной памяти, поступающий на второй вход буферной памяти 3. По полученному из основной памяти 2 адресу ряда и младшей части

адреса (адресующей колонку) буферная память 3 осуществляет считывание данных, которые передаются на первый выход устройства 14.

Одновременно осуществляется считывание L битов из дополнительной памяти 4 по младшей части адреса, которые запоминаются в регистре 5 слова.

Допустим, что запрашиваемые данные обнаружены в i-м ряду (i-й разряд регистра 6

, поиска установлен в единичное значение). При этом, если данный блок буферной памяти 3 не отключен (1-й разряд регистра 5 слова сброшен в нулевое значение), на выходе i-ro элемента И группы 9 возбуждается единичный сигнал, который, пройдя элемент

0 ИЛИ 10, поступает на третий выход устройства, свидетельствует о наличии действительных данных в буферной памяти 3 и разрешает их использование.

Если же данный блок буферной памяти отключен, то Г-и разряд регистр слова имеет

5 единичное значение (считанное из дополнительной памяти 4) и на выходе i-ro элемента И группы 9 отсутствует единичный сигнал. В этом случае на выходе элемента ИЛИ 10 присутствует нулевой сигнал, который запрещает использование данных буферной памя ти 3 и инициирует необходимость формирования обращения к оперативной памяти. Информация, считанная из буферной памяти 3 и индексной памяти 17, вместе с контрольными разрядами поступает в блок

г 7 контроля, где осуществляется ее контроль по паритету.

Содержимое выбранной колонки индексной памяти 17 (L ячеек) поступает на вход сумматоров по модулю два первой группы 20. Результаты контроля поступают на выход

элементов И первой группы 22 и фиксируются в регистре 8 ошибок, если на инверсных входах этих элементов нулевые сигналы (биты деградации в регистре 5 слова установлены в нулевое значение).

Если обнаружен сбой в данных 1-й ячейки

5 индексной памяти 17 и 1-й разряд регистра 5 слова установлен в единичное состояние, данный сбой считается недействительным (на выходе i-ro элемента И первой группы 22

нулевой сигнал), т. е. сбой не фиксируется в регистре 8 ошибок.

Данные из буферной памяти 3 контролируются по паритету на сумматорах по модулю два второй группы 21. Результат контроля передается на выход элементов И второй группы 23, если на выходе элемента И 24 присутствует нулеввой сигнал (не все биты деградации в регистре 5 слова в единичном состоянии).

Таким образом, блокировка сбоев буферной памяти осуществляется при отключении всей колонки буферной памяти. Если в ходе обращения к оперативной памяти в регистре 8 ошибок зафиксирован сбой, в i-й ячейке адресуемой колонки индексной памяти 17 (i-й разряд регистра ощибок равен единице), единичный сигнал с второго выхода 15 устройства вызывает микропрограммное прерывание, в результате которого производится переход на микропрограмму обработки сбоев.

Данная микропрограмма, в случае необходимдсти, осуществляет установку соответствующего бита в дополнительной памяти 4. Для этой цели используется третий вход 13 устройства.

Таким образом, дальнейшее использование блока буферной памяти, соответствующего сбойной ячейке индексной памяти,

I

ГГГ-ТГ1

запрещается. Так, если в результате ассо-, циативного поиска в основной памяти 2 i-й разряд регистра 5 слова и регистра 6 поиска установлен в единицу, на выходе 5 i-ro элемента И группы 9 устанавливается нулевой сигнал, который запрещает использование данных из i-й ячейки буферной памяти несмотря на то, что основная память 2 показала, что запрашиваемые данные содержатся в буферной памяти 3.

Кроме того, единичный 1-й бит регистра 5 слова блокирует выдачу сбоя- i-й ячейки индексной памяти 17, что позволяет после отключения не реагировать на сбои в-данной ячейке.

Аналогично, если обнаружен сбой данных буферной памяти 3, отключается соответствующий блок данных или полностью колонка (в этом случае блокируются сбои, обнаруженные в выходных данных буферной памяти 3).

Предлагаемое устройство осуществляет контроль за правильностью работы буферной памяти, и позволяет исключить из работы неисправные блоки буферной памяти динамически, без вмешательства оператора, что обеспечивает высокую Надежность работы буферной памяти.

Фиг.2

| Измеритель предельных значений временных интервалов | 1976 |

|

SU648938A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

| Патент США № 3840863, кл | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Приспособление для склейки фанер в стыках | 1924 |

|

SU1973A1 |

Авторы

Даты

1985-06-23—Публикация

1984-04-11—Подача