8

(Л

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство динамического преобразования адреса | 1982 |

|

SU1022165A1 |

| Запоминающее устройство с частичным резервированием | 1986 |

|

SU1434503A1 |

| МНОГОКАНАЛЬНОЕ УСТРОЙСТВО ДЛЯ РЕЗЕРВИРОВАНИЯ РАДИОСТАНЦИЙ | 1990 |

|

RU2018939C1 |

| Резервированное запоминающее устройство | 1987 |

|

SU1513526A1 |

| Устройство для моделирования структурно-сложных объектов | 1984 |

|

SU1234845A1 |

| Запоминающее устройство с автономным контролем | 1980 |

|

SU936033A1 |

| Оперативное запоминающее устройство с автономным контролем | 1978 |

|

SU744738A1 |

| Оперативное запоминающее устройство с автономным контролем | 1983 |

|

SU1113855A2 |

| Устройство для контроля блоков памяти | 1985 |

|

SU1316053A1 |

| Двухканальная резервированная вычислительная система | 1989 |

|

SU1734251A1 |

Изобретение относится к вычислительной технике и может быть использовано для управления резервом памяти вычислительной системы. Целью изобретения является сокращение объема аппаратуры при реализации функций управления резервом памяти блоками переменной длины. Поставленная цель достигается тем, что в устройство, содержащее ассоциативную память 1, выходной регистр 5, введены дешифратор 2, элемент задержки 3 и N коммутаторов 4, где N - число адресных разрядов, что позволяет снизить необходимое число ячеек ассоциативной памяти при разервировании блоков переменной длины. 3 ил.

-

- СП

ел

сриеЛ

Изобретение относится к вычислительной технике и может быть исполь- аовано для управления резервом памяти вычислительной системы.

Цель изобретения - сокращение объема аппаратуры при реализации функций управления резервом памяти блоками переменной длины.

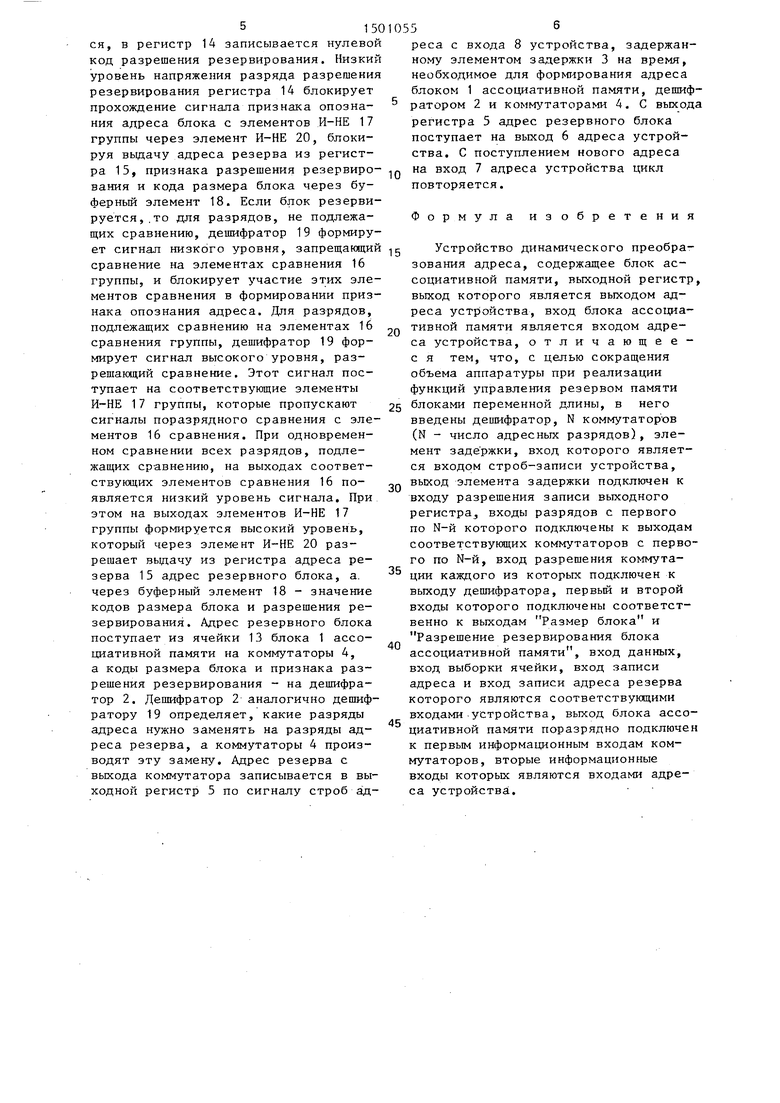

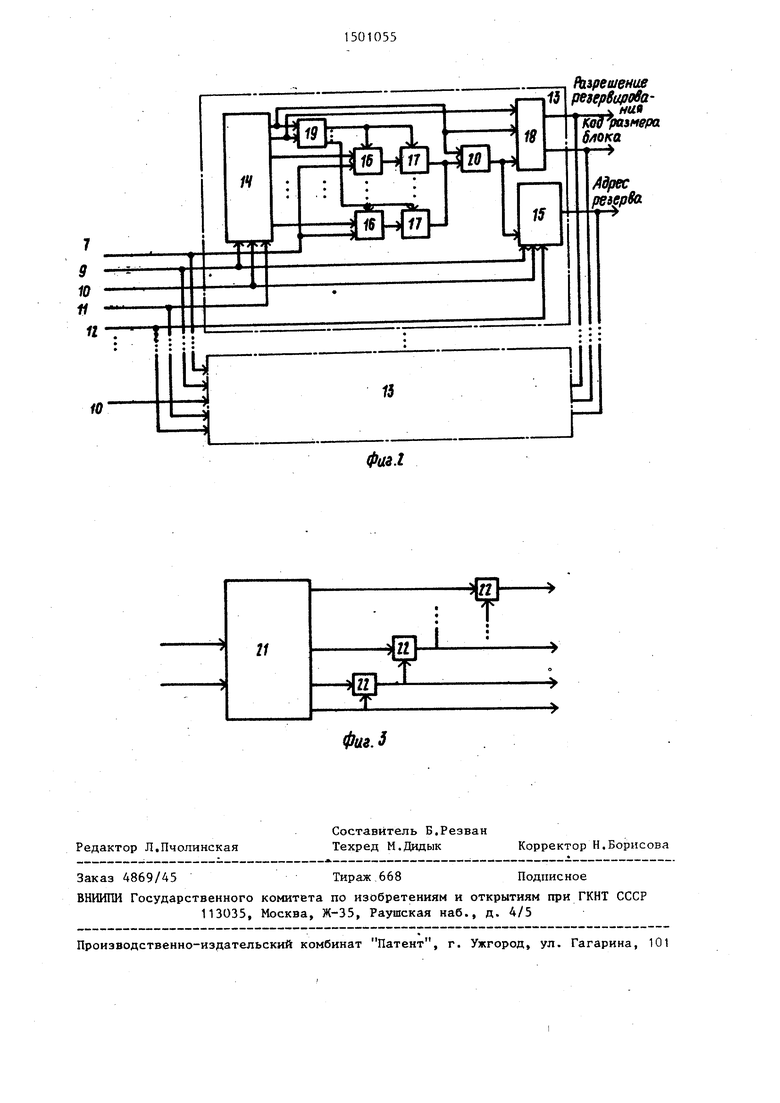

На фиг, 1 изображена блок-схема устройства динамического преобразования адреса; на фиг. 2 - блок-схема блока ассоциативной памяти 1; на фиг. 3 - блок-схема дешифратора 2.

Устройство динамического преобразования адреса содержит блок 1 ассоциативной памяти, дешифратор 2, элемент 3 задержки, группу из N одноразрядных коммутаторов 4 (где N - число адресных разрядов), выходной регистр 5, выход 6 адреса устройст- .ва, вход 7 адреса, вход 8 Строб записи, вход 9 данных, вход 10 выборки ячейки, вход 11 записи адреса и вход 12 записи адреса резерва.

Блок 1 ассоциативной памяти образуют ячейки 13 памяти, каждая из которых состоит из регистра адреса и размера резервируемого блока 14, регистра 15 адреса резерва, группы из N элементов 16 сравнения, группы из N элементов И-НЕ 17с открьп ым коллектором, бу()ерного элемента 18, дешифратора 19 и элемента И-НЕ 20. 1

Дешифратор 2 содержит двоичный

дешифратор 21 и группу из N - 1 элементов ИПИ 22.

Дешифратор 19 по структуре аналогичен дешифратору 2.

Устройство динамического преобразования адреса работает в двух режимах: программирования и преобразования адресов,

В режиме программирования в блок 1 ассоциативной памяти производится запись адресов блоков, подлежащих резервированию, кодов размеров резервируемых блоков и адресов резервных блоков. Запись в блок 1 ассоциативной памяти ведется следующим образом

На вход 9 подается адрес резервируемого блока, код размера блока и код разрешения резервирования, на вход 10 - код ядреса ячейки 13, по которому разрешается запись в регист 14 адреса и размера резервируемого блока и в регистр 15 адреса резерва этой ячейки. На вход 11 подается положительный импульс, по переднему

0

0

5

0

5

0

5

0

5

фронту которого адрес, код размера блока и код разрешения резервирования записываются в регистр 14 адреса и размера резервируемого блока. Затем на вход 9 подается адрес резервного блока, который заменяет ре- зервируем1)1й блок с адресом, хранящимся в регистре 14 ячейки 13, и на вход 12 записи в регистр адреса резерва подается положительный импульс, по переднему фронту которого адрес резервного блока записывается в регистр адреса, резерва 15. Аналогично записываются адреса, коды размеров блоков, коды разрешения резервирования и адреса резервных блоков во все необходимые ячейки 13 блока ассоциативной памяти 1. После этого устройство готово к преобразованию адресов .

В режиме преобразования адресов на входах 10 и 11 установлен низкий уровень сигнала. Адрес с входа 7 Поступает на все ячейки 13 блока ассоциативной памяти 1, а его отдельные разряды - на соответствукщие коммутаторы 4, В ячейках 13 блока 1 ассоциативной памяти в соответствии с кодами разрешения резервирования и размера блока дешифраторы 19 формируют сигналы разрешения сравнения соответствующего количества старших адресных линий входа 7 адреса устройства и содержимого адресных разрядов регистра 14 адреса и размера резервируемого блока. При резервировании отдельных ячеек памяти в разряды размера блока регистра 14 записывается нулевой код, при этом дешифратор 19 выдает сигналы разрешения сравнения на. все элементы сравнения 16 ячейки 13 блока ассоциативной памяти 1, При резервировании блока памяти в разряды размера блока регистра 14 записывается код, при котором дешифратор 19 этой ячейки 13 выдает сигналы разрешения не на все элементы 16 сравнения, а на элементы 16 сравнения старших разрядов адреса. Количество элементов 16 сравнения, осуществляющих сравнение старших разрядов адреса, определяется кодом, записанным в разряды размера блока регистра 14. Таким образом, в соответствии с размером резервируемого блока сравниваются соответствующие адресные разряды на элементах 16 сравнения. Если ячейка или блок с данным адресом не резервируются, в регистр 14 записывается нулевой код разрешения резервирования. Низкий уровень напряжения разряда разрешения резервирования регистра 14 блокирует прохождение сигнала признака опознания адреса блока с элементов И-НЕ 17 группы через элемент И-НЕ 20, блокируя выдачу адреса резерва из регистра 15, признака разрешения резервирования и кода размера блока через буферный элемент 18. Если блок резервируется,, то для разрядов, не подлежащих сравнению, дешифратор 19 формирует сигнал низкого уровня, запрещающий сравнение на элементах сравнения 16 группы, и блокирует участие этих элементов сравнения в формировании признака опознания адреса. Для разрядов, подлежащих сравнению на элементах 16 сравнения группы, дешифратор 19 формирует сигнал высокого уровня, разрешающий сравнение. Этот сигнал поступает на соответствующие элементы И-НЕ 17 группы, которые пропускают сигналы поразрядного сравнения с элементов 16 сравнения. При одновременном сравнении всех разрядов, подлежащих сравнению, на выходах соответствующих элементов сравнения 16 появляется низкий уровень сигнала. При этом на выходах элементов И-НЕ 17 группы формируется высокий уровень, который через элемент И-НЕ 20 разрешает выдачу из регистра адреса резерва 15 адрес резервного блока, а. через буферный элемент 18 - значение кодов размера блока и разрешения резервирования. Адрес резервного блока поступает из ячейки 13 блока 1 ассоциативной памяти на коммутаторы 4, а коды размера блока и признака разрешения резервирования - на дешифратор 2. Дешифратор 2 аналогично дешифратору 19 определяет, какие разряды адреса нужно заменять на разряды адреса резерва, а коммутаторы 4 производят эту замену. Адрес резерва с выхода коммутатора записывается в выходной регистр 5 по сигналу строб ад0

5

0

5

0

5

0

5

реса с входа 8 устройства, задержанному элементом задержки 3 на время, необходимое для формирования адреса блоком 1 ассоциативной памяти, дешифратором 2 и комм таторами 4. С выхода регистра 5 адрес резервного блока поступает на выход 6 адреса устройства, С поступлением нового адреса на вход 7 адреса устройства цикл повторяется.

Формула изобретения

Устройство динамического преобразования адреса, содержащее блок ассоциативной памяти, выходной регистр, выход которого является выходом адреса устройства, вход блока ассоциативной памяти является входом адреса устройства, отличающее- с я тем, что, с целью сокращения объема аппаратуры при реализации функций управления резервом памяти блоками переменной длины, в него введены дешифратор, N коммутаторов (N - число адресных разрядов), элемент заде ржки, вход которого является входом строб-записи устройства, выход элемента задержки подключен к входу разрешения записи выходного регистра входы разрядов с первого по N-й которого подключены к выходам соответствующих коммутаторов с первого по N-й, вход разрешения коммутации каждого из которых подключен к выходу дешифратора, первьм и второй входы которого подключены соответственно к выходам Размер блока и Разрешение резервирования блока ассоциативной памяти, вход данных, вход выборки ячейки, вход записи адреса и вход записи адреса резерва которого являются соответствующими входами.устройства, выход блока ассоциативной памяти поразрядно подключен к первым информационным входам коммутаторов, вторые информационные входы которых являются входами адреса устройства1.

10

Фиг.З

Л зреа/ение резервирови

нив

-чг

код размера 6/юка

Адрес pesepSa

| Патент США № 3902164, кл | |||

| Способ отопления гретым воздухом | 1922 |

|

SU340A1 |

| Приспособление для склейки фанер в стыках | 1924 |

|

SU1973A1 |

| Устройство динамического преобразования адреса | 1982 |

|

SU1022165A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1989-08-15—Публикация

1988-02-23—Подача