Изобретение относится к автоматике и цифровой вычислительной технике и может быть использовано при построении параллельных комбинационных преобразователей двоичного кода в двоично-десятичный.

Предлагаемый четырехразрядный преобразователь может выполнять роль базового блока при построении многоразрядных преобразователей. Соответствующее включение этих блоков позволяет построить преобразователь двоичного кода в двоично-десятичный произвольной разрядности.

Известен четырехразрядный преобра:зователь двоичного кода в двоичнодесятичный, содержащий сумматор и схему сравнения Ij.

Недостаток известного преобразователя .- низкая экономичность, связанная с большим потреблением тока и большой стоимостью ИС средней степени интеграции.

Наиболее близким к предлагаемому по технической сушности и схемному построению является четырехразрядный преобразователь двоичного кода в двоично-десятичный , содержащий шестнадцать элементов И-НЕ .

Недостаток данного преобразователя - большой объем аппара,туры и низкая экономичность.

Целью изобретения является упрощение преобразователя и повышение его экономичности.

Поставленная цель достигается тем, в четырехразрядный преобразователь двоичного кода в двоично-десятичный, содержащий семь элементов И-НЕ, причем входы первого и третьего разрядов преобразователя соединены соответственно с первыми входами первого и второго элементов И-НЕ, выходы которых соединены с входами третьего элемента И-НЕ, выход которого является выходом третьего разряда преобразователя, вход четвертого разряда которого соединен с вторым входом первого элемента И-НЕ, введены первый и второй элементы 2И-2ИЛИ-НЕ и элемент ИСКЛЮЧАЮЩЕЕ ИЛИ, первый вход которого соединен с входом первого разряда преобразователя и с первым входом первого элемента 2И-2ИЛИ-НЕ, выход которого соединен с вторым входом второго элемента И-НК и первым входом четвертого элемента И-НЕ второй вход которого соединен с выходом пятого элемента И-НЕ, а выход четвертого элемента И-НЕ является выходом четвертого, разряда преобразователя и соединен с вторым входом элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, выход которого является выходом первогоразряда преобразователя и соединен с первыми входами второго элемента , 2И-2ИЛИ-НЕ и шестого элемента И-НЕ,

второй вход которого соединен с вторым и третьим входами первого элемента 2И-2ИЛИ-НЕ и с входом третьего разряда преобразователя, вход четвертого разряда которогр соединен с первым и вторым входами пятбго элемента И-Н,Е и вторым входом второго элемента 2И-2ИЛИ-НЕ, тре,тий вход которого соединен с выходом .шестого элемента И-НЕ, а четвертые

0 входа первого и второго элементов 2И-2ИЛИ-НЕ соединены с входом второго разряда преобразователя, выход второго разряда которого соединен , с выходом седьмого элемента И-НЕ,

5 первый и второй входы которого соединены с выходом второго элемента 2И-2ИЛИ-НЕ. ,

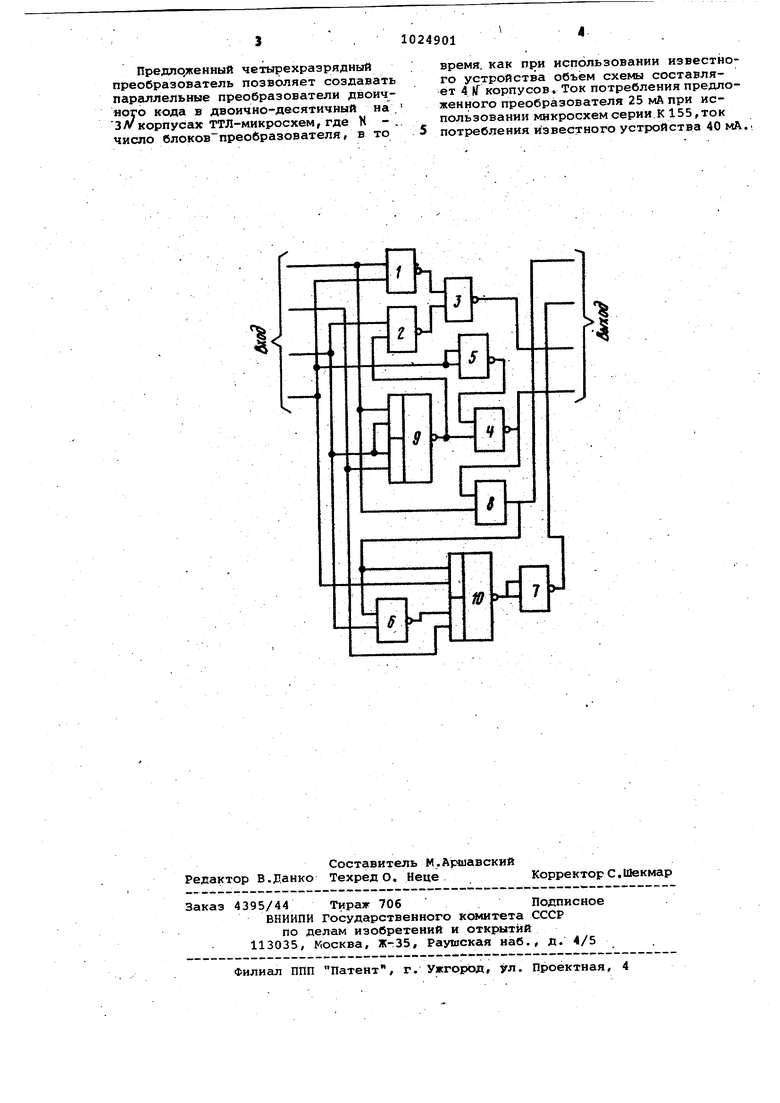

На чертеже приведена схема преобразователя .

Q Предлагаемое устройство содержит элементы И-НЕ 1 - 7 с первого поседьмой, элемент ИСКЛЮЧАЮЩЕЕ ИЛИ 8, первый элемент 2И-2ИЛИ-НЕ 9, второй элемент 2И-2ИЛИ-НЕ 10.

Преобразователь работает следующим образом,

Пусть а, Ь, с, d - значения разрядов входного числа, перечисленные в порядке возрастания значимости разрядов А, В, С, О - разряды выходного числа в том же порядке. Схема преобразователя реализует следующие логические функции

be + d;

+ ad;

+ aD;

В-b(Ac) + Ad.

0 .В случае замены четвертого элемента И-НЕ элементом ИСКЛЮЧАЮОЕЕ ИЛИ вид функции D меняется

О в acd + Ьс + abd + cd.

5 Непосредственная подстановка входных чисел от 0000 до 1001 убеждает в том, что в обоих случаях выполняется требуемое преобразование.

Предлагаемый преобразователь осуюествляет прямую передачу кода с входов на выходы/ если входное число меньше или равно 4, и приба:вляет к входному числу +3 в противном случае.

Четвертый, пятый и седьмой элементы И-НЕ или любая их комбинация могут быть заменены элементами ИСКЛЮЧАЮЩЕЕ ИЛИ, что может быть полезно для более компактного выполнения схемы преобразователя. При замене

0 пятого и седьмого элементов И-НЕ - на элементы ИСКЛЮЧАЮЩЕЕ ИЛИ входной сигнал подается на один вход элемента ИСКЛЮЧАЩЕЕ ИЛИ 8, а на второй ,его вход подается постоянное чение единица

Предложенный четырехразрядный преобразователь позволяет создавать параллельные преобразователи двончного кода в двоично-десятичный на . 3/V корпусах ТТЛ-микросхем, где К - .. число блоков преобразователя, в то

время, как при использовании известного устройства объём схемы составляет 4 ||Г корпусов. Ток потребления предложенного преобразователя 25 мА при использовании микросхем серии К 155,ток потребления известного устройства 40 мА,

| название | год | авторы | номер документа |

|---|---|---|---|

| Преобразователь двоично-десятичного кода в двоичный | 1980 |

|

SU930313A1 |

| Шифратор десятичного кода в двоичный код | 1990 |

|

SU1757105A1 |

| Преобразователь двоичного кода угла в двоично-десятичный код градусов и минут | 1983 |

|

SU1116425A1 |

| Преобразователь кода семисегментного индикатора в двоично-десятичный код | 1990 |

|

SU1743001A1 |

| Устройство для преобразования двоично-десятичного кода в двоичный | 1974 |

|

SU549801A1 |

| Преобразователь кода семисегментного индикатора в двоично-десятичный код | 1983 |

|

SU1112553A1 |

| Преобразователь двоично-десятичного кода в код семисегментного индикатора | 1983 |

|

SU1200275A1 |

| Преобразователь двоичного кода в двоично-десятичный | 1981 |

|

SU960794A1 |

| Шифратор двоично-десятичного кода | 1980 |

|

SU881731A1 |

| Преобразователь двоично-десятичного кода в семисегментный код | 1981 |

|

SU1005025A1 |

ЧЕТЫРЕХРАЗРЯДНЬгЙ ПРЕОБРАЗОВАТЕЛЬ ДВОИЧНОГО КОДА В ДВОИЧНОДЕСЯТИЧНЫЙ, содержащий смесь элементов 1I-HE., причем входы первого и третьего разрядов преобразователя соединены соответственно с первыми входакш первого и второго элементов И-НЕ, выходы которых соединены с входами третьего элемента И-НЕ, выход которого является выходсм третьего разряда преобразователя, вход четз&ертого разряда которого соединен с вторым входом первого элемента И-НЕ, отличающийся тем, что, с целью упрощения преобразователя и повышения его эиойомичности, в него введены первь1й и второй элементы 2И-2ИЛИ-ЯЕ и элемент ИСКЛЮЧАЮЩЕЕ ИЛИ, первый вход которого соединен с входом первого разряда преобразователя и с первым входом первого элемента 2И-2ИЛИ-НЕ, выход которого соединен с вторБ1М входом второго элемента И-НЕ и первым, входом четвертого элемента И-НЕ, второй вход которого соединен с выходом пятого элемента И-НЕ, а выход четвертого элемента И-НЕ является выходом четвертого разряда преобразователя и соединен со вторым входом элемента ИСКЛЮЧАЩЕЕ ИЛИ, выход которого является выходом первого разряда преобразователя и соединен с первыми входами второго элемента 2И-2ИЛИ-НЕ и шестого элемента И-НЕ, . второй вход которого соединен с вторым и третьим входами первого элемента 2И-2ИЛИ-НЕ и с входом третьего разряда преобразователя, вход четвертого разряда которого соединен с первым и вторым входами пятого элемента И-НЕ -и вторым входом второго элемента 2И-2ИЛИ-НЕ, третий вход которого соединен с выходом шестого элемента И-НЕ, а четвертые входы первого и второго элементов 2И-2ИЛИ-НЕ соединены с входом второего разряда преобразователя, выход второго разряда которого соединен с выходом седьмого элемента И-НЕ, первый и второй входы которого соединены с выходом элемента 2И-2ИЛИ-НЕ.

г1

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Ватнер X | |||

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Т | |||

| Устройство для устранения мешающего действия зажигательной электрической системы двигателей внутреннего сгорания на радиоприем | 1922 |

|

SU52A1 |

| Приспособление для получения кинематографических стерео снимков | 1919 |

|

SU67A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Проектирование аналого-цифровых систем на интегральных схемах | |||

| Под ред | |||

| Б.В.Шамрая | |||

| Л., Машиностроение 1976, с | |||

| Двухколейная подвесная дорога | 1919 |

|

SU151A1 |

Авторы

Даты

1983-06-23—Публикация

1981-08-21—Подача