(54) ПРЕОБРАЗОВАТЕЛЬ ДВОИЧНОГО КОДА В ДВОИЧНО1 . 2Изобретение относится к автоматике и цифровой вычислительной технике и может быть использовано при построении двоично-десятичных преобразователей в вычислительных машинах и . ;цифровых системах контроля и управ Ления.

Известен преобразователь двоичного кода в двоично-десятичный, содержащий сдвиговый регистр, дешифратор коррекции и блок коммута- : ции. 1.

Недостаток известного устройства состоит в низком быстродействии.

Наиболее близким к предлагаемому по технической сущности и схемному построению является преобразователь двоичного кода в двоично-десятичный, состоящий из последовательно соединенных преобразователей веса разрядов двоичного числа с повышением веса основания в десять раз и выводом четырех мЛадших разрядов двоично-десятичного числа с основанием, численно равным двоично-десятичному эквиваленту. Каждый преобразователь веса разрядов двоичного числа состоит из последовательна соединенных блоков, содержащих четырехразрядные ;сумматоры и схемы сравнения 21. . ДЕСЯТИЧНЫЙ

Недостаток данного преобразоватеLля состоит в аппаратурной избыточности.

Целью изобретения является упрощение преобразователя с сохранением его быстродействия.

Поставленная цель достигается тем, что S преобразователе двоичного кода в двоично-десятичный содержащем

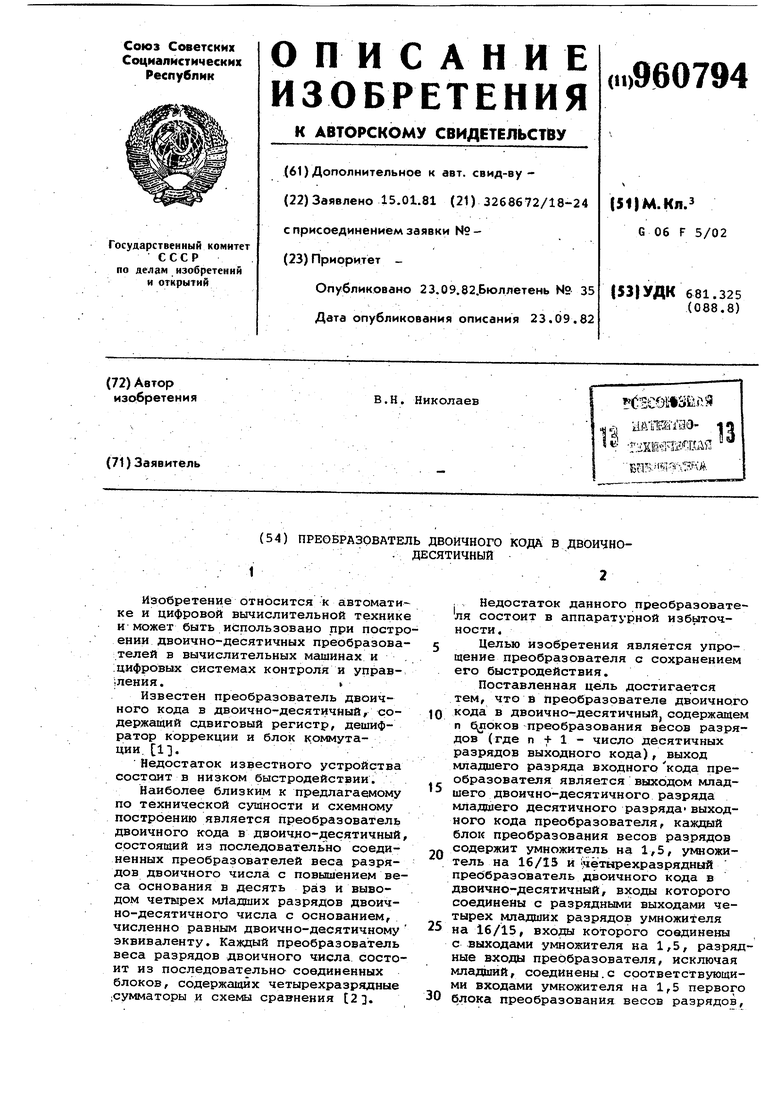

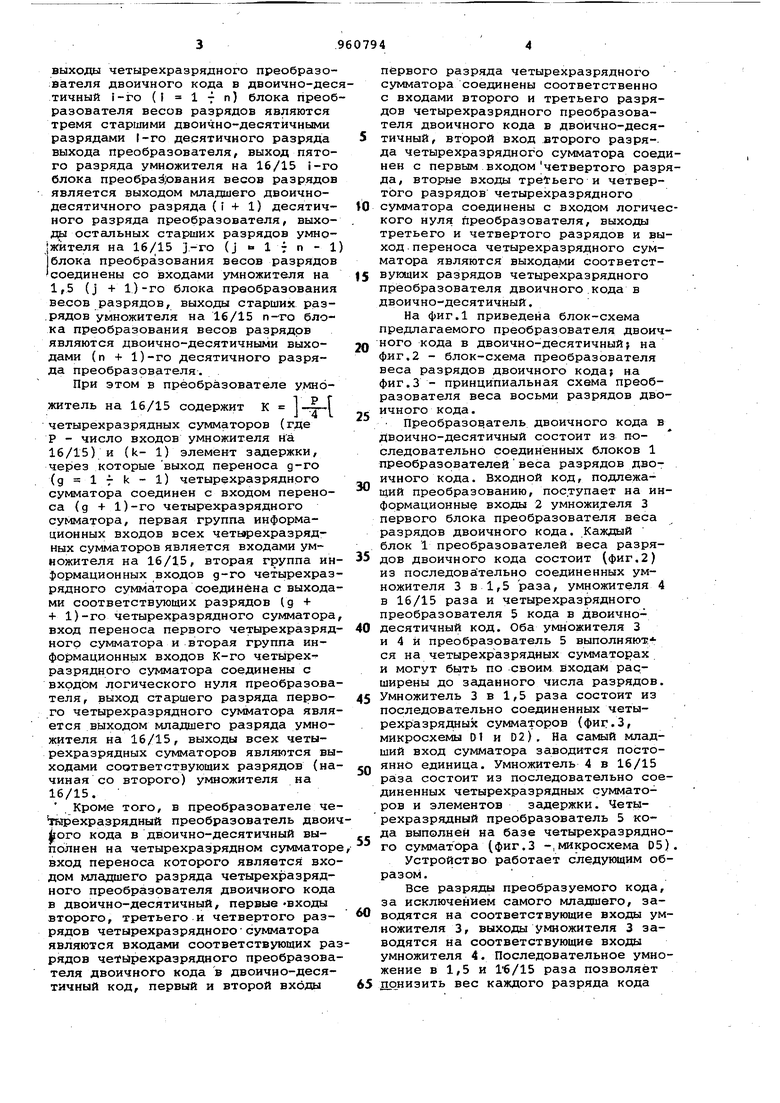

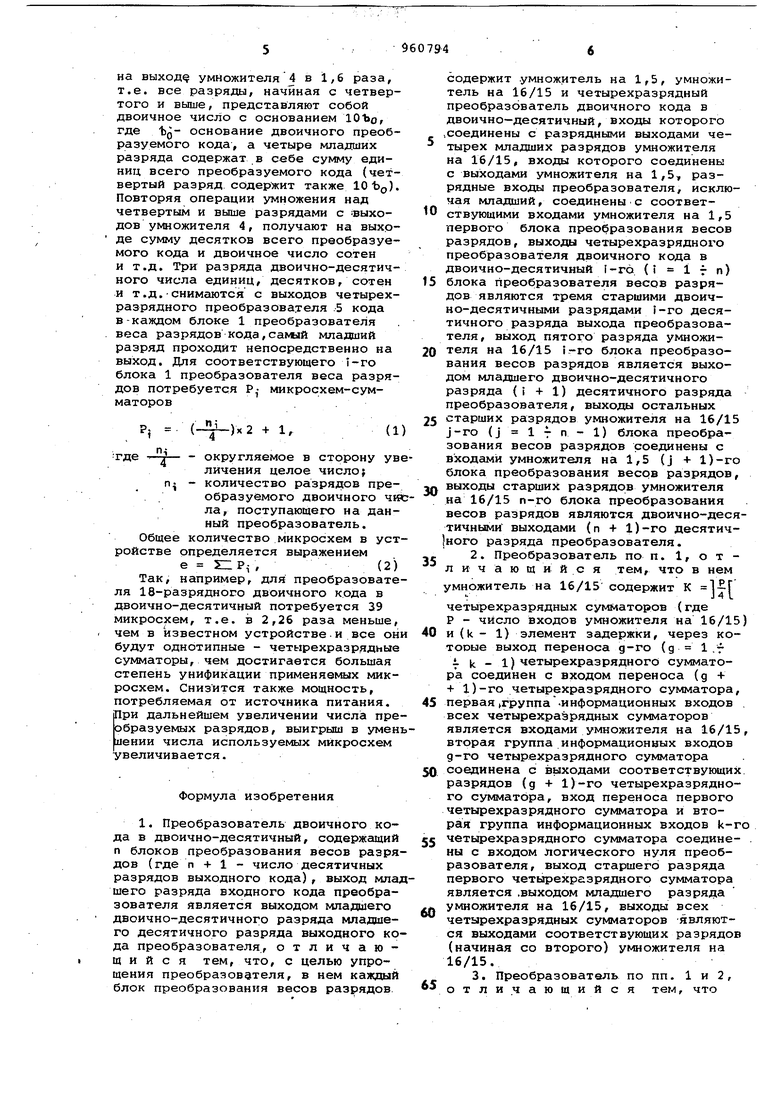

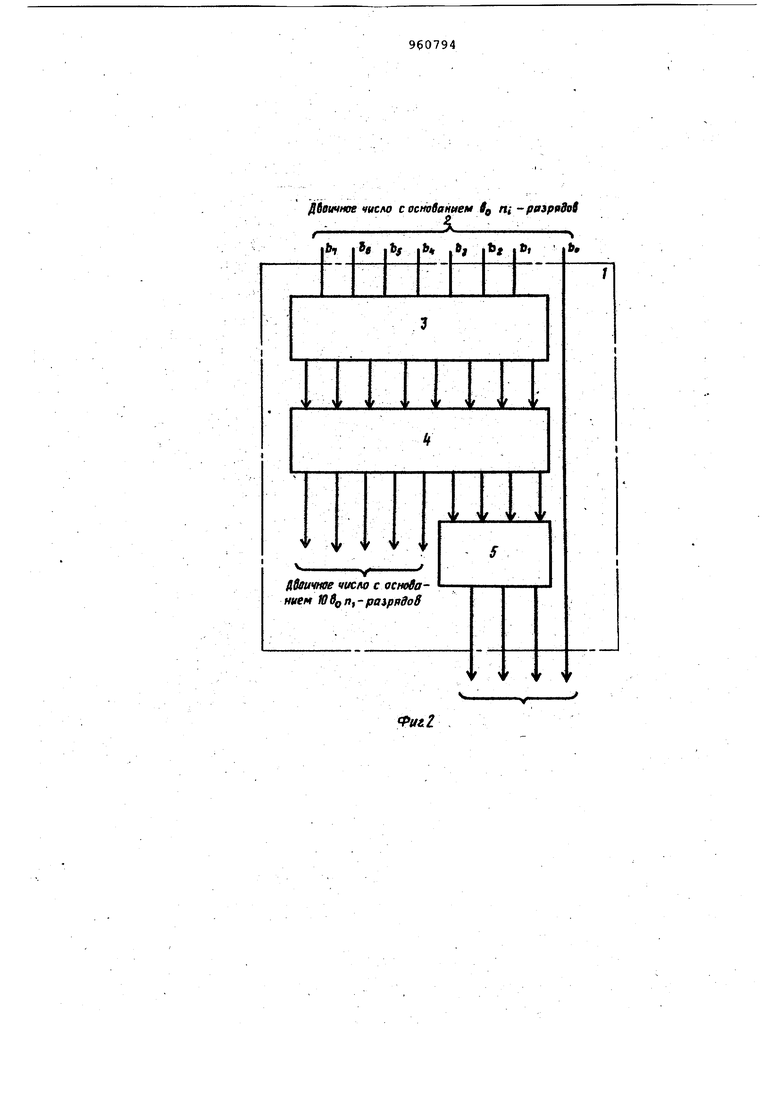

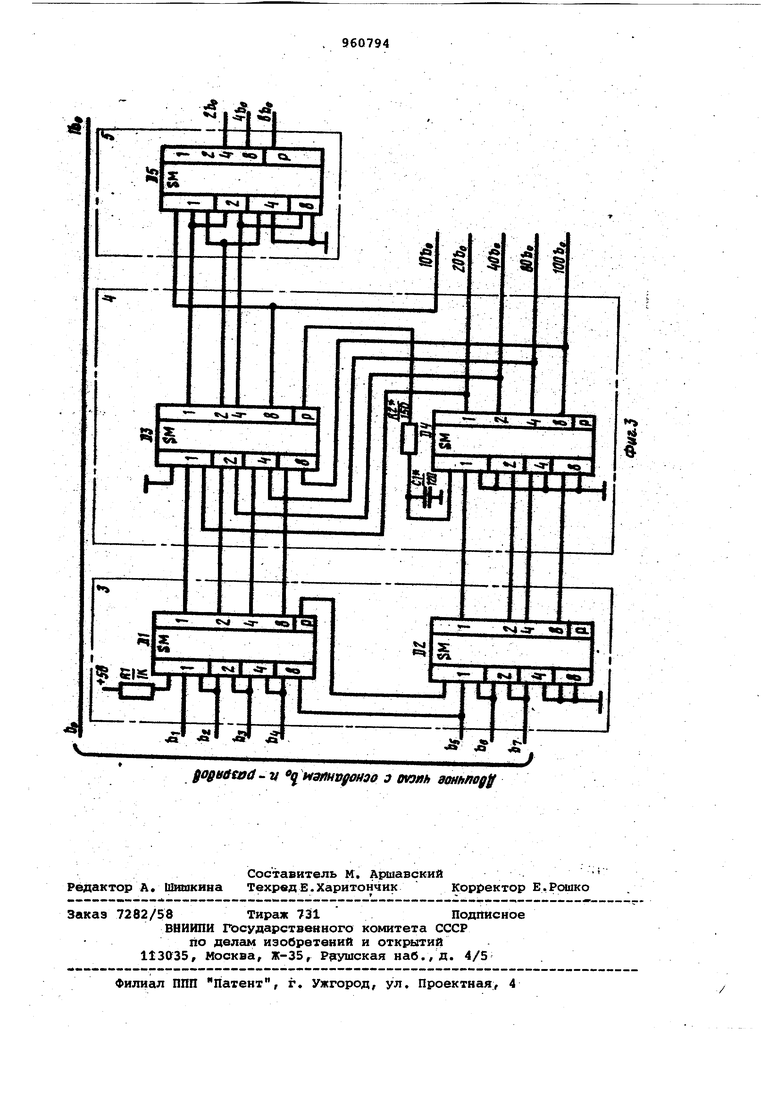

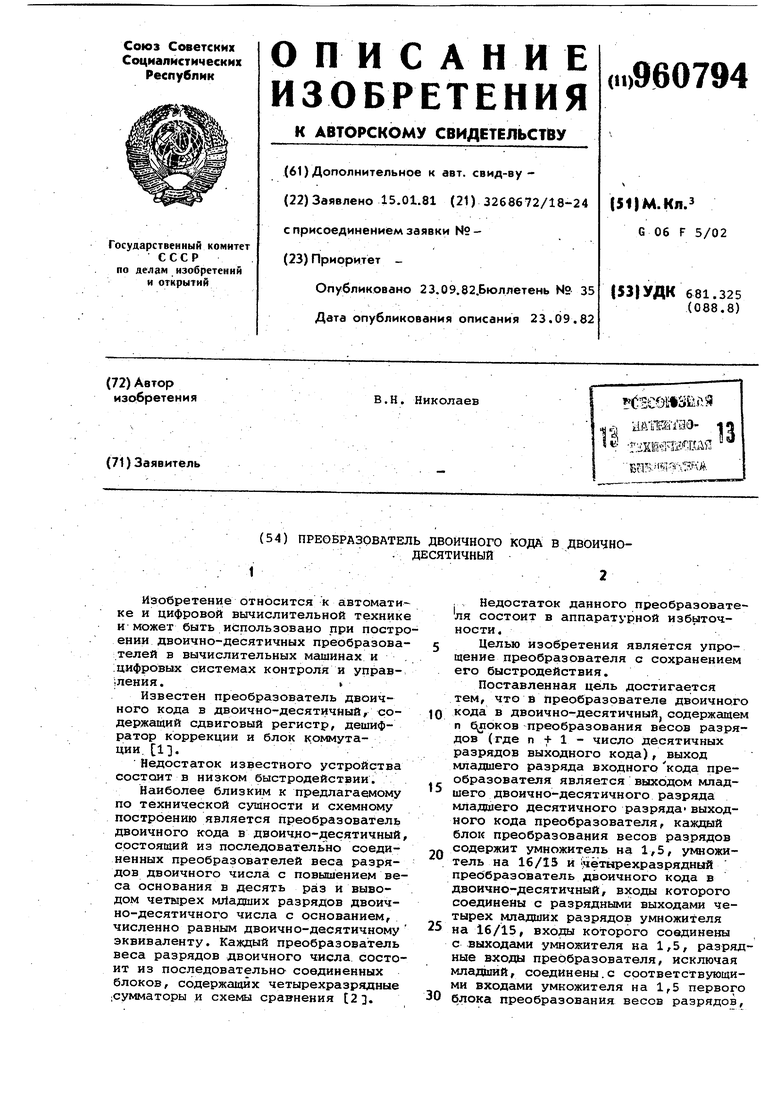

10 п оков преобразования весов разрядов (где п + 1 - число десятичных разрядов выходного кода), выход младшего разряда входногокода преобразователя является выходом млад15шего двоично-десятичного разряда младшего десятичного разряда-выходного кода преобразователя, каждый блок преобразования весов разрядов содержит умножитель на 1,5, умножи20тель на 16/15 и 1нётырехразрядный преобразователь двоичного кода в двоично-десятичный, входы которого соединены с разрядными выходами четырех младших разрядов умножителя 25 на 16/15, входы которого соединены с выходами умножителя на 1,5, разрядные входы преО бразователя, исключая младший, соединены.с соответствующими входами умножителя на 1,5 первого 30 блока преобразования весов разрядов. выходы четырехразрядного преобразователя двоичного кода в двоично-дес тичный i-ro () блока преоб разователя весов разрядов являются тремя старг шми двоично-десятичными разрядами 1-го десятичного разряда выхода преобразователя, выход пятого разряда умножителя на 16/15 i-ro блока преобрайрвания весов разрядов является выходом младшего двоичнодесятичного разряда ( i + 1) десятичного разряда преобразователя, выхода остальных старших разрядов умножителя на 16/15 j-ro (j « 1 7 п - 1 блока преобразования весов разрядов соединены со входами умножителя на 1,5 (j + 1)-го блока преобразования весов разрядов, выходы старших раз.рядов умножителя на 16/15 п-го блока преобразования весов разрядов являются двоично-десятичными выходами (п + 1)-го десятичного разряда преобразователя. При этом в преобразователе умножитель на 16/15 содержит К четырехразрядных сумматоров (где Р - число входов умножителя на 16/15) и (k- 1) элемент задержки, через которые выход переноса д-го () четырехразрядного сумматора соединен с входом переноса (д + 1)-го четырехразрядного сумматора, первая группа информационных входов всех четырехразрядных сумматоров является входами умножителя на 16/15, вторая группа ин формационных входов д-го четырехраз рядного сумматора соединена с выхода ми соответствующих разрядов (д + + 1)-го четырехразрядного сумматора вход переноса первого четырехразряд ного сумматора и вторая группа информационных входов К-го четырехразрядного сумматора соединены с входом логического нуля преобразова теля, выход старшего разряда первого четырехразрядного сумматора явля ется выходом младшего разряда умножителя на 16/15, выходы всех четырехразрядных сумматоров являются вы ходами соответствующих разрядов (на чиная со второго) умножителя на 16/15. Кроме того, в преобразователе че прехразрядный преобразователь двоич ioro кода в дв.оично-десятичный выполнен на четырехразрядном сумматоре вход переноса которого является входом младшего разряда четырехразрядного преобразователя двоичного кода в двоично-десятичный, первые -входы второго, третьего и четвертого разрядов четырехразрядногосумматора являются входами соответствующих раз рядов четырехразрядного преобразователя двоичного кода в двоично-десятичный код, первый и второй входы первого разряда четырехразрядного сумматора соединены соответственно с входами второго и третьего разрядов четырехразрядного преобразователя двоичного кода в двоично-десятичный, второй вход .второго разря-. да четырехразрядного сумматора соединен с первым входомчетвертого разряда, вторые входы третьего и четвертого разрядов четырехразрядного сумматора соединены с входом логического нуля преобразователя, выходы третьего и четвертого разрядов и выход переноса четырехразрядного сумматора являются выходами соответствующих разрядов четырехразрядного преобразователя двоичного.кода в двоично-десятичный. На фиг.1 приведена блок-схема предлагаемого преобразователя двоичного кода в двоично-десятичный} на фиг.2 - блок-схема преобразователя веса разрядов двоичного кода; на фиг.З - принципиальная схема преобразователя веса восьми разрядов двоичного кода. Преобразователь двоичного кода в Двоично-десятичный состоит из последовательно соединенных блоков 1 преобразователейвеса разрядов двоичного кода. Входной код, подлежащий преобразованию, поступает на информационные входы 2 умножи;геля 3 первого блока преобразователя веса разрядов двоичного кода. Каждый блок 1 преобразователей веса разрядов двоичного кода состоит (фиг.2) из последова тельно соединенных умножителя 3 в 1,5 раза, умножителя 4 в 16/15 раза и четырехразрядного преобразователя 5 кода в двоичнодесятичный код. Оба умножителя 3 и 4 и преобразователь 5 выполняют ся на четырехразрядных сумматорах, и могут быть по своим йходам расширены до заданного числа разрядов. Умножитель 3 в 1,5 раза состоит из последовательно соединенных четырехразрядных сумматоров (фиг.З, микросхекш D1 и D2). На самый младший вход сумматора заводится постоянно единица. Умножитель 4 в 16/15 раза состоит из последовательно соединенных четырехразрядных сумматоров и элементов задержки. Четырехразрядный преобразователь 5 кода выполнен на базе четырехразрядного сумматора (фиг.З -.микросхема D5). Устройство работает следующим образом. . Все разряды преобразуемого кода, за исключением самого младшего, заводятся на соответствующие входы умножителя 3, выходы умножителя 3 заводятся на соответствующие входы умножителя 4. Последовательное умножение в 1,5 и 16/15 раза позволяет принизить вес каждого разряда кода

в нем четырехразрядный преобразователь двоичного кода в двоично-десятичный выполнен на четырехразрядном сумматоре, вход переноса которого является входом младшего разряда четырехразрядного преоб{ азователя двоичного Кода в двоично -десятичный, первые входы второго, третьего и четвертого разрядов четырехразрядного сумматора являются вхоДс1Ми соответствующих разрядов четырехразрядного преобразователя двоичного кода , Двоично-десятичный код, первый и вгорой входы первого разряда четырехразрядного сумматора-соединены соответственно с входами второго и третьего разрядов четырехразрядноро преобразователя двоичного кода в двоично-десятичный, второй вход второго разряда четырехрядного сумматора сое-

Динен с первым входом четвертого разряда, вторые входы третьего и четвертого разрядов четырехразрядного сумматора соединены с входом логического нуля преобразователя., выходы третьего и четвертого разрядов и выход переноса четырехразрядного сумматора являются выходами соответствующих разрядов четырехразрядного преобразователя двоичного кода в двоично-десятичный.

Источники информации, принятые во внимание при экспертизе

1 Авторское свидетельство СССР №486314, кл. q 06 F 5/02, 1972.

2, Хаим Витнер. Преобразователь двоичного кода в двоично-десятичный на KlMOn ИС. - Электроника, 1979, № 10, том. 52.

| название | год | авторы | номер документа |

|---|---|---|---|

| Преобразователь последовательного двоичного кода в параллельный двоично-десятичный код | 1982 |

|

SU1084780A1 |

| Преобразователь двоичного кода в двоично-десятичный | 1984 |

|

SU1277402A1 |

| Преобразователь двоично-десятичного кода в двоичный | 1983 |

|

SU1095169A1 |

| Преобразователь двоично-десятичныхчиСЕл B дВОичНыЕ C МАСшТАбиРОВАНиЕМ | 1979 |

|

SU822173A1 |

| Преобразователь двоично-десятичного кода в двоичный | 1980 |

|

SU888104A1 |

| Преобразователь двоично-десятичного кода в двоичный | 1985 |

|

SU1292187A1 |

| Преобразователь двоичного кода в двоично-десятичный | 1978 |

|

SU771659A1 |

| Устройство для преобразования двоично-десятичных чисел в двоичные | 1988 |

|

SU1557680A2 |

| Преобразователь двоичного кода угла в двоично-десятичный код градусов,минут и секунд | 1980 |

|

SU955022A1 |

| Преобразователь двоичного кода вдВОичНО-дЕСяТичНый и дВОичНО-дЕСяТичНОгОВ дВОичНый | 1979 |

|

SU849197A1 |

Л, - разрядов

X

|| 144 1444444

X ф ф ф ф fU ф V V Ф

лг

/ ф Л1/

лг

ti:

f Л Ф 1г tf

Явоачну - decinnuvHffe число с основанием ЮЬ,

Ли

f

, Двоично-десятичное

vucflo с ocHotkoHueM

Цвоинно- десатичное число с основанием ЮООЪд

ф ф ф

Двоичт-десятичное число с основанием . 0

ф ф ф

fuz.1

ЦЬончное число состванаем 9g щ -разрядов

А ...

gogtaffod-v измпдйнэо з атяь аммоду

Авторы

Даты

1982-09-23—Публикация

1981-01-15—Подача