(5) ПРЕОБРАЗОВАТЕЛЬ ДВОИЧНО-ДЕСЯТИЧНОГО КОДА В ДВОИЧНЫЙ

| название | год | авторы | номер документа |

|---|---|---|---|

| Трехдекадный преобразователь двоично-десятичного кода в двоичный | 1980 |

|

SU943705A1 |

| Преобразователь двоично-десятичного кода в двоичный | 1981 |

|

SU1005027A1 |

| СПОСОБ И УСТРОЙСТВО УМНОЖЕНИЯ ДВОИЧНО-ДЕСЯТИЧНЫХ КОДОВ | 2008 |

|

RU2386998C1 |

| СПОСОБ И УСТРОЙСТВО СУММИРОВАНИЯ И ВЫЧИТАНИЯ ДВОИЧНО-ДЕСЯТИЧНЫХ КОДОВ | 2008 |

|

RU2389064C1 |

| Преобразователь целых комплексных чисел в двоичный код | 1980 |

|

SU962914A1 |

| СПОСОБ И УСТРОЙСТВО УМНОЖЕНИЯ ДВОИЧНО-ДЕСЯТИЧНЫХ КОДОВ | 2009 |

|

RU2410745C1 |

| Преобразователь целой части двоичного кода в двоично-десятичный | 1973 |

|

SU612240A1 |

| Преобразователь двоично-десятичного кода в двоичный | 1988 |

|

SU1554143A1 |

| Преобразователь двоично-десятичного кода в двоичный | 1984 |

|

SU1193824A1 |

| Устройство для сложения в двоичном избыточном коде | 1987 |

|

SU1413623A1 |

I

Изобретение относится к автоматике и цифровой технике и может быть использовано при построении преобра-, зователей в вычислительных устройствах и устройствах обработки данных.

Известен преобразователь двоичнодесятичного кода в двоичный код, содержащий шесть четырехразрядных сумматоров, расположенных в шесть ярусов 1 1.

Недостаток этого ареобразователя состоит в большом количестве аппара-туры и низком быстродейств ии.

Наиболее близким решением данной задачи по технической сущности и схемному построению является преобразователь двоично-десятичного кода в двоичный, содержащий четыре четырехразрядных сумматора, составляющих четыре яруса и элемент ИЛИ C2J

Недостаток известного преобразователя состоит в относительно низком быстродействии, связанным с большим количеством ярусов.

Цель изобретения - повышение быстродействия преобразователя.

Поставленная цель достигается тем, что в преобразователь двоичнодесятичного кода в двоичный, содержащий четыре четырехразрядных сумматора , причем вход первого разряда преобразователя соединен с выходом пер вого разряда преобразователя, входы второго и третьего разрядов преобразователя соединены соответственно с первыми входами первого и второго разрядов первого четырехразрядного сумматора, входы пятого, шестого и восьмого разрядов преобразователя соединены с вторыми входами соответ

. ственно первого и вто)эого разрядов и первым входом четвертого разряда первого четырехразрядного сумматора,

вь1ход первого разряда первого четыг рехразрядного сумматора являет-

,ся выходом второго разряда преобразователя, выходы второго, третьего и четвертого разрядов 3 первого четырехразрядного сумматора соединены соответственно с пер выми входами первого, второго и третьего разрядов второго четырехразрядного сумматора, выходы первог второго и третьего разрядов которог являются соответственно выходами третьего, четвертого и пятого разрядов преобразователя, выходы перво го, второго, третьего и четвертого разрядов третьего четырехразрядного сумматора являются соответственно выходами седьмого, восьмого, дев того и десятого разрядов преобразователя, вход девятого разряда преоб разователя соединен с первым входом первого разряда четвертого четырехразрядного сумматора , и вторым входом первого разряда второго четырехразрядного сумматора, введен пятый четырехразрядный сумматор, первые входы первого, второго, третьего и четвертого разрядов которого соединены соответственно с входами пятого, шестого, седьмого и восьмого разрядов преобразователя, вторые входы первого, второго и третьего разрядов пятого четырехразрядного сумматора соединены соответственно с входами десятого, одиннадцатого и двенадцатого разрядов преобр зователя, вход девятого разряда преобразователя соединен с первым входом четвертого разряда второго четырехразрядного сумматора, выход четверт го разряда которого является выходом шестого разряда преобразователя а выход переноса соединен с входом переноса третьего четырехразрядного сумматора, первые входы первого, . второго, третьего и четвертого разрядов которого соединены с выходами соответствующих разрядов четвертого

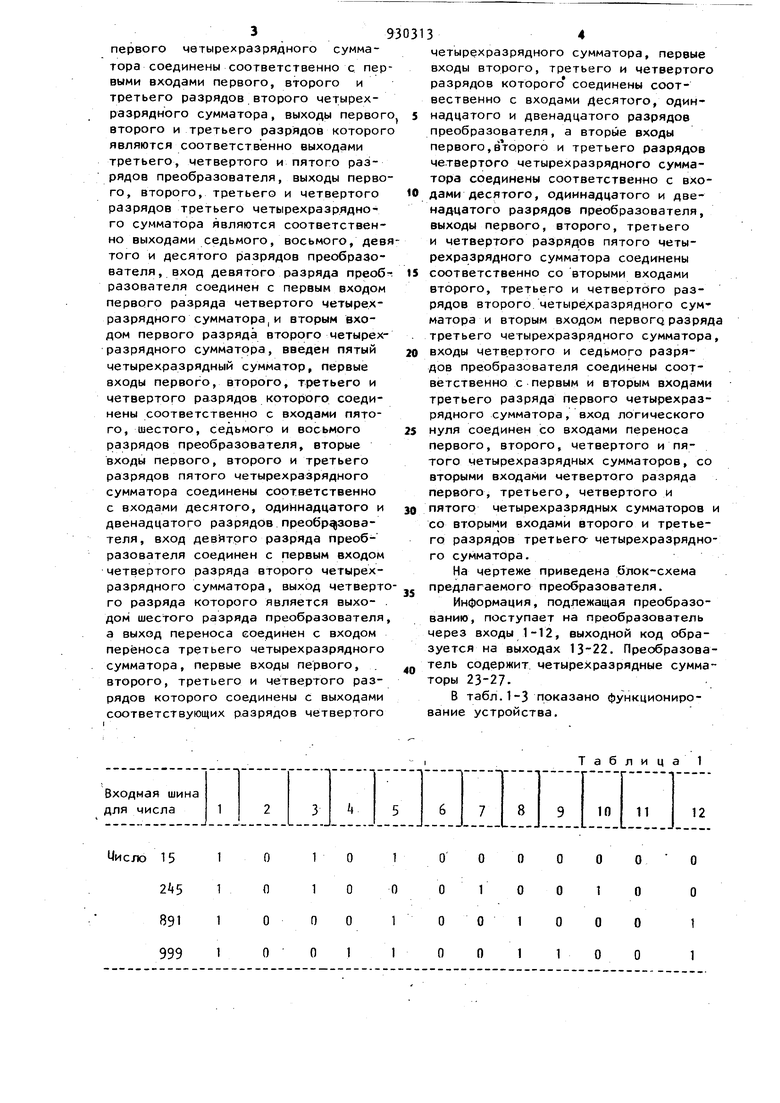

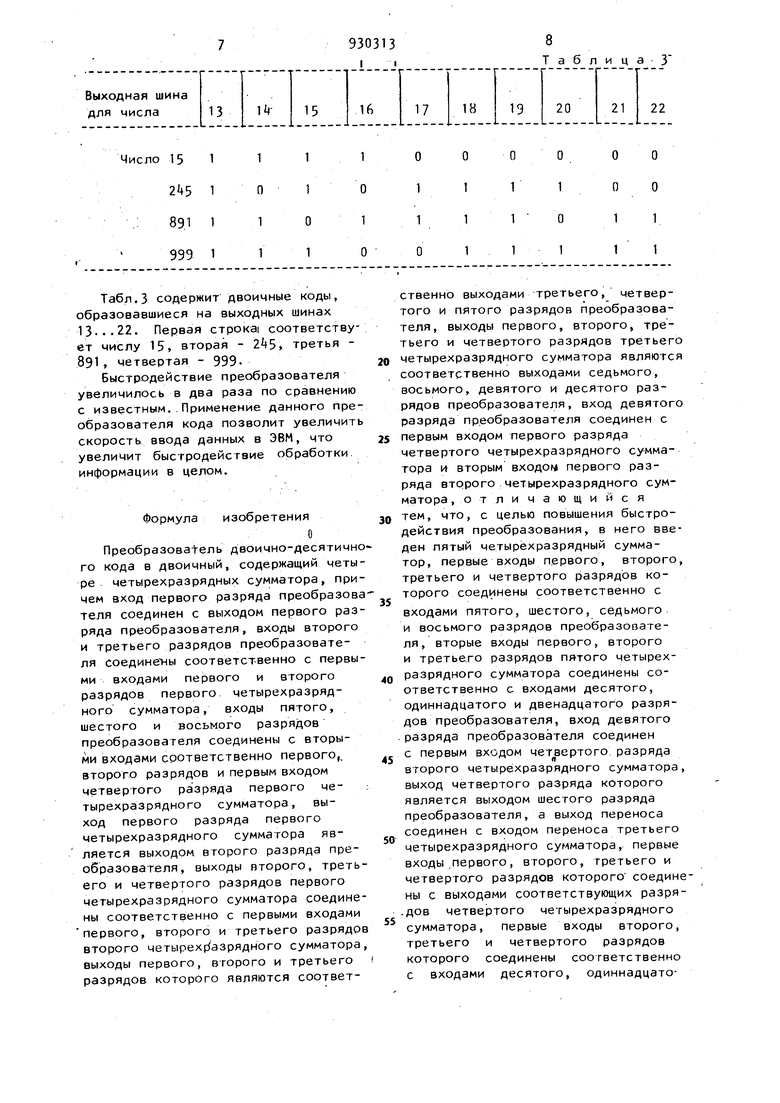

Число 15 2.5 891 999

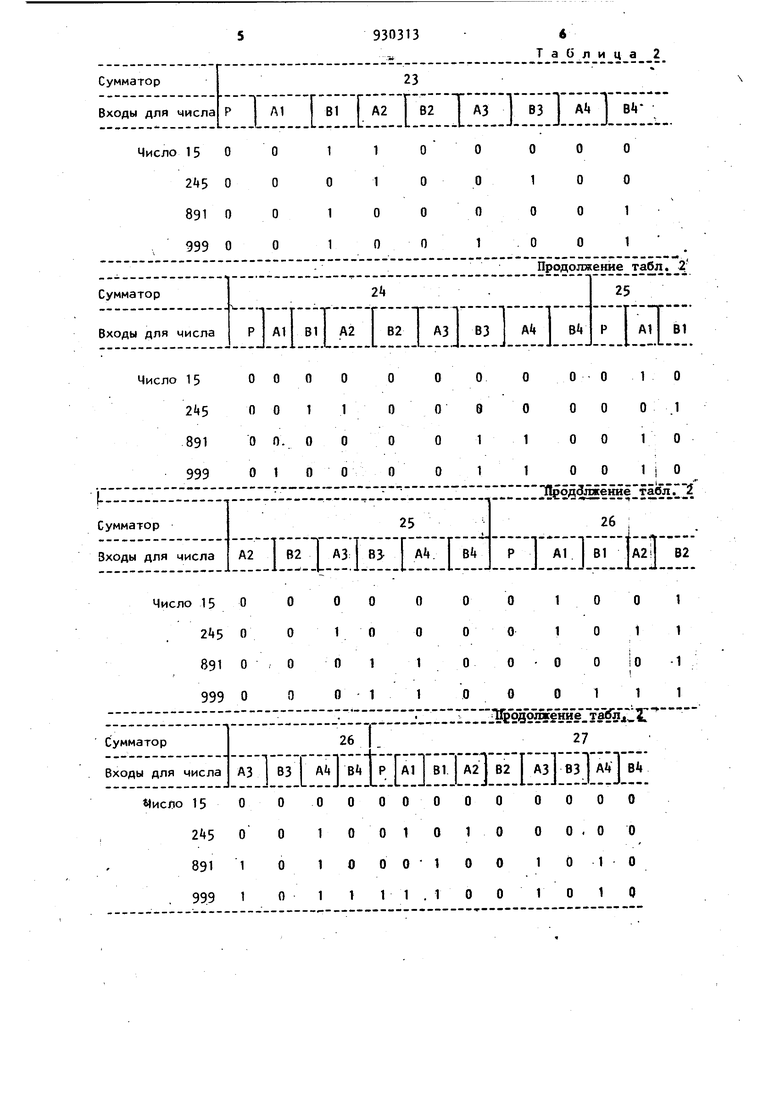

Таблица 1 4 четырехразрядного сумматора, первые входы второго, третьего и четвертого разрядов которого соединены соотвественно с входами Десятого, одиннадцатого и двенадцатого разрядов преобразователя, а вторые входы первого,второго и третьего разрядов четвертого четырехразрядного сумматора соединены соответственно с входами десятого, одиннадцатого и двенадцатого разрядов преобразователя, выходы первого, второго, третьего и четвертого разрядов пятого четырехразрядного сумматора соединены соответственно со вторыми входами второго, третьего и четвертого разрядов второго, четыре сразрядного сумматора и вторым входом nepBorq разряда третьего четырехразрядного сумматора, входы четвертого и седьмого разрядов преобразователя соединены соответственно с первым и вторым входами третьего разряда первого четырехразрядного сумматора, вход логического нуля соединен со входами переноса первого, второго, четвертого и пятого четырехразрядных сумматоров, со вторыми входами четвертого разряда первого, третьего, четвертого и пятого четырехразрядных сумматоров и со вторыми входами второго и третьего разрядов третьего- четырехразрядного сумматора. На чертеже приведена блок-схема предлагаемого преобразователя. Информация, подлежащая преобразованию, поступает на преобразователь через входы 1-12, выходной код образуется на выходах . Преобразователь содержит четырехразрядные сумматоры 23-27. В табл.1-3 показано функционирование устройства.

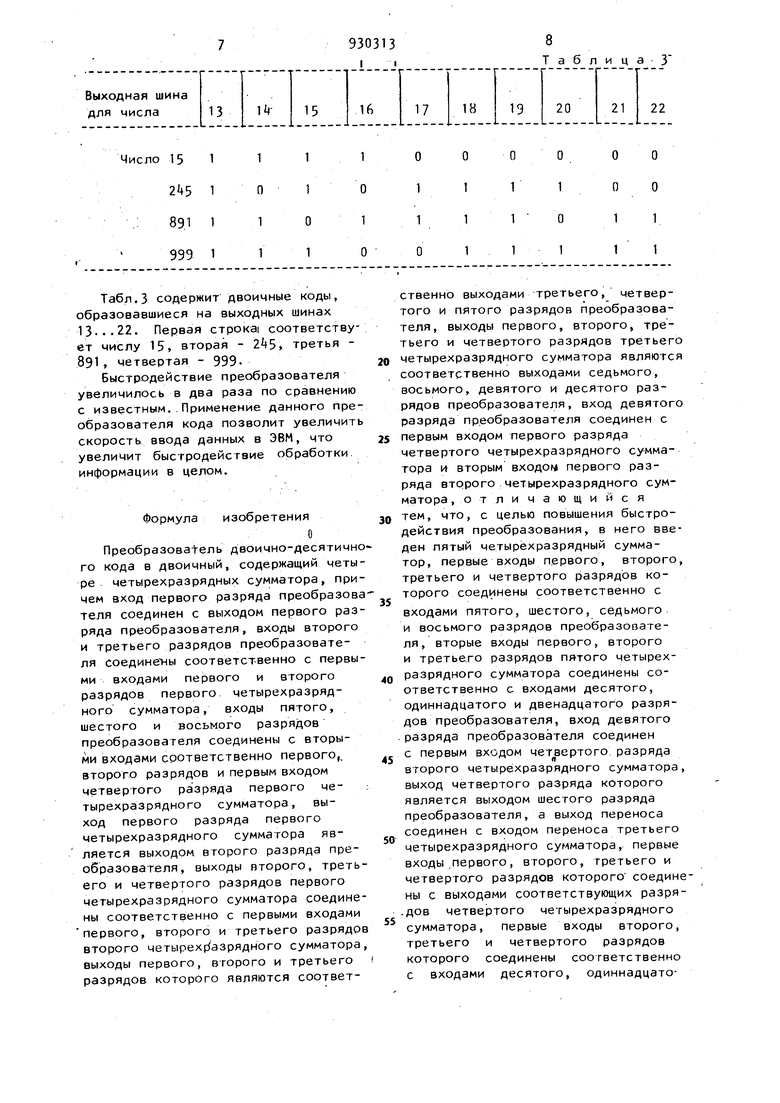

Таблица 2 Табл.3 содержит двоичные коды, образовавшиеся на выходных шинах 13...22. Первая строка соответству ет числу 15, вторая - 2kS, третья 891, четвертая - 999Быстродействие преобразователя увеличилось в два раза по сравнению с известным..Применение данного пре образователя кода позволит увеличит скорость ввода данных в ЭВМ, что увеличит быстродействие обработки информации в целом. Формула изобретения Преобразователь двоично-десятичн го кода в двоичный, содержащий четы ре, четырехразрядных сумматора, при чем вход первого разряда преобразов теля соединен с выходом первого раз ряда преобразователя, входы второго и третьего разрядов преобразователя соедине 1ы соответственно с первы ми входами первого и второго разрядов первого, четырехразрядного сумматора, входы пятого, шестого и восьмого разрядов преобразователя соединены с вторыми входами соответственно первого,, второго разрядов и первым входом четвертого разряда первого четырехразрядного сумматора, выход первого разряда первого четырехразрядного сумматора является выходом второго разряда преобразователя, выходы второго, треть его и четвертого разрядов первого четырехразрядного сумматора соедине ны соответственно с первыми входами первого, второго и третьего разрядо второго четырехр/азрядного сумматора выходы первого, второго и третьего разрядов которого являются соответТаблицаЗственно выходами третьего, четвертого и пятого разрядов преобразователя, выходы первого, второго, третьего и четвертого разрядов третьего четырехразрядного сумматора являются соответственно выходами седьмого, восьмого, девятого и десятого разрядов преобразователя, вход девятого разряда преобразователя соединен с первым входом первого разряда четвертого четырехразрядного сумматора и вторым входом первого разряда второго , четырехразрядного сумматора, отличающийся тем, что, с целью повышения быстродействия преобразования, в него введен пятый четырёхразрядный сумматор, первые входы первого, второго, третьего и четвертого разрядов которого соединены соответственно с входами пятого, шестого, седьмого и восьмого разрядов преобразователя, вторые входы первого, второго и третьего разрядов пятого четырехразрядного сумматора соединены соответственно с входами десятого, одиннадцатого и двенадцатого разрядов преобразователя, вход девятого разряда преобразователя соединен с первым входом четвертого разряда второго четырёхразрядного сумматора, выход четвертого разряда которого является выходом шестого разряда преобразователя, а выход переноса соединен с входом переноса третьего четырехразрядного сумматора, первые входы .первого, второго, третьего и четвертого разрядов которого соединены с выходами соответствующих разрядов четвертого четырехразрядного сумматора, первые входы второго, третьего и четвертого разрядов которого соединены соответственно с входами десятого, одиннадцато993031

го и двенадцатого разрядов преобразователя, а вторые входы первого, второго и третьего разрядов : четвертого четырехразрядного сумматора соединены соответственно с входа- j ми десятого, одиннадцатого и двенадцатого разрядов преобразователя, выходы первого, второго, третьего и четвертого разрядов пятого четырехразрядного сумматора соединены соот- to ветственно со вторыми входами -второго, третьего и четвертого разрядов второго четырехразрядного сумматора и вторым входом первого разряда третьего четырехразрядного сумматора, |5 входы четвертого и седьмого разрядов преобразователя соединены соответственно с первым и вторым входами

3 10

третьего разряда первого четырехразрядного сумматора, вход логического нуля соединен со входами переноса первого, второго, четвертого и пятого четырехразрядных сумматоров, со вторыми входами четвертого разряда пеового, третьего, четвертого и пятого четырехразрядных сумматоров и со вторыми входами второго и третьего разрядов третьего четырехразрядного сумматора.

Источники информации, принятые во внимание при экспертизе1,Патент США If 3705299, кл. 235-155, опублик, 19732.Авторское свидетельство СССР по заявке N 27285 7/2,

кл. G 06 F 5/02, 23.02.79 (прототип)

Авторы

Даты

1982-05-23—Публикация

1980-08-21—Подача