t

Изобретение относится к области цифровой вычислительной техники и может быть использовано для аппаратной реализации операций вычисления экспоненциальной функции и ее квадрата.

Известно устройство для вычисления экспоненциальной функции по автор.евид. № 538366, содержащее блок управления, выходы которого соединены с управляющими входами накопительных и сдвигающего регистров и входом блока односторонней памяти, выходы накопительных регистров соединены со входами одноразрядных сумматоров-вычитателей, выходы которых соединены со входами накопительных регистров, выход одного накпительного регистра соединен со входом блока определения псевдочастного, выход которого соединен с управляющим входом одного из одноразрядных сумматоров-вычитателей, устройство содержит также блок повторения операций, блок сброса, блок анализа сходимости, вентили, одни входы которых соединены с выходом блока определения псевдочастного, другие входы которых соединен

с выходами блока односторонней памяти, а выходы вентилей соединены со входом одноразрядного сумматоравычитателя, причем вход блока анализа сходимости соединен с выходом соответствующего накопительного регистра, а выход - со входом блока сброса, выход которого соединен с одним входом блока управления, дру0гие вход и выход которого соединены с блоком повторения операций 1,

Недостатком его является невозможность вычисления квадрата экспоненциальной функции. Целью изобре5тения является обеспечение возможности вычисления квадрата экспоненциальной функции. Цель достигается тем, что устройство содержит третий и четвертый сумматоры, вычитатели,

0 блок сдвига и третий накопительный регистр, первый выход которого соединен с первым входом третьего сумматора-вычитателя, выход которого соединен с первым входом третьего нако5пительного регистра, второй вход которого соединен с-шестым вых дом блока управления, седьмой выход которого соединен с первым входом блока сдвига, информационные входы кото0

рого соединены с информационными выходами иакогштельного регистра, выходы блока сдвига соединены с первым и вторым входам-1 четвертого cyiMMaтора-вычитателя, третий вход которого соединен с выходом блока определения энаксг, выход - со вторым входом третьего сум татора-вычитателя.

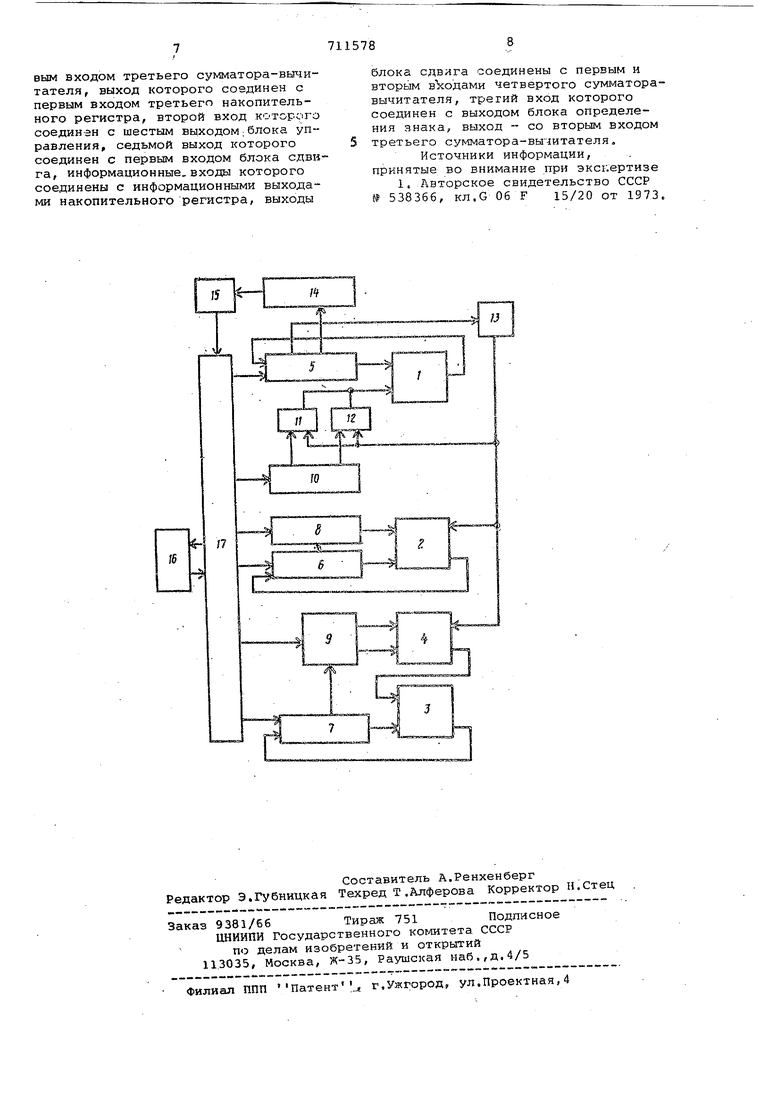

На .чертеже представлена блоксхема устройства для вычисления экспоненциальной функции.

Устройство Содержит одноразрядные сумматоры-вычитатели 1-4 комбинационного типа, накопительные регистры 5-7, сдвигающий регистр 8, блок сдвига 9,выполненный, например, на двух Сдвигающих регистрах, блок односторонней памяти 10, выполненного с поразрядной, выборкой двух констант 6i (1 + 2 Ми 2л . (1-2 ). одновременно, элементы И 11-12, блок определения знака 13, выполненный в виде триггера и логических элементов, блок анализа сходимости 14, выполненный в виде цифровой схемы сравнения, блок сброса 15, выполненкшлй в виде триггера и логических эле5.йэатов, блок повторения итераций 16, выполненный в виде счетчика и логических элементов, блок управления 17 состояспий . из генератора тактовых импульсов, счетчиков, логических элементов и т.п. Выходом устройства являегся вход первого накопительного 5 егястра 5, выходом устройства являзвтся для экспоненциальной функции вкход второго накопительного пегистра, 6 для квадрата экспоненциальной функции - выход третьего накопительного регистра 7,

Вычисление экспоненциальной функции и ее квадрата в предложенном устройстве для интервала изменения аргумента основано на параллельном решении в итерационном процессе разностных рекуррентных соотношений, например, для двоичной системы счисления:

Z,-X 2j-««(l(j-2 - ) Z,0

n Sirrn 7- - J + 1 при „ , t-1 npHZj 0 J-o/i--

+ . n/X

e

Uo-1 Uj,yi i-Uj+c j.Uj.2-VUj.2

:Un-e«

Каждое рекуррентное соотношение вычисляется последовательно за (n+m тактов , где п -число разрядов аргументов, m - число дополнительных (зщитных) разрядов дпя компенсации усчения чисел при сдвиге. Так как ристема базисных функций W(. ; не удовлетворяет условиям сходимост .(исправляемости итераций) для цифр

оператора

.i-i:.

(i-2)2.en()

5 (,,e.{V2TO чтобы избежать появления зринесходимости на интервале изменения аргумента , необходимо и достаточно повторить по два раза все итерации, либо только 3,5,7 и т.д. итерации, либо 4,,16 и т.д. В последующих случаях время вычисления сокращается.

В начальном состоянии в накопительный регистр 5 заносится заданный аргумент X; накопительные регистры 6-7, сдвигающий регистр 8 и блок сдвига 9 устанавливаются в единичные состояния.

Вычисления в любой j -и итерации в описываемом устройстве выполняются следующгм образом,

С выходов блокауправления 17 выдаются импульсы для свдига содержаний в сдвигающем регистре 8 и блок сдвига 9, затем подается серия (последовательность) тактовых импульсов для продвижения содержаний накопительных и сдвигающего регистров 5-8, блока сдвига 9 и очередной константы

&1 (l+(:j,..2O-1-0 из блока односторонней памяти 10 на соответствующие входы сумглаторов-вычитателей 1-4 С выхода сдвигающего регистра 8 на второй вход сумматора-вычитателя 2 подается значение у-, 2.( Со второго выхода третьего накопительного регистра 7 на -первый вход блока сдвига 9 подается величина

(Jj , с первого выхода блока сдвига 9 на первый вход сумматора-вычи.тателя 4 подается значение Uj 2 v , со второго выхода на второй вход - значение Uj 2 i Алгебраическая сумма этих значений подается на второй вход сумматора-вычитателя 3. Результаты алгебраического суммирования-вычитания с выходов сумматороввычитателей 1-3 заносятся младшими разрядами вперед в освобождающиеся при сдвиге старщие разряды накопительных регистров 5-7 и продвигаются к их началу. После окончания итерации в накопительных регистрах 5-7 содержатся промежуточные результаты, которые передаются из накопительного регистра б в сдвигаюоий регистр 8, а из накопительного регистра 7 в блок сдвига 9. По знаку содержания накопительного регистра 5 в блоке определения знака43 формируется сигнал О: + i при положительном содержании накопительного регистра 5, или QJ -J при отрицательном содержании накопительного регистра 5. В первом случае суммато1)ы-вычитатели, 2 и 4 работают в режиме сложения по вторым входам, а с блока односторонней памяти 10 через элемент И 11 на второй вход сумматора-вычитателя 1 подается константа еп({ ) . во втором случае сумматоры-вычитатели 2 и 4 работают в режиме вычитания, а на сумматор-вычитатель 1 подается, чере элемент И 12 константа rf(-24 i /.

Вычисления в следующих итерациях .происходят аналогичным образом.

Блок повторения итераций 16 не изменяет номерj итерации, следующих за повторяемыми итерациями. В повторяемой итерации участвует предыдущая константа (с учетом нового значения оператора а,- , значения Vj и Uj дсвигаются на прежнее число разрядов.

После выполнения (п+1) итераций ,или при равенстве нулю содержания накопительного регистра 5 (в последнем случае с выхода блока анализа сходимости 14 через блок сброса 15 на блок управления 17 вьщается сигнал останов и последний прекращает выдавать тактовые импульсы на следующей итерации) процесс вычисления закончен. В накопительном

регистре б содержится значение экспоненциальной функции ( е ) , в накопительном регистре 7 - значение квадрата экспоненциальной функции ().

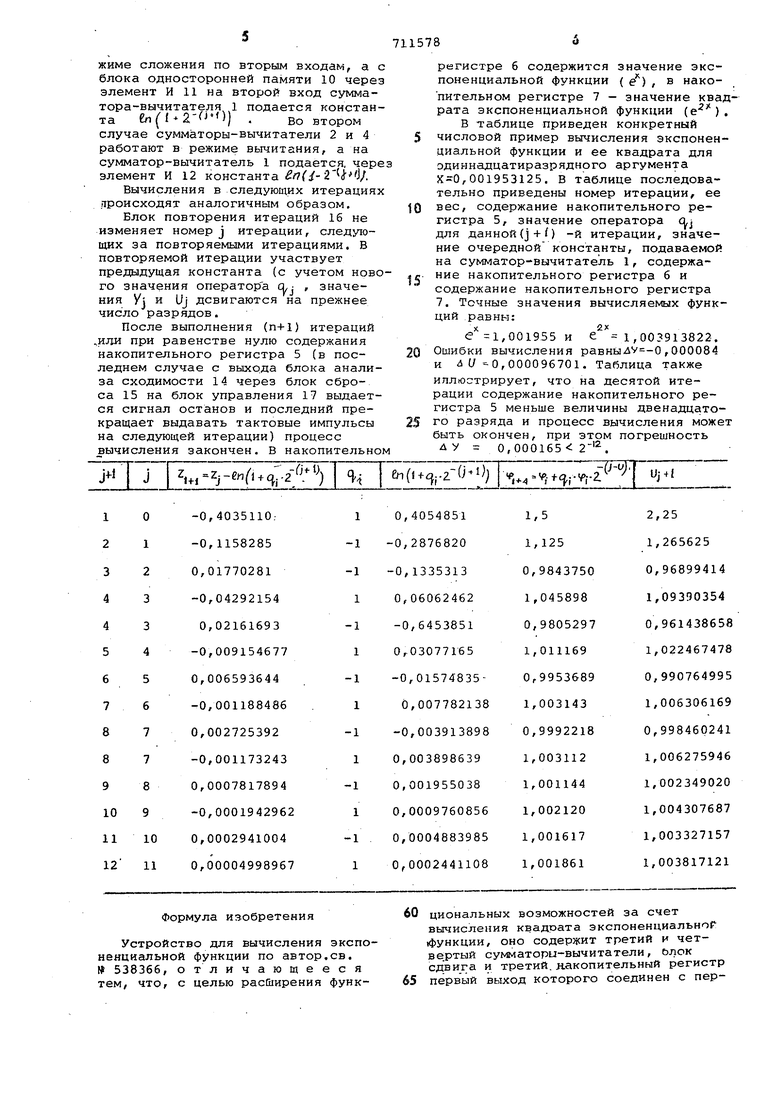

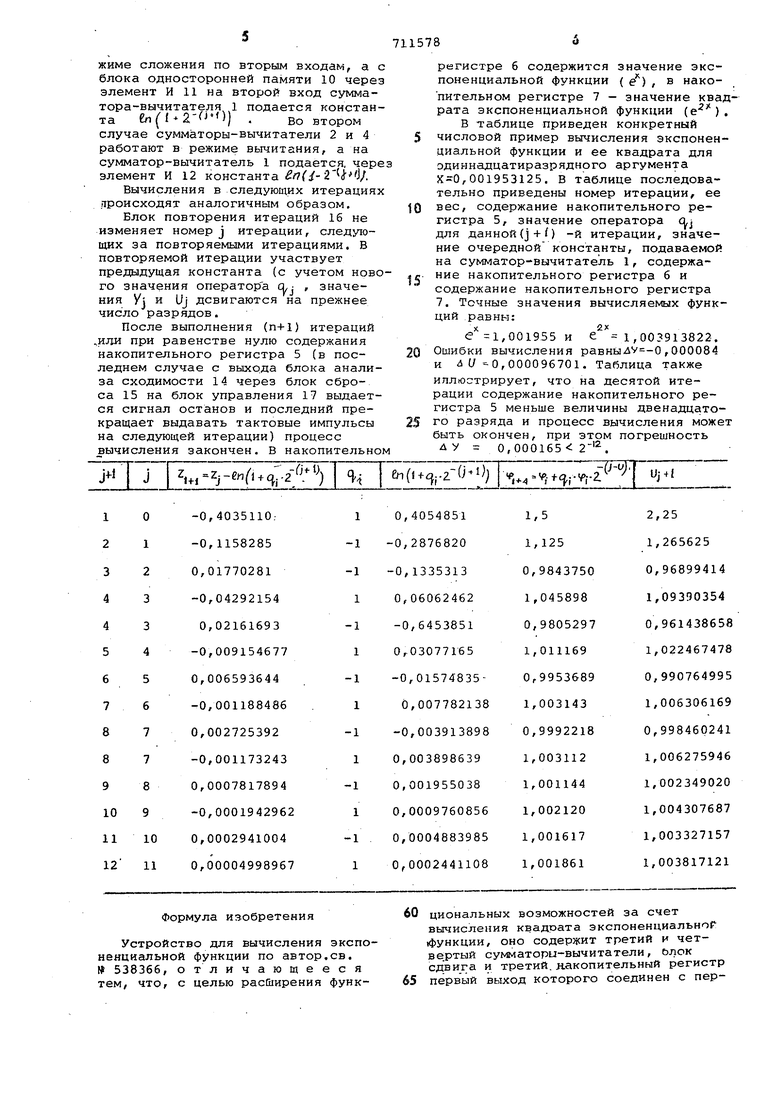

В таблице приведен конкретный 5 числовой пример вычисления экспоненциальной функции и ее квадрата для одиннадцатиразряднрго аргумента ,001953125. В таблице последовательно приведены номер итерации, ее 0 вес, содержание накопительного регистра 5, значение оператора для данной( + 0 -и итерации, значение очередной константы, подаваемой на сумматор-вычитатель 1, содаржас. ние накопительного регистра 6 и

содержание накопительного регистра 7. Точные значения вычисляемых функций равны:

X2х

е 1,001955 и е 1,003913822. 0 Ошибки вычисления равны4У -о,000084 и 4f -0,000096701. Таблица также иллюс:трирует, что на десятой итерации содержание накопительного регистра 5 меньше величины двенадцатого разряда и процесс вычисления может быть окончен, при этом погрешность Д V 0,000165 .

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для вычисления логарифмической функции | 1973 |

|

SU541167A1 |

| Устройство для вычисления экспоненциальной функции | 1973 |

|

SU538366A1 |

| Устройство для вычисления гиперболического тангенса | 1973 |

|

SU526890A1 |

| Устройство для вычисления гиперболических синуса и косинуса | 1973 |

|

SU536490A1 |

| Устройство для вычисления тригонометрического тангенса | 1973 |

|

SU537344A1 |

| Устройство для вычисления кубического корня | 1973 |

|

SU516037A1 |

| Устройство для извлечения корня третьей степени из частного и произведения | 1976 |

|

SU607214A1 |

| Цифровой функциональный преобразователь | 1980 |

|

SU922760A2 |

| Цифровой функциональный преобразователь | 1976 |

|

SU748434A1 |

| Цифровой функциональный преобразователь | 1975 |

|

SU599265A1 |

Формула изобретения

Устройство для вычисления экспоненциальной функции по автор.св. № 538366, отличающееся тем, что, с целью расширения функциональных возможностей за счет вычисления квадрата экспоненциально (функции, оно содержит третий и четвертый сумматори-вычитатели, ьлок сдвига и третий, накопительный регистр первый выход которого соединен с первым входом третьего сумматора-вычитателя, выход которого соединен с первым входом третьего накопительного регистра, второй вход которого соединен с шестым выходом;блока управления, седьмой выход которого соединен с первым входом блока сдвига, информационные, входы которого соединены с информационными выходами накопительного регистра, выходы

блока сдвига соединены с первым и BTOptJiM вЪ:одами четвертого сумматоравычитателя, третий вход которого соединен с выходом блока определения знака, выход -- со вторым входом третьего cy мaтopa-вы-Iитaтeля,

Источники информации, принятые во внимание при экспертизе

Авторы

Даты

1980-01-25—Публикация

1977-04-07—Подача