Изобретение относится к вычислительной технике и автоматике и может быть использовано для автоматического контроля исправности цифровых интегральных схем.

Цель изобретения - расширение функциональных возможностей путем обеспечения возможности контроля логических блоков, различных по расположению выводов «земля и «питание.

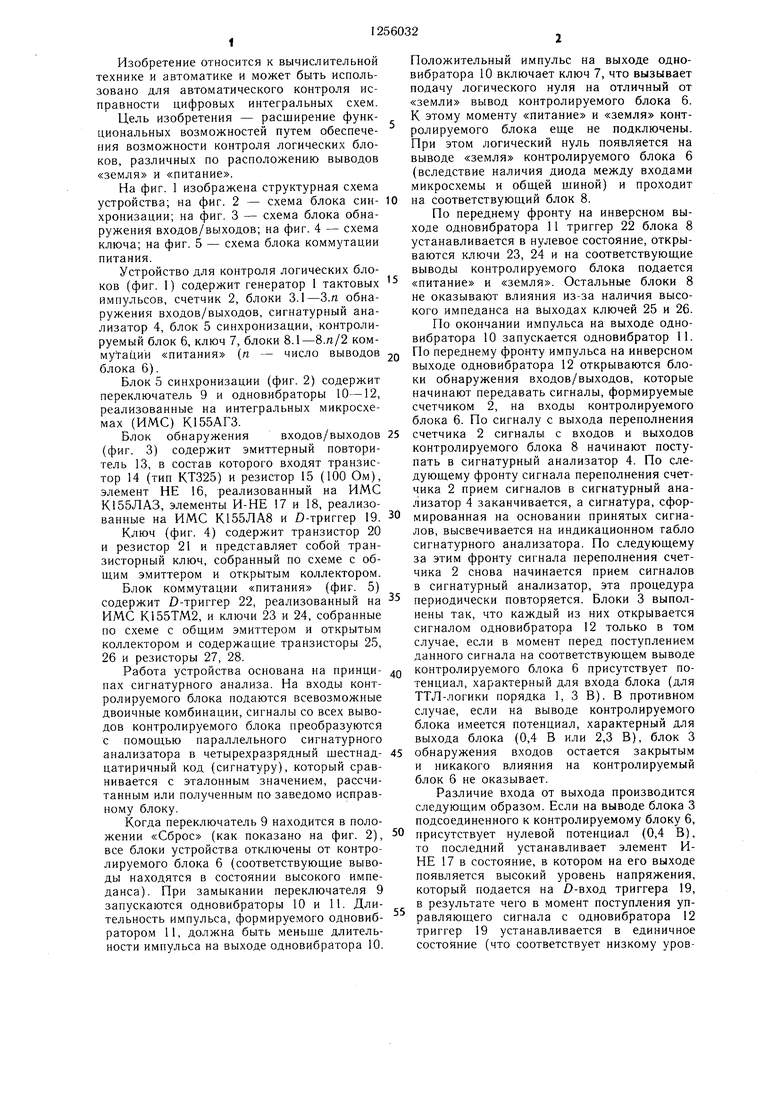

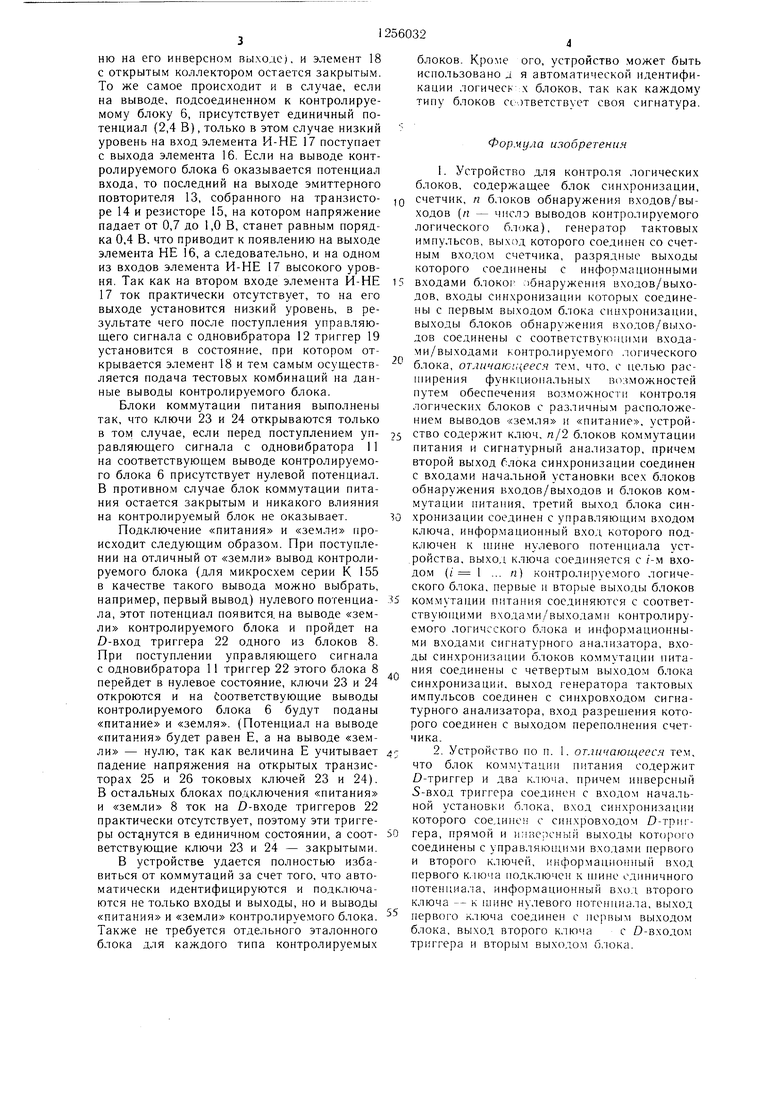

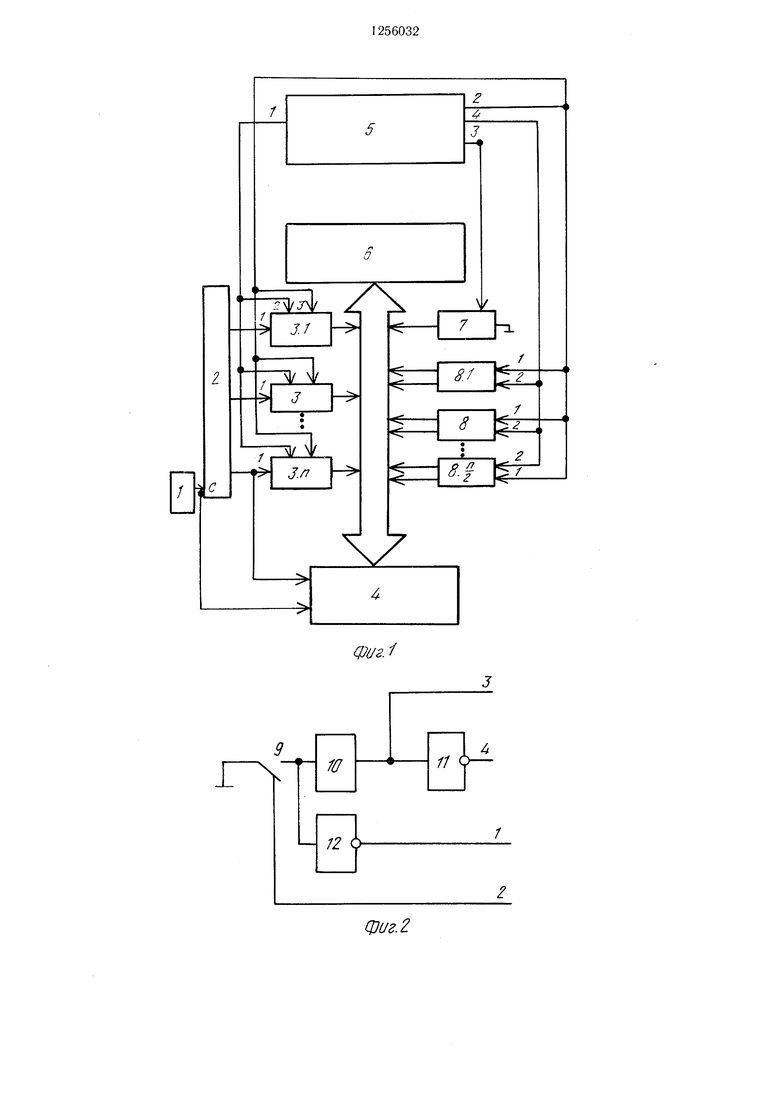

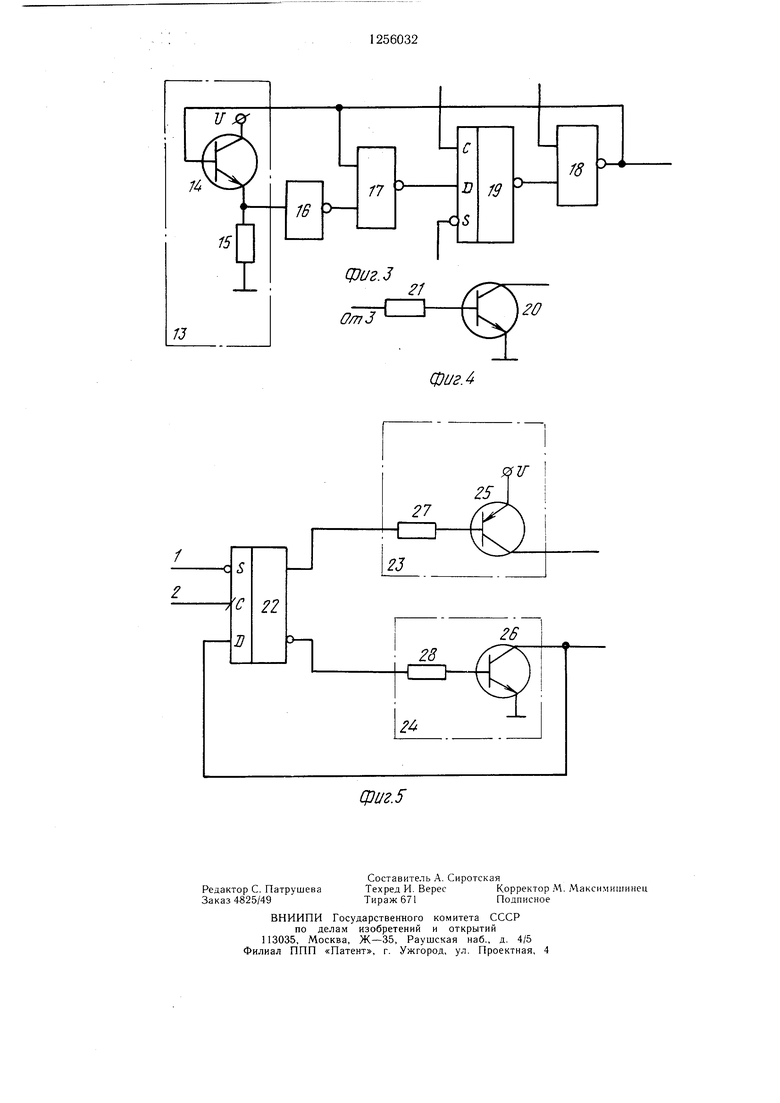

На фиг. 1 изображена структурная схема устройства; на фиг. 2 - схема блока син- хронизации; на фиг. 3 - схема блока обнаружения входов/выходов; на фиг. 4 - схема ключа; на фиг. 5 - схема блока коммутации питания.

Устройство для контроля логических блоков (фиг. 1) содержит генератор 1 тактовых импульсов, счетчик 2, блоки 3.1-З.п обнаружения входов/выходов, сигнатурный анализатор 4, блок 5 синхронизации, контролируемый блок 6, ключ 7, блоки 8.1-8.П/2 коммутации «питания (п - число выводов блока 6).

Блок 5 синхронизации (фиг. 2) содержит переключатель 9 и одновибраторы 10-12, реализованные на интегральных микросхемах (ИМС) К155АГЗ.

Блок обнаружения входов/выходов (фиг. 3) содержит эмиттерный повторитель 13, в состав которого входят транзистор 14 (тип КТ325) и резистор 15 (100 Ом), элемент НЕ 16, реализованный на ИМС К155ЛАЗ, элементы И-НЕ 17 и 18, реализованные на ИМС К155ЛА8 и D-триггер 19.

Ключ (фиг. 4) содержит транзистор 20 и резистор 21 и представляет собой транзисторный ключ, собранный по схеме с общим эмиттером и открытым коллектором.

Блок коммутации «питания (фиг. 5) содержит D-триггер 22, реализованный на ИМС К155ТМ2, и ключи 23 и 24, собранные по схеме с общим эмиттером и открытым коллектором и содержащие транзисторы 25, 26 и резисторы 27, 28.

Работа устройства основана на принци- пах сигнатурного анализа. На входы контролируемого блока подаются всевозможные двоичные комбинации, сигналы со всех выводов контролируемого блока преобразуются с помощью параллельного сигнатурного анализатора в четырехразрядный щестнад- цатиричный код (сигнатуру), который сравнивается с эталонным значением, рассчитанным или полученным по заведомо исправному блоку.

Когда переключатель 9 находится в положении «Сброс (как показано на фиг. 2), все блоки устройства отключены от контролируемого блока 6 (соответствующие выводы находятся в состоянии высокого импеданса). При замыкании переключателя 9 запускаются одновибраторы 10 и 11. Длительность импульса, формируемого одновиб- ратором 11, должна быть меньше длительности импульса на выходе одновибратора 10.

Положительный импульс на выходе одно- вибратора 10 включает ключ 7, что вызывает подачу логического нуля на отличный от «земли вывод контролируемого блока 6. К этому моменту «питание и «земля контролируемого блока еще не подключены. При этом логический нуль появляется на выводе «земля контролируемого блока 6 (вследствие наличия диода между входами микросхемы и общей шиной) и проходит на соответствующий блок 8.

По переднему фронту на инверсном выходе одновибратора 11 триггер 22 блока 8 устанавливается в нулевое состояние, открываются ключи 23, 24 и на соответствующие выводы контролируемого блока подается «питание и «земля. Остальные блоки 8 не оказывают влияния из-за наличия высокого импеданса на выходах ключей 25 и 26.

По окончании импульса на выходе одно- вибратора 10 запускается одновибратор 11. По переднему фронту импульса на инверсном выходе одновибратора 12 открываются бло- кн обнаружения входов/выходов, которые начинают передавать сигналы, формируемые счетчиком 2, на входы контролируемого блока 6. По сигналу с выхода переполнения счетчика 2 сигналы с входов и выходов контролируемого блока 8 начинают поступать в сигнатурный анализатор 4. По следующему фронту сигнала переполнения счетчика 2 прием сигналов в сигнатурный анализатор 4 заканчивается, а сигнатура, сформированная на основании принятых сигналов, высвечивается на индикационном табло сигнатурного анализатора. По следующему за этим фронту сигнала переполнения счетчика 2 снова начинается прием сигналов в сигнатурный анализатор, эта процедура периодически повторяется. Блоки 3 выполнены так, что каждый из них открывается сигналом одновибратора 12 только в том случае, если в момент перед поступлением данного сигнала на соответствующем выводе контролируемого блока 6 присутствует потенциал, характерный для входа блока (для ТТЛ-логнки порядка 1, 3 В). В противном случае, если на выводе контролируемого блока имеется потенциал, характерный для выхода блока (0,4 В или 2,3 В), блок 3 обнаружения входов остается закрытым и никакого влияния на контролируемый блок 6 не оказывает.

Различие входа от выхода производится следующим образом. Если на выводе блока 3 подсоединенного к контролируемому блоку 6, присутствует нулевой потенциал (0,4 В), то последний устанавливает элемент И- НЕ 17 в состояние, в котором на его выходе появляется высокий уровень напряжения, который подается на D-вход триггера 19, в результате чего в момент поступления управляющего сигнала с одновибратора 12 триггер 19 устанавливается в единичное состояние (что соответствует низкому уровню на его инверсном выходе), и элемент 18 с открытым коллектором остается закрытым. То же самое происходит и в случае, если на выводе, подсоединенном к контролируемому блоку 6, присутствует единичный потенциал (2,4 В), только в этом случае низкий уровень на вход элемента И-НЕ 17 поступает с выхода элемента 16. Если на выводе контролируемого блока 6 оказывается потенциал входа, то последний на выходе эмиттерного повторителя 13, собранного на транзисторе 14 и резисторе 15, на котором напряжение падает от 0,7 до 1,0 В, станет равным порядка 0,4 В. что приводит к появлению на выходе элемента НЕ 16, а следовательно, и на одном из входов элемента И-НЕ 17 высокого уровня. Так как на втором входе элемента И-НЕ 17 ток практически отсутствует, то на его выходе установится низкий уровень, в результате чего после поступления управляющего сигнала с одновибратора 12 триггер 19 установится в состояние, при котором открывается элемент 18 и тем самым осуществляется подача тестовых комбинаций на данные выводы контролируемого блока.

Блоки коммутации питания выполнены так, что ключи 23 и 24 открываются только в том случае, если перед поступлением управляющего сигнала с одновибратора 11 на соответствующем выводе контролируемого блока 6 присутствует нулевой потенциал. В противном случае блок коммутации питания остается закрытым и никакого влияния на контролируемый блок не оказывает.

Подключение «питания и «земли происходит следующим образом. При поступлении на отличный от «земли вывод контролируемого блока (для микросхем серии К, 155 в качестве такого вывода можно выбрать, например,первый вывод) нулевого потенциала, этот потенциал появится, на выводе «земли контролируемого блока и пройдет на О-вход триггера 22 одного из блоков 8. При поступлении управляющего сигнала с одновибратора 11 триггер 22 этого блока 8 перейдет в нулевое состояние, ключи 23 и 24 откроются и на Соответствующие выводы контролируемого блока 6 будут поданы «питание и «земля. (Потенциал на выводе «питания будет равен Е, а на выводе «земли - нулю, так как величина Е учитывает падение напряжения на открытых транзисторах 25 и 26 токовых ключей 23 и 24). В остальных блоках по.аключения «питания и «земли 8 ток на О-входе триггеров 22 практически отсутствует, поэтому эти триггеры оста,нутся в единичном состоянии, а соответствующие ключи 23 и 24 - закрытыми.

В устройстве удается полностью избавиться от ко.ммутаций за счет того, что автоматически идентифицируются и подключаются не только входы и выходы, но и выводы «питания и «земли контролируемого блока. Также не требуется отдельного эталонного блока для каждого типа контролируемых

блоков. Кро.ме ого, устройство может быть использовано л я автоматической идентификации логических блоков, так как каждому типу блоков сс:,)тветствует своя сигнатура.

Формула изобретения

1. Устройство для контроля логических блоков, содержащее блок синхронизации, 0 счетчик, п блоков обнаружения входов/выходов п - числа выводов контролируемого логического блока), генератор тактовых импульсов, выход которого соединен со счетным входом счетчика, разрядные выходы которого соединены с информационными 5 входами блокор обнаружения входов/выходов, входы синхронизации которых соединены с первым выходом блока синхронизации, выходы блоков обнаружения одов/выхо- дов соединены с соответствующими входами/выходами контролируемого .югического

блока, отличающееся те.м, что, с целью расширения функциональных возможностей путем обеспечения возможности контроля логических блоков с раз,1ичным расположением выводов «зе.мля и «питание, устрой5 ство содержит ключ, п/2 б,1оков коммутации питания и сигнатурный анализатор, причем второй выход блока синхронизации соединен с входами начальной установки всех блоков обнаружения входов/выходов и блоков коммутации питания, третий блока синхронизации соединен с управляющим входом ключа, информационный вход которого подключен к тине нулевого потенциала уст- .ройства, выход ключа соединяется с /-.м входом (( 1 ... п) контролируемого логического блока, первые и вторые выходы блоков

5 коммутации питания соединяются с соответствующими входами/выходами контролируемого логического блока и информационными входами сигнатурного анализатора, входы синхронизации блоков коммутации питания соединены с четвертым выходом блока синхронизации, выход генератора тактовых импульсов соединен с синхровходом сигнатурного анализатора, вход разрешения которого соединен с выходом переполнения счетчика.

:2. Устройство но п. 1. отличающееся тем,

что блок коммутации питания содержит D-триггер и два ключа, причем инверсный S-вход триггера соединен с входом начальной установки блока, вход синхронизации которого соединен с синхровходом )-три1 0 гера, прямой и нииерсный выходы которого соединены с управляюн1и.ми входами первого и второго ключей, информацион11ый вход первого к.иоча подключен к П1ине единичного потенциала, информационный вход второг-о ключа - к шине нулевого потенциала, выход

5 первого к. 1юча соединен с первым выходом блока, выход второго ключа с D-в.чодом триггера и вторым выходом б. юка.

фиг.

фиг.г

/4

If

фиг Л

| название | год | авторы | номер документа |

|---|---|---|---|

| Многоканальный сигнатурный анализатор | 1984 |

|

SU1262500A1 |

| Устройство для контроля цифровой аппаратуры | 1989 |

|

SU1735854A1 |

| Устройство для контроля цифровых узлов | 1986 |

|

SU1363215A1 |

| Устройство для контроля логических блоков | 1988 |

|

SU1624459A1 |

| Устройство для контроля цифровых блоков | 1985 |

|

SU1288700A1 |

| Устройство для контроля цифровых блоков | 1989 |

|

SU1709318A1 |

| Устройство для контроля цифровых блоков | 1990 |

|

SU1829037A2 |

| Устройство для контроля блоков постоянной памяти | 1983 |

|

SU1104590A1 |

| УСТРОЙСТВО КОНТРОЛЯ СОСТОЯНИЙ ПЕРЕГОННЫХ РЕЛЬСОВЫХ ЛИНИЙ | 2020 |

|

RU2746536C1 |

| Сигнатурный анализатор (его варианты) | 1984 |

|

SU1252784A1 |

Изобретение относится к автоматике и вычислительной технике и может быть использовано при контроле микросхем. Цель изобретения - расширение функциональных возможностей путем обеспечения возможности контроля логических блоков с различным расположением выводов «земля и «питание. Устройство содержит блок синхронизации, генератор тактовых импульсов, блоки обнаружения входов/выходов, блоки коммутации питания, ключ, сигнатурный анализатор. При включении блока синхронизации через ключ коммутируется логический «О, который поступает на любой вход логического блока, отличный от вывода «питание и «земля. Благодаря наличию в конструкции контролируемого логического блока (микросхема 155 ЛАЗ), напри.мер диода, между входом и общей шиной «земля, этот логический «О проходит на шину «земля, к которой подключен один из блоков коммутации питания, включает его, и питание и «О автоматически подключают ся к соответствующим выводам микросхемы. Остальные блоки коммутации не влияют на контролируемую микросхему вследствие состояния высокого импеданса на выходе. 1 з. п. ф-лы. 5 ил. (Л ю ел о о со 1чЭ

D

26

28

Редактор С. Патрушева Заказ 4825/49

ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий

113035, Москва, , Раушская наб., д. 4/5

Филиал ППП «Патент, г. Ужгород, ул. Проектная, 4

сриг.

Составитель А. Сиротская

Техред И. ВересКорректор М. Максиминшнец

Тираж 671Подписное

| Многоканальное устройство для контроля логических блоков | 1982 |

|

SU1038947A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для контроля логических блоков цвм | 1976 |

|

SU633019A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1986-09-07—Публикация

1984-09-13—Подача