S

N)

(

элементов памяти, не содержащих цепи предустановки. Устройство содержит наборное поле 1, генератор 2, коммутатор 3 выводов, дешифратор 4, коммутатор 5 адреса, регистр 6 кода выводов питания, блок 7 проверки на четность, счетчик 8 адреса, дешифратор 9 выводов питания, регистр 10 входов-выходов блок 11 постоянной памяти, коммутатор 12 выводов питания, блок 13 распределения синхроимпульсов, блок 14 сравнения, триггер 15 результата, многоконтактный зонд 16, индикатор 17, регистр 18 маски, элемент ИЛИ 19, интегрирующую КС-цепочку 20, элемент И 21, Положительный эффект достигается за счет введения средств идентификации типа микросхемы, цепей сброса регистра вьгаодов питания, а такзке введения RC-цепочки и элемента И, 1 з,п,ф-лы 3 ил.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля цифровых интегральных микросхем | 1986 |

|

SU1354142A1 |

| Устройство для контроля цифровых интегральных микросхем | 1985 |

|

SU1265663A1 |

| Устройство для контроля блоков памяти | 1986 |

|

SU1444896A1 |

| Устройство для контроля оперативной памяти | 1981 |

|

SU980166A1 |

| Устройство для контроля цифровых узлов | 1984 |

|

SU1231506A1 |

| Многопостовое устройство для контроля параметров электронных схем | 1983 |

|

SU1108374A1 |

| Устройство контроля параметров | 1990 |

|

SU1800447A1 |

| Устройство для контроля записи информации в программируемые блоки памяти | 1983 |

|

SU1104589A1 |

| Устройство для тестового контроля цифровых узлов | 1987 |

|

SU1425682A1 |

| Устройство для сопряжения процессора с памятью | 1988 |

|

SU1683020A1 |

Изобретение относится к контрольно-измерительной технике и может быть использовано для контроля цифровых микросхем. Цель изобретения - расширение функциональных возможностей устройства за счет контроля интегральных микросхем с различным расположением выводов питания и элементов памяти, не содержащих цепи предустановки. Устройство содержит наборное поле 1, генератор 2, коммутатор 3 выводов, дешифратор 4, коммутатор 5 адреса, регистр 6 кода выводов питания, блок 7 проверки на четность, счетчик 8 адреса, дешифратор 9 выводов питания, регистр 10 входов-выходов, блок 11 постоянной памяти, коммутатор 12 выводов питания, блок 13 распределения синхроимпульсов, блок 14 сравнения, триггер 15 результата, многоконтактный зонд 16, индикатор 17, регистр маски 18, элемент ИЛИ 19, интегрирующую RC - цепочку 20, элемент И 21. Положительный эффект достигается за счет введения средств идентификации типа микросхемы, цепей сброса регистра выводов питания, а также введения RC - цепочки и элемента И. 1 з.п. ф-лы, 3 ил.

Изобретение относится к контрольно-измерительной технике и может быт использовано для контроля цифровых микросхем.

Цель изобретения - расширение функциональных возможностей устройства за счет контроля интегральных микросхем с различным расположением выводов питания и элементов памяти, не содержащих цепи предустановки.

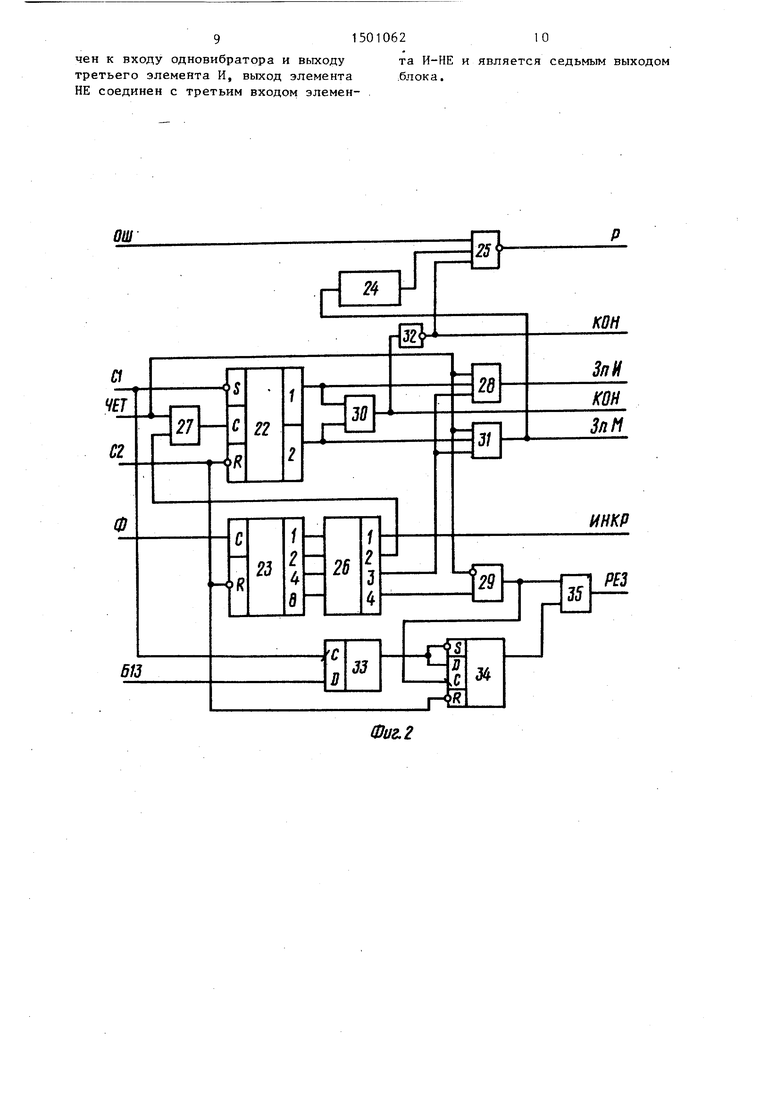

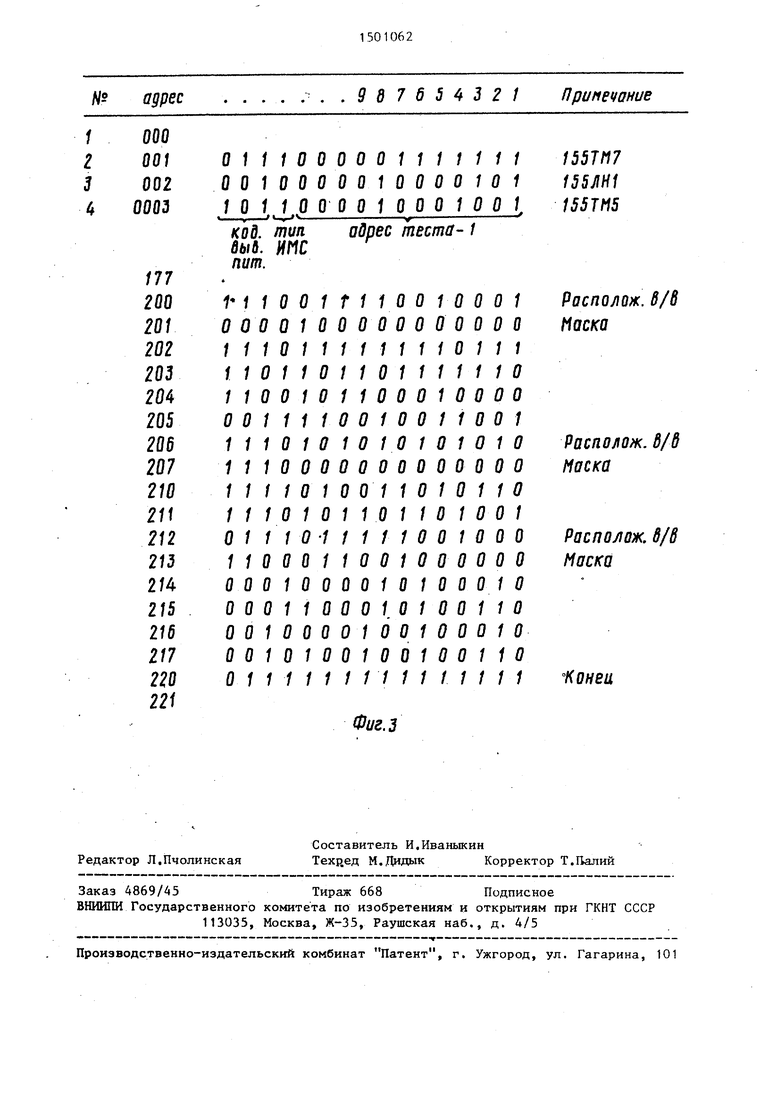

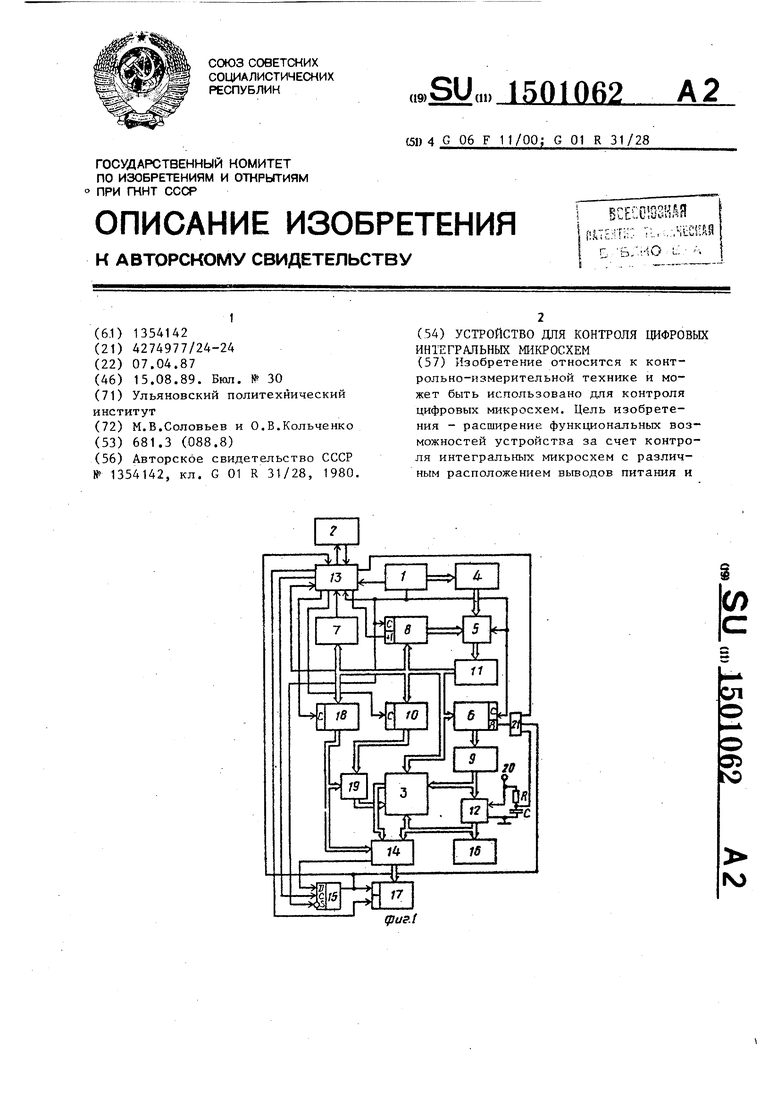

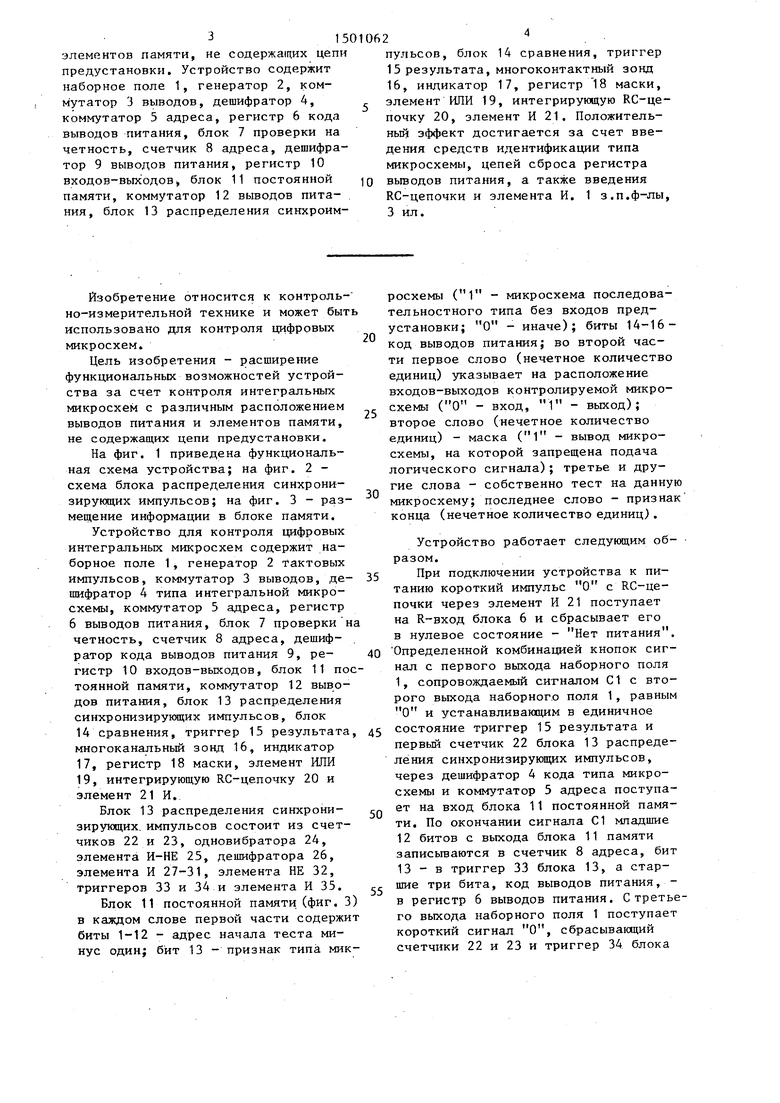

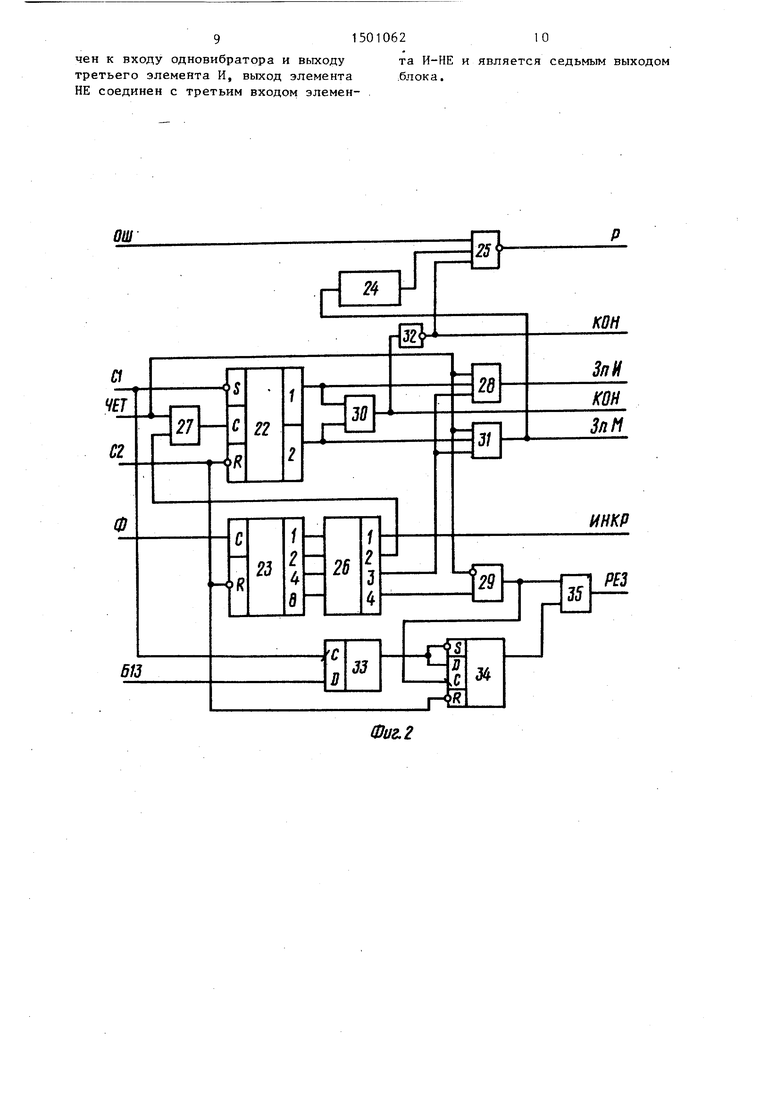

На фиг, 1 приведена функциональная схема устройства; на фиг, 2 - схема блока распределения синхронизирующих импульсов; на фиг, 3 - размещение информации в блоке памяти.

Устройство для контроля цифровых интеграпьньк микросхем содержит наборное поле 1, генератор 2 Тактовых импульсов, коммутатор 3 выводов, дешифратор 4 типа интегральной микросхемы, коммутатор 5 адреса, регистр 6 выводов питания, блок 7 проверки н четность, счетчик 8 адреса, дешифратор кода выводов питания 9, регистр 10 входов-выходов, блок 11 потоянной памяти, коммутатор 12 выводов питания, блок 13 распределения сйнхронизирукнцих импульсов, блок 14 сравнения, триггер 15 результата многоканальный зонд 16, индикатор 17, регистр 18 маски, элемент ИЛИ 19, интегрирующую RC-цепочку 20 и элемент 21 И,

Блок 13 распределения синхронизирующих, импульсов состоит из счетчиков 22 и 23, одновибратора 24, элемента И-НЕ 25, дешифратора 26, элемента И 27-31, элемента НЕ 32, триггеров 33 и 34 и элемента И 35,

Блок 11 постоянной памяти (фиг, 3 в каждом слове первой части содержи биты 1-12 - адрес начала теста минус один; бит 13 - признак типа мик0

5

0

5

0

5

0

5

росхемы (1 - микросхема последова- тельностного типа без входов предустановки; О - иначе); биты 14-16- код выводов питания; во второй части первое слово (нечетное количество единиц) указывает на расположение входов-выходов контролируемой микросхемы (О - вход, 1 - выход); второе слово (нечетное количество единиц) - маска (1 - вывод микросхемы, на которой запрещена подача логического сигнала); третье и другие слова - собственно тест на данную микросхему; последнее слово - признак конца (нечетное количество единиц) ,

Устройство работает следующим образом.

При подключении устройства к питанию короткий импульс О с RC-цепочки через элемент И 21 поступает на R-вход блока 6 и сбрасывает его в нулевое состояние - Нет питания. Определенной комбинацией кнопок сигнал с первого выхода наборного поля 1, сопровождаемый сигналом 01 с второго выхода наборного поля 1, равным О и устанавливающим в единичное состояние триггер 15 результата и первый счетчик 22 блока 13 распределения синхронизирующих импульсов, через дешифратор 4 кода типа микросхемы и коммутатор 5 адреса поступает на вход блока 11 постоянной памяти. По окончании сигнала С1 мпадшие

12битов с выхода блока 11 памяти записываются в счетчик 8 адреса, бит

13- в триггер 33 блока 13, а старшие три бита, код выводов питания, в регистр 6 выводов питания, С третьего выхода наборного поля 1 поступает короткий сигнал О, сбрасывающий счетчики 22 и 23 и триггер 34 блока

13 распределения синхронизирующих импульсов, после чего открывается элемент 25 H-FIE, сигнал О с выхода которого запускает генератор 2 тактовых импульсов. Если в триггер 33 блока 13 записан О, то триггер 34 блока 13 возвращается в единичное состояние. Под управлением сигналов, поступающих с выхода ре гистра 6 через дешифратор 9, срабатывает коммутатор 12 вьшодов питания и первая часть комм татора 3 выводов. Контролируемая микросхема запитывает- ся. Сигналом с выхода дешифратора 26 блока 13 инкрементируется содержимое счетчика 8 адреса, с выхода которого сигналы адреса теста поступают через коммутатор 5 адреса на адресные входы блока 11 памяти, с выхода которого считьгоается первое слово теста (расположение входов-выходов), содержащее нечетное количество едициц, о чем свидетельствует сигнал ЧЕТ, равный 1. Сигналом с второго выхода дешифратора 26 блока 13 открывается элемент И 27, выходной сигнал которого устанавливает состояние счетчика 22, равйое 01. (один). Сигнал с

третьего выхода дешифратора 26 прохо- 30 да дешифратора 26 через элемент И 29

дит через элемент И 28 на выход ЗпИ блока 13, по переднему фронту которого в регистр 10 входов-выходов записывается слово,, соответствующее расположению входов-выходов контролируемой микросхемы. Сигнал с четвертого выхода дешифратора 26 блока 13 поступает на элемент 29, закрытый сигналом . Цикл работы счетчика 23 продолжается. Сигналом с первого выхода дешифратора 26 блока 13 осуществляется инкремент счетчика 8 адреса. Сигналы на выходе блока 11 памяти соответствуют второму слову с нечетным количеством единиц. Сигнал ЧЕТ на выходе блока 7 проверки на четность равен 1. Сигнал с второго выхода дешифратора 26 открьшает элемент И 27, с выхода которого единичный сигнал устанавливает счетчик 22 блока 13 в состояние 10 (два). Сигнап с третьего выхода дешифратора 26 проходит через элемент И 31, записывает сигналы с выхода блока 11 памяти, соответствующие накладываемой маске, в регистр 18 маски, выходные сигналы которого переключают вторую группу коммутатора 3 выводов, и запускает одновибратор 24 блока 13 на время-.

35

40

45

50

55

поступает на элемент И 35. и, если триггер 34 находится в единичном состоянии, то записывается результат поразрядного сравнения, кроме разрядов, соответствующих единичному значению регистра маски, с выхода блока 14 сравнения в триггер 15 результата. Если триггер 34 сброшен, в триггер 33 записана 1, то сигнал с выхода триггера 34 запирает элемент И 35 и появление сигнала на четвертом выходе дешифратора 26 не вызывает записи поразрядного сравнения в триггер 15 результата. По окончании сигнала с четвертого выхода дешифратора 26 через элемент И 29 поступает на синхро- вход триггера 34 и записывает сигнал 1 с D-входа на выход. В следующем цикле сигнал с выхода 4 дешифратора 26 через элементы И 29 и 35 записывает результат поразрядного сравнения в триггер 15 результата. Данный цикл необходим для записи в контролируемую микросхему исходной информации, которая сравнивается с эталонной в следующем цикле.

Если в триггер 15 результата запи- сан О, т.е. обнаружена ошибка, при этом , то закрывается элемент

достаточное для переключения татора 3 вывод зв. Сигнал с четвертого выхода дешифратора 26 блока 13 поступает на элемент И 29, закрытый сигналом . Цикл работы счетчика 23 продолжается. Сигналом с первого выхода дешифратора 26 блока 13 осуществляется инкремент счетчика 8

0 адреса и сигналы на выходе блока 11 памяти, соответствующие третьему слову теста с четным количеством единиц, разряды которого, соответствующие входам контролируемой микросхемы,

5 есть сигналы входного воздействия,через коммутатор 3 выводов поступают на входы контролируемой микросхемы и на вторые входы блока 14 сравнения, а выходные разряды, ожидаемая реакция

0 контролируемой микросхемы на вторые входы блока 14 сравнения. Входные и реальные выходные сигналы с выводов контролируемой микросхемы поступают на соответствующие первые входы бло5 ка 14 сравнения. Сигналы со второго и третьего выходов дешифратора 26 не проходят через элементы И 27, 28 и 31, которые закрыты сигналом ЧЕТ, равным О. Сигнап с ч твертого выхо5

0

5

0

5

поступает на элемент И 35. и, если триггер 34 находится в единичном состоянии, то записывается результат поразрядного сравнения, кроме разрядов, соответствующих единичному значению регистра маски, с выхода блока 14 сравнения в триггер 15 результата. Если триггер 34 сброшен, в триггер 33 записана 1, то сигнал с выхода триггера 34 запирает элемент И 35 и появление сигнала на четвертом выходе дешифратора 26 не вызывает записи поразрядного сравнения в триггер 15 результата. По окончании сигнала с четвертого выхода дешифратора 26 через элемент И 29 поступает на синхро- вход триггера 34 и записывает сигнал 1 с D-входа на выход. В следующем цикле сигнал с выхода 4 дешифратора 26 через элементы И 29 и 35 записывает результат поразрядного сравнения в триггер 15 результата. Данный цикл необходим для записи в контролируемую микросхему исходной информации, которая сравнивается с эталонной в следующем цикле.

Если в триггер 15 результата запи- сан О, т.е. обнаружена ошибка, при этом , то закрывается элемент

И-НЕ 25 блока 13, единичный сигнал с выхода которого блокирует генератор 2 тактовых импульсов, а индикатор 17 высвечивает позицию дефектног вывода. Регистр 6 выводов питания сигналом через элемент И 21 сбрасывается, контролируемая микросхема отключается от источника питания. Процесс контроля завершен. В противном случае приведенный цикл повторяется до считьгеания блоком 11 памяти третьего нечетного слова - признака конца теста, после чего состояние счетчика 22 блока 13 ста- нет 11 (три) и единичный сигнал с выхода элемента 30 И блокирует че- рез элементы НЕ 32 и И-НЕ 25 работу генератора 2 тактовых импульсов, с выхода элемента И 30 сигнал поступает на второй вход индикатора 17, который высвечивает положительный результат контроля микросхемы, а инверсный сигнал КОН с выхода элемента НЕ 32 через элемент И 21 сбра- сывает регистр 6 выводов питания в состояние Питания нет. Контролируемая микросхема отключается от источника питания. Устройство готово к

дальнейшей работе.

I

Повторный запуск устройства осуществляется нажатием кнопок наборного поля 1.

Формула изобретения

5 0 5

0

5

Q с

Фиг. 2

Фиг.з

| Устройство для контроля цифровых интегральных микросхем | 1986 |

|

SU1354142A1 |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

Авторы

Даты

1989-08-15—Публикация

1987-04-07—Подача