Изобретение относится к вычислительной технике и может быть исполь зовано, в частности, в системах формирования кодов, а также в специализированных вычислительных устройства

.статической обработки информации.

Известны устройства для деления десятичных чисел, содержащие регистры операндов, сумматоры, логические элементы, в которых очередная цифра частного вычисляется с помощью серии вычитаний делителя из положительного

.остатка до получения отрицательной разности или серии сложений делителя с отрицательным остатком до получения положительной или нулевой 1 3Наиболее близким к предлагаемому является устройство для деления п-разрядных двоично-десятичных чисел содержащее регистр делимого, регистр делителя, регистр частного, блок формирования цифр частного, блок управления и вычислитель, два управляющих входа которого подключены к соответствующим выходам блока управления, третий вход которого через блок формирования цифр частного подключен к первому входу регистра част- . ного, второй вход которого подключен к четвертому входу блока управления и к управляющему входу регистра делимого, первый выход которого подключен к первому .входу cy iмaтopa, а второй вход последнего - к первому выходу регистра делителя, выход сумматора подключен к входу регистра делимого 2.

Недостатком являются избыточность аппаратуры и низкое быстродействие при решении частной задачи делени п-разрядных двои 1но-десятичных чисел на два.

Цель изобретения - упрощение устройства и повышение быстродействия при делении на два.

Поставленная цель достигается тем что устройство для деления п-разрядных двоично-десятичных чисел, содержащее вычислительный блок, содержит дополнительно (п-2) вычислительных блоков (п-число десятичных разрядов), каждый из вычислительных блоков представляет собой комбинационный сумматор , причем .каждый сумматор имеет четыре двоичных разряда, первые входы разрядов сумматоров соединены с входными шинами соответствующих десятичных разрядов делимого устройства, вторые входы первых и третьих разрядов комбинационных сумматоров соединены с шиной сигнала логического нуля устройства, вторые входы вторых и четвертых разрядов комбинационных сумматоров соединены с выходами первых разрядов Суммы предыдущих комбинационных суМмзторОб соответственно, BTOрые входы второго и четвертого разрядов ( п-1)-го комбинационного сумматоров соединен с первой входной шиной п-го десятичного разряда делимого устройства, входные шины с второй по четвертую п-го десятичного разряда делимого устройства и шина логического нуля устройства соединены с выходными шинами i;-ro десятичного разряда частного, выходные шины каждого разряда частного с первого по (п-1)-и устройства соединены с выходами разрядов суммы с второго по четвёртый и выходом переноса соответствующего комбинационного сумматора.

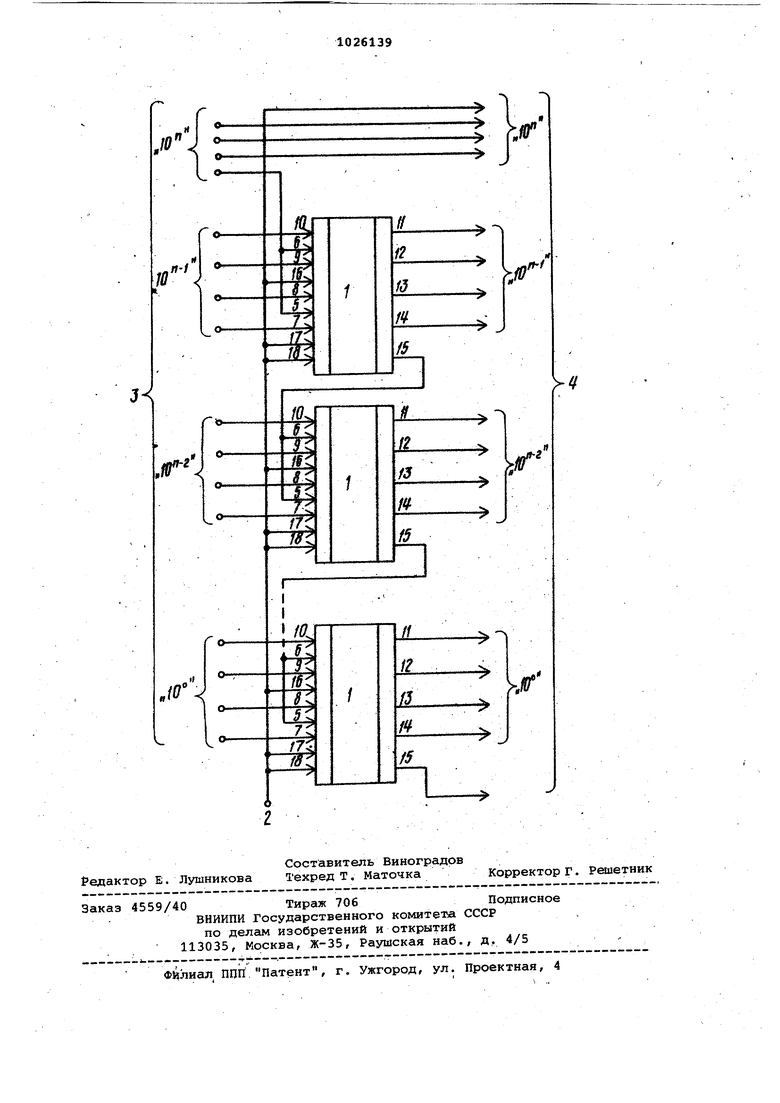

На чертеже изображена схема устройства для деления п-разрядных двоично-десятичных чисел.

Устройство содержит (п-1) четырехразрядных полных двоичных комбинаци1ОННЫХ сумматоров 1, вычислительных блоков-, шину 2 сигнала логического нуля, входные шины 3 делимого, выходные шины 4 частного.

Устройство работает следующим образом.

п-разрядное десятичное число в двоично десятичном коде поступает на входные шины 3 делимого..Три старших разряда двоичного кода цифры п-го разряда делимого являются тремя младшими разрядами двоичного кода цифры п-гр разряда частного, старший разряд кода цифры п-го разряда частного рав.ен нулю. Младший разряд двоичного кода п-го разряда делимого подается на входы 5 и 6 сумматора 1 (п-1)-1го разряда. Если младший разряд двоичного кода п-го разряда равен нулю, то двоичный код цифры (п-1)-го разряда делимого, поступающий на входы 7-10 сумматора 1 (n-l)-ro разряда, передается на выходы этого сумматора без изменения, и с выходов 11-14 снимается двоичный код цифры (n-l)-ro разряда частного, равный половине значения цифры (п-1)-го разряда делимого. Есл младший разряд 15 двоичного кода п-го разряда делимого равен единице, то в сумматоре 1 (п-1)-го разряда происходит сложение цифры разряда делимого с цифрой десяти (1010), и с выходов 11-14 сумматора 1 (п-1)-го разряда снимается двоичный код цифры (п-1)-го разряда частного, равный половине значения полученной двоичной cyMNM. Шина 2 подключена к входам 16-18 румматоров 1.

Младший разряд суммы с выход.а 15 сумматора 1 tп-1)-го разряда подаетс на входц 5 и 6 сумматора 1 (п-2)-го разряда, на входы 7-10 которого подается двоичный код цифры (п-2 -го разряда делимого. На выходах 11-14 сумматора 1 ( п-2)-го разряда формируется двоичный код цифры 1( п-2)-го разряда частного, равный половине значения цифры (п-2)-го разряда делимого, если младшийч разряд суммы с выхода разряда 15 сумматора 1 ( разряда равен нулю, или равный пологвине значения полученной суммы от сложения цифры (п-2)-го разряда делимого с цифрой десять -tlOlO) , если младший разряд суммы с выхода разряда 15 сумматора 1(п-1)-го разряда равен единице.

Младший разряд суммы с выхода разряда 15 сумматора 1 (п-2)-го разряда подается на входы 5 и 6 сумматора п-3)-го разряда (не показан).

Формирование десятичной цифры частного (п-З)-го и последующих разрядов аналогично описанному вьше формированию цифры частного (п-2 разряда. .

Первый разряд 15 выхода суммы сумматора 1 младшего разряда свидетельствует о четности делимого. Если данный разряд равен нулю, то дели-( мое - число четное и разделилось на два без остатка, если разряд равен

единице, то делимое число нечетное и к частному добавляется 0,5.

Например, когда на входные шины 3, подается код трехзначного десятичного числа 728(0111 0010 1000, на

выходных шинах 4 получается код

числа 364(0011 ОНО 0100 О; , а когда на входные шины 3 подается код числа 729(0111 0010 1001) на выходных шинах 4 получается код числа 364,5(OOII

ОНО 0100 1) .

Предлагаемое устройство в отличие от. известных содержи,т меньшее число элементов, так как в нем отсутствуют регистры делимого, делителя и

частного, блок формирования цифр частного и блок управления.

быстродействие устройства бпреде-, , ляё-ся только собственным временем переключения двоичных полных четырехразрядных сумматоров и не зависит от алгоритма формирования цифр частного и времени переключения регистров делимого, делителя, частного, блока фбрмирования цифр частного и блока управления.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для деления чисел | 1986 |

|

SU1417010A1 |

| УСТРОЙСТВО ДЛЯ ДЕЛЕНИЯ | 1991 |

|

RU2018934C1 |

| Устройство для деления чисел | 1990 |

|

SU1735844A1 |

| Устройство для деления | 1991 |

|

SU1783523A1 |

| Устройство для деления | 1990 |

|

SU1803913A1 |

| Устройство для деления чисел | 1985 |

|

SU1429109A1 |

| Вычислительное устройство | 1988 |

|

SU1545215A1 |

| Устройство для деления | 1985 |

|

SU1282117A1 |

| Преобразователь двоичного кода в двоично-десятичный код | 1978 |

|

SU742923A1 |

| Устройство для деления | 1990 |

|

SU1728862A1 |

УСТРОЙСТВО ДЛЯ ДЕЛЕНИЯ . Н-РАЗРЯДНЫХ ДВОИЧНО-ДЕСЯТИЧНЫХ ЧИСЕЛ, содержащее вычислительный блок, 6 т л и ч а ю щ е е с я тем, что, с целью упрощения устройства и повьаиения быстродействия при делении на два, оно содержит дополнительно (п-2) вычислительных блоков (п -число десятичных разрядов), каждай из вычислительных блоков, представляет собой комбинационный сумматор« причем каждый сумматор имеет четыре даоичных разряда, первые входы разрядов сумматоров соединены с входными шянами соответствующих десятичных разрядов делюлого устройств, вторые входи рервых и третьих разрядов комбинационных сумматоров соединены с шиной сигналалогического нуля устройства, входы вторых и четвертых разрядов комбинационных сумматоров соединены с выходами первых разрядов сумкоэ предыдущих комбинацион ных сумматоров соответственно, вторые входы второго и четвертого разрядов ( )-го кокйинационного сумкагора соединены с первой входной шиной п-го десятичного разряда делимого устройства, входные шины с второй по четвертую п-го десятичного раз- § ряда делимого устройства и шина логического куля устройства соединены с выхрДньвш шинами п-го десятичного разряда частного, выходные шины кгикдого разрдда частного с первого по (п-1)-й устройства соединены с выходами разрядов суммы с второго по четвертый и выходом переноса соответ- ствующего комбинационного суналатора.

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Карцев М | |||

| А | |||

| Арифметика цифровых машив, М., Наука, 1969, с | |||

| МАШИНА ДЛЯ ПРОИЗВОДСТВА ПОДЗЕМНЫХ РАБОТ | 1919 |

|

SU524A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Патент США 3735107, кл | |||

| Упругая металлическая шина для велосипедных колес | 1921 |

|

SU235A1 |

| ПРИБОР ДЛЯ ЗАПИСИ И ВОСПРОИЗВЕДЕНИЯ ЗВУКОВ | 1923 |

|

SU1974A1 |

Авторы

Даты

1983-06-30—Публикация

1982-03-24—Подача