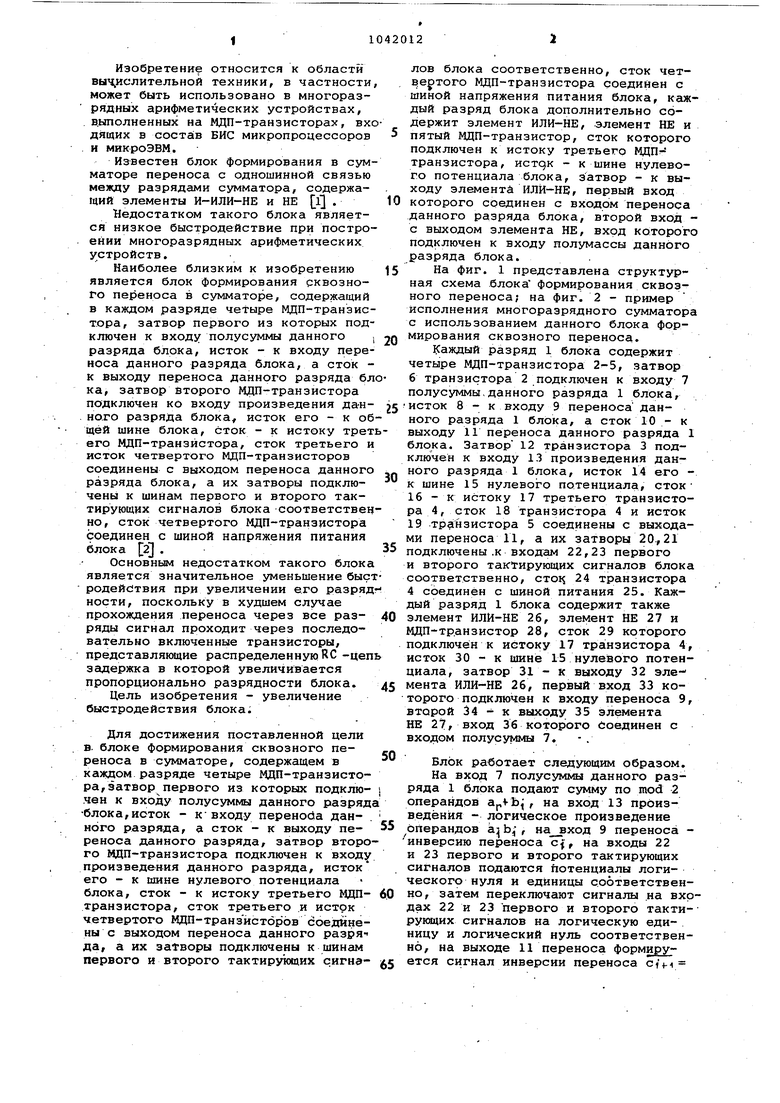

Изобретение относится к области вы ислительной техники, в частности может быть использовано в многоразрядных арифметических устройствах, в.ыполненных на МДП-транзисторах, вхо дящих в состав БИС микропроцессоров и микроэвм. Известен блок формирования в сумматоре переноса с одношинной связью между разрядами сумматора, содержащий элементы И-ИЛИ-НЕ и НЕ l . Недостатком такого блока является низкое быстродействие при построении многоразрядных арифметических устройств. Наиболее близким к изобретению является блок формирования сквозного переноса в сумматоре, содержащий в каждом разряде четыре МДП-транзистора, затвор первого из которых подключен к входу полусуммы данного разряда блока, исток - к входу переноса данного разряда блока, а сток к выходу переноса данного разряда бл ка, затвор Второго ВДП-транзистора подключен ко входу произведения да-нного разряда блока, исток его - к об щей шине блока, сток - к истоку трет его МДП-транзйстора, сток третьего и исток четвертого МДП-транзисторов соединены с выходом переноса данного разряда блока, а их затворы подключены к шийам первого и второго тактирующих сигналов блока соответствен но, сток четвертого МДП-транзистора соединен с шиной напряжения питания блока 12 , Основным недостатком такого блока является значительное уменьшение быс родействия при увеличении его разряд ности, поскольку в худшем случае прохождения переноса через все разряды сигнал проходит через последовательно включенные транзисторы, представляющие распределенную RC -цеп задержка в которой увеличивается пропорционально разрядности блока. Цель изобретения - увеличение быстродействия блока; Для достижения поставленной цели в. блоке формирования сквозного переноса в сумматоре, содержащем в каждом разряде четыре МДП-транзистора, затвор первого из которых подключей к входу полусуммы данного разряд блока,ноток - к-входу переноса данного разряда, а сток - к выходу переноса данного разряда, затвор второ го МДП-транзистора подключен к входу произведения данного разряда, исток его - к шине нулевого потенциала блока, сток - к истоку третьего МДПтранзистора, сток третьего и исток четвертого МДП-транзистбров соединены с выходом переноса данного paspH-i да, а их затворы подключены к шинам первого и второго тактируйхдих сигнэлов блока соответственно, сток четЭертого МДП-транзистора соединен с шиной напряжения питания блока, каждый разряд блока дополнительно содержит элемент ИЛИ-НЕ, элемент НЕ и пятый МДП-транзистор, сток которого подключен к истоку третьего транзистора, истдк - к шине нулевого потенциала блока, затвор - к выходу элемента ИЛИ-НЕ, первый вход которого соединен с входом переноса данного разряда блока, второй вход с выходом элемента НЕ, вход которого подключен к входу пол5массы данного разряда блока. . На фиг. 1 представлена структурная схема блока формирования сквозного переноса; на фиг. 2 - пример исполнения многоразрядного сумматора с использованием данного блока формирования сквозного переноса. Каждый разряд 1 блока содержит четыре МДП-транзистора 2-5, затвор 6 транзистора 2 подключен к входу 7 полусу7 1мы,данного разряда 1 блока, исток 8 - к входу 9 переноса данного разряда 1 блока, а сток 10 - к выходу 11 переноса данного разряда 1 блока. Затвор 12 транзистора 3 подключен к входу 13 произведения данного разряда 1 блока, исток 14 его к шине 15 нулевого потенциала, сток 16 - к истоку 17 третьего транзистора 4, сток 18 транзистора 4 и исток 19 транзистора 5 соединены с выходами переноса 11, а их затворы 20,21 подключены .к входам 22,23 первого и второго тактирующих сигналов блока соответственно, CTOJJ 24 транзистора 4 соединён с шиной питания 25. Каждый разряд 1 блока содержит также элемент ИЛИ-НЕ 26, элемент НЕ 27 и МДП-транзистор 28, сток 29 которого подключён к истоку 17 тра нзистора 4, исток 30 - к шине 15 нулевого потенциала, затвор 31 - к выходу 32 эле-мента ИЛИ-НЕ 26, первый вход 33 которого подключен к ВХОДУ переноса 9, второй 34 - к выходу 35 элемента НЕ 27, вход 36 которого Соединен с входом полусуммы 7. - . Блок работает следующим образом. На вход 7 полусуммы данного разряда 1 блока подают сумму по mod 2 операндов (, иа вход 13 произведения - логическое произведение операндов a;j b,f , 9 переноса инверсию переноса с|, на входы 22 и 23 первого и второго тактирующих сигналов подаются потенциалы логического нуля и единицы соответственно, затем переключают сигналы на входах 22 и 23 первого и второго тактирующих сигналов на логическую еди-. ницу и логический нуль соответственно, на выходе 11 переноса формируется сигнал инверсии переноса Cf+.1

с« () , причем, если a-b; 1, а aj-fbj 1, то сигнал переноса распространяется по двум цепям одновременно: через транзистор 2 и через элемент ИЛИ-НЕ 26 и транзисторы 28 и 4. Выигрыш в быстродействии получается за счет того, что транзистор 28 и транзистор 4 являются дополнительными цепями разряда монтажной емкости, сосредоточенной на выходе переноса 11.

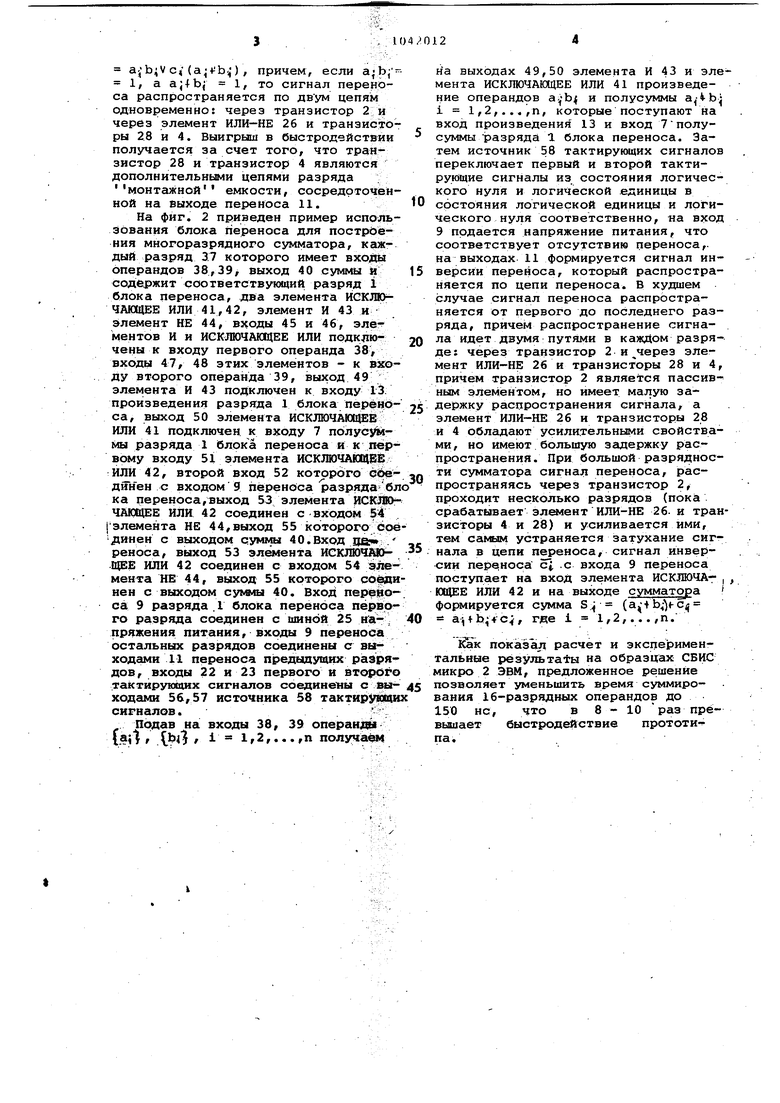

На фиг. 2 приведен пример использования блока переноса для построения многоразрядного сумматора, каждый разряд 3.7 которого имеет входы операндов 38,39 выход 40 суммы и содержит соответствующий разряд 1 блока переноса, два элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 41,42, элемент И 43 и элемент НЕ 44, входы 45 и 46, элементов И и ИСКЛЮЧАЮЩЕЕ ИЛИ подключены к входу первого операнда 38, входы 47, 48 этих элементов - к входу второго операнда 39, выход 49 элемента И 43 под ключен к входу 13 произведения разряда 1 блока переноса, выход 50 элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 41 Подключен к входу 7 п6лус5 Мы разряда 1 блока переноса и к первому входу 51 элемента ИСКЛЮЧАЮЩЩ ИЛИ 42, второй вход 52 которого соединен с входом 9 переноса 1 азрядабл ка переноса,выход 53 элемента ИСКЛКН ЧАЮЩЕЕ ИЛИ 42 соединен с входом 54 iэлемента НЕ 44,выход 55 которого оое динен с выходом суммы 40.Вход ЦВт реиоса, выход 53 элемента ИСКЛЮЧАК ЩЕЕ ИЛИ 42 соединен с входом 54 элемента НЕ 44, выход 55 которого соединен с выходом суммы 40. Вход переноса 9 разряда . 1 блока переноса первого разряда соединен с шиной 25 напряжеиия питания, входы 9 переноса остальных разрядов соединены с выходами 11 переноса предыдущих разрядов, входы 22 и 23 первого и второго тактируюсцих снгнгьлов соединены с вы- ходс1ми 56,57 источника 58 тактирующи сигналов.

Подав на входы 38, 39 операнда (aijJ , (Ь4 / 1 1,2,...,п получаем

на выходах 49,50 элемента И 43 и элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 41 произведение операндрв а.Ь и полусуммы i l,2,...,n, которые поступают на вход произведения 13 и вход 7 полусуммы разряда 1 блока переноса. Затем источник 58 тактирующих сигналов переключает первый и второй тактирук)щие сигналы из состояния логического нуля и логической единицы в состояния логической единицы и логического нуля соответственно, яа вход 9 подается напряжение питания, что соответствует отсутствию переноса,, на выходах 11 формируется сигнал инверсии переноса, который распространяется по цепи переноса. В худшем случае сигнал переноса распространяется от первого до последнего разряда, причем распространение сигнала идет двумя путями в каждом разряде: через транзистор 2 и через элемент ИЛИ-НЕ 26 и транзисторы 28 и 4, причем транзистор 2 является пассивным элементом, но имеет малую задержку распространения сигнала, а элемент ИЛИ-НЕ 26 и транзисторы 28 и 4 ОбЛсщают усилительными свойствами, но имеют.большую задержку распространения. При большой разрядности сумматора сигнал переноса, распространяясь через транзистор 2, проходит несколько разрядов (пока срабатывает элетлент ИЛИ-НЕ 26- и транзисторы 4 и 28) и усиливается ими, тем самЕШ устраняется затухание сигнала в цепи переноса, сигнал инверсин nepeiHoca ci .с входа 9 переноса поступает на вход элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 42 и на выходе сумматора формируется сумма S ()fc a,tb|4C4, где i 1,2,...,п.

Щк показал расчет и экспериментальные реэульта1ы на образцах СБИС микро 2 ЭВМ, предложенное решение позволяет уменыаить время суммирования 16-разрядных операндов до 150 НС, что в 8 - 10 раз превышает быстродействие прототи- па.

2 Ь2

II

II

II

Sn

| название | год | авторы | номер документа |

|---|---|---|---|

| Узел формирования переноса в сумматоре | 1985 |

|

SU1312567A1 |

| Формирователь переноса | 1990 |

|

SU1702361A1 |

| Узел формирования переноса в сумматоре | 1985 |

|

SU1287147A1 |

| Узел формирования переноса в сумматоре | 1985 |

|

SU1291969A1 |

| СУММАТОР | 1994 |

|

RU2049346C1 |

| Схема формирования переносов сумматора | 1988 |

|

SU1624443A1 |

| Сумматор | 1986 |

|

SU1406591A1 |

| Формирователь переноса | 1984 |

|

SU1223223A1 |

| УСТРОЙСТВО СЛОЖЕНИЯ С УСКОРЕННЫМ ПЕРЕНОСОМ | 2000 |

|

RU2198421C2 |

| Устройство для формирования группового переноса | 1985 |

|

SU1335981A1 |

БЛОК ФОРМИРОВАНИЯ СКВОЗНОГО ПЕРЕНОСА В СУММАТОРЕ, содержащий, в каяодом разряде четыре МДПтраиэистора, затвор из которых подключен к входу полусуммы данного разряда, исток - к входу переноса данного разряда, а сток - к вы-, ходу переноса данного разряда, затвор второго МДП-транзистора подключен к входу произведения данного, разряда, исток его - к шине нулевого потенциала блока, сток - к истоку третьего МДП-транзистора, сток треть- его и исток четвертого МДП-транзисторов соединены с выходом переноса данного разряда, а их затёоры подключены к шинам первого и второго тактирующих сигналов блока соответственно, сток четвертого МДП-транзистора соединен с шиной напряжения питания блока, отличающийс я тем, что,- с целью увеличения быстродействия, каждый разряд блока, дополнительно содержит злемент ИЛИ- НЕ, элемент НЕ и пятый МДП-транзистор, сток которого подключен к исто.ку третьего МДП-транзиСтора, исток к шине нулевого потенциала блока, § затвор - к выходу элемента ИЛИ-НЕ, (Л первый вход которого соединен с входом переноса данного разряда блока, второй вход - с выходом элемента НЕ, вход которого подключен к входу полусуммы данного разряда блока.

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Патент США №3728532, кл | |||

| Способ отопления гретым воздухом | 1922 |

|

SU340A1 |

| Приспособление для склейки фанер в стыках | 1924 |

|

SU1973A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Патент США 4016546, кл | |||

| Способ отопления гретым воздухом | 1922 |

|

SU340A1 |

| Шеститрубный элемент пароперегревателя в жаровых трубках | 1918 |

|

SU1977A1 |

Авторы

Даты

1983-09-15—Публикация

1979-12-26—Подача