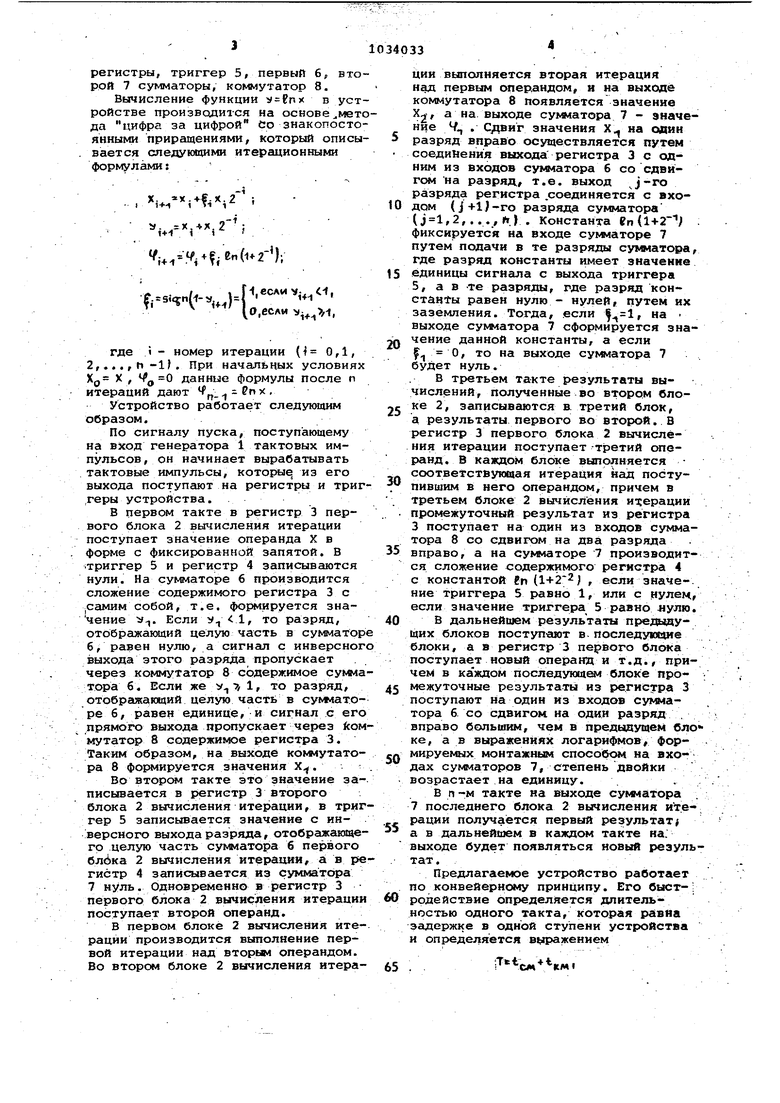

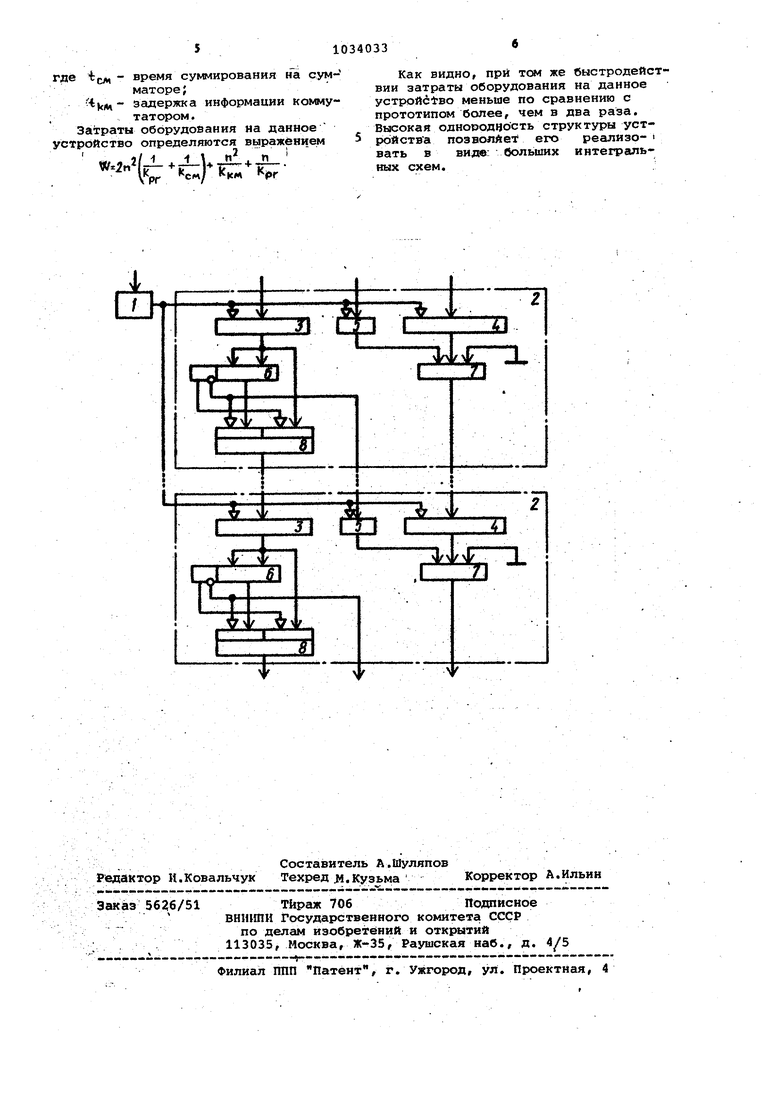

Изобретение относится к вычисли Тельной технике и предназначено для использования в специализирова ных ЦВМ высокой производительности В задачах, связанных с цифровой обработкой физической, акустической Навигационной, и другой информации, требуется выполнение операции логарифмирования над большими массивами данных. В частности данная операция необходима для сжатия динамического .диапазона сигнала. Причем в системах реального времени требования к быстродействию выполнения данной, операции очень высоки. Известно устройство для вычислеНИН логарифмов чисел, содержащее регистр числа, накопитель, блок дел ния, схему сравнения, кольцевой сдвигающий регистр, регистрырюзуль тата и блок управления. Алгоритм работы устройства основан на методе проб и оценок, fl . . . Недостатком известного устройств является низкое быстродействие, поскольку логарифм -числа выполняется в данном устройстве за количеств тактов,равное разрядности данного числа. /V Наиболее близким по технической сущности к предлагаемому является конвейерное устройство, для вычисления функции впх, содержащее входной регистр, две cxeNSd И, три коммутатора, два-сумматора, выходной регистр, блок управления, (2п 2) блоков вычисления итерации, каждый из которых содержит по два регистра два сумматора, два коммуггатора и схему И. Данное устройство производит вычисление функции v Рпх на основе . алгоритма Волдера со знакопеременны ми приращениями, в соответствии с которыми для вычисления функции X необходимо выполнить 2п итераций, где п - разрядность обpa6aTt BaeiuBdx чисел. Устройство пост роено по конвейерному принципу и в каждой ступени конвейера реализует одну итерацию алгоритма Волдера, что позволяет достичь очень высокого быстродействия С2 1. Однако наличие в устройстве 2м сз-упеней требует для его построения больших затрат оборудования, определяемых выражением . 2п (5.1- - if-)/- Е1{п-К(ии)V 1-2 (микросхем), где коэффиц 1енты Крг , Kg, К,( учи тывают количество обрабатываемых разрядов в одном корпусе мик; осхемы,, на которой строится соответственно регистр}, сумматор,коммутатор/ п разрядность обрабатываемых чисел; i - номер итерации, K(i)- число, равное i/2+l при i-четном и равное .(i-fl) /2 при i-нечетном. Цель изобретения - сокращение затрат оборудования. Указанная цель достигается тем, что в устройство для вычисления функции , содержащее генератор тактовых импульсов и п блоков вычисления итерации, каждый из которых состоит из первого и второго регистров, первого и второго сумматоров, коммутатора и триггера, причем выходы первого и второго регистров соединены соответственно с первыми входами первого и второго сумматоров , выход первого регистра подключен к. первому информационному входу коммутатора, выход второго сумматора i-ro блока вычисления итерации ( где t l-«-n) соединен с информационным входом второго регистра (5+1 1-го блока вычисления итерации, выход генератора тактовых импульсов подключен к упра вляющим входам всех регистров блоков вычисления итерации, в каждом i-м блоке, вычисления итерации выход первого регистра соединен с вторым входом первого сумматора со сдвигом на j разрядов вправо, (где j 0,1, .. .П-1),выход дробной части операнда первого сумматора подключен к второму информационному входу коммутатора, первый и второй управляющие входы которого соединены соответственно с прямым к инверсным выходами разряда целой части операнда первого сумматора,выход триггера подключен к второму входу сумматора, третий вход которого соединен с входом константы, инверсный выход разряда це лой части операнда первого сумматора и выход коммутатора т-го блока вычисления итерации подключен соответственно к информационным входам риггера и первого регистра (i+l)-ro блока вычисления итерации, выход генератора тактовых импульсов соединен с управляющими входами триггеров блоков вычисления итерации, вход и выход устройства подключены соответственно к информационным входам первого регистра и второго . сумматора первого и п-го блоков вычисления итераций. На чертеже представлена блок-схема устройства для вычисления функции . Устройство содержит генератор 1 тактовых импульсов и п блоков 2 вычисления итерации, каждый из которых содержит первый 3 и второй 4

регистры, триггер 5, первый 6, второй 7 сумматоры, коквиутатор 8.

Вычисление функции в устройстве производится на основе метода гхифра за цифрой Со знакопостоянныьш приращениями, который описывается следующими итерационными формулами:

. . .,.2-%

-1

.

;+-, V i fi« 2-|;

(t-v.)i

если v- (.1,

1+1

где i - номер итерации ( 0,1, 2,...,h-l. При начальных условиях X(j X , давние формулы после п итераций дают f,. Pf

Устройство работает следуннцим образом.

По сигналу пуска, поступающему на вход генератора 1 тактовых импульсов , он начинает вырабатывать тактовые импульсы, которы из его выхода поступают на регистры и триг,геры устройства.

В первом такте в регистр 3 первого блока 2 вычисления итерации поступает значение операнда X в форме с фиксированной запятой. В триггер 5 и регистр 4 записываются нули. На сумматоре 6 производится сложение содержимого регистра 3 с .самим собой, т.е. формируется значение у. Если у 1, то разряд, отображающий целую часть в су№4атор б, равен нулю, а сигнал с инверсног выхода этого разряда пропускает через коммутатор 8 содержимое сумматора б. Если же v 7, 1, то разряд, отображающий целую часть в сулматоре 6, равен единице, и сигнал с его прямого выхода пропускает через fcoMмутатор 8 содержимое регистра 3. Таким образом, на выходе коммутатора 8 формируется значения Х.

Во втором такте это значение записывается в регистр 3 второго блока 2 вычисления итерации, в триггер 5 записывается значение с инверсного выхода разряда, отображающего целую часть сумматора б первого 2 вычисления итерации, ai в регистр 4 записывается из сумматора 7 нуль. Одновременно в регистр 3 первого блока 2 вычисления итерации поступает второй операнд.

В первом блоке 2 вычисления итерации производится выполнение первой итерации над вторьи операндом. Во втором блоке 2 вычисления итерации выполняется вторая итерация над первым операндом, и на выходе коммутатора 8 появляетсязначение Х, а на выходе сумматора 7 - значение Ч . Сдвиг значения Х на олии разряд вправо осуществляется путем соединения выхода регистра 3 с одним из входов сумматора б со сдвигом на разряд, т.е. выход J-ro разряда регистра .соединяется с входом (j+lj-ro разряда сумматора (,2, ..., h I . Константа Sn () фиксируется на входе сумматоре 7 путем подачи в те разряды суитатора где разряд константы имеет значение единицы сигнала с выхода триггера 5, а в -те разряды, где разряд константы равен нулю - нулей путем их заземления. Тогда, если , на выходе сумматора 7 сформируется значение данной константы, а если f О, то на выходе cy в Iaтopa 7 будет нуль.

. В третьем такте результаты вычислений, полученные во втором Споке 2, записываются R третий блок, а результаты первого в-о второй. В регистр 3 первого блока 2 вычисления итерации поступает -третий операнд. В каждом блоке выполняется соответствующая итерация над поступившим в него операндом, причем в третьем блоке 2 вычисления иг ерации промежуточный результат из регистра 3 поступает на один из входов сумматора 8 со сдвигом на два разряда вправо, а на сумматоре 7 производится сложение содержимого регистра 4 с константой Сп (1+2г2; если значение триггера 5 равно 1, или с нулем если значение триггера 5 равно .нулю

В дальнейшем результаты пред94дущих блоков поступают в. последуисше блоки, а в регистр 3 первого блоКа поступает новый операнд и т.д., причем в каждом последующем блоке промежуточные результаты из регистра 3 поступают На один из входов С1тиматора б со сдвигом на один разряд , вправо большим, чем в предыдущем ел ке, а в выражениях логарифмов, формируемых монтажным способом на входах сумматоров 7, степень двойки возрастает .на единицу. .

В п-м такте на выходе сукматора 7 последнего блока 2 вычисления итерации получается первый результат; а в дальнейшем в каждом такте на. выходе будет появляться новый резултат .

Предлагаемое устройство работает по конвейерному принципу. Его быстродействие определяется длительностью одного такта, которая равна задержке в одной ступени устройства и определяется выражением

где сл - время суммирования на сумматоре;

tj, - задержка информации коммутатором.

Затраты оборудования на данное устройство определяются выражением

см/ KKM 9Г

Как видно, при же быстродействии затраты оборудования на данное устройс во меньше по сравнению с прототипом более, чем в два раза. Вьюокая ОДНОРОДНОСТЬ структуры устройства позволАеТ его реализо- вать в виде: больших интегральных схем.

| название | год | авторы | номер документа |

|---|---|---|---|

| Конвейерное устройство для вычисления логарифмической и экспоненциальной функций | 1982 |

|

SU1027722A1 |

| Устройство для вычисления функции @ = @ | 1982 |

|

SU1062693A1 |

| Конвейерное устройство для вычисления функций синуса и косинуса | 1981 |

|

SU1003080A1 |

| Устройство для реализации алгоритма Волдера | 1983 |

|

SU1115049A1 |

| Конвейерное устройство для вычисления гиперболических функций | 1981 |

|

SU1026141A1 |

| Устройство для цифровой обработки сигналов | 1985 |

|

SU1336028A1 |

| Конвейерное устройство для вычисления функции Y=е @ | 1981 |

|

SU962927A1 |

| Устройство для поворота вектора | 1983 |

|

SU1144104A1 |

| Конвейерное устройство для вычисления функции @ = @ | 1981 |

|

SU964635A1 |

| Устройство для вычисления логарифмов двоичных чисел | 1981 |

|

SU1023324A1 |

УСТРОЙСТВО ДЛЯ ВЫЧИСЛЕНИЯ ФУНКЦИИ vrlfnx , содержащее генератор тактовых импульсов и и блоков вычисления итерации, каждый из которых состоит из первого и второго регистров, первого и второго сумматоров, коммутатора и триггера, причем выходы первого и второго регистров соединены соответственно с первыми входами первого и второго сумматоров, выход первого регистра подключен к первому информационному входу.коммутатора, выход второго cyiywaTc a с i -го блока вычисления итерации (где i 1-V п 1соединен с , информационным входом второго регйстра (i +1)-го блока вычисления ;итерации, выход генератора тактовых импульсов подключен к управлякиди входам всех регистров блоков вычисления итерации, о т л и ч а ю tn е е с я тем, что, с целью сокращения объема оборудования, в каждом t-м блоке вычисления итерации выход первого регистра соединен с вторым входом первого сумматора со сдвигом на j разрядов вправо (где ,l ...,п-1), выход дробной части операнда первого сумматора под-, ключен к второму информационному входу коммутатора, первый и второй управлякияие вкоды которого соединены соответственно с прямым и инверсньм выходами разряда целой части операнда первого сумматора, выход триггера подключен к второму входу сумматора, третий вход которого соединен с входом константы, инверсг нь1й выход разряда целой части опет ранда первого сугФчатора и выход коммутатрра {-го блока вычисления итерации подключены соответственно к информационным входам триггера W первого регистра

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Устройство для вычисления логарифмов чисел | 1975 |

|

SU590733A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Авторское свидетельство СССР по заявке 3255903, кл.С1 06 F 7/556, 1981 -прототип ., | |||

Авторы

Даты

1983-08-07—Публикация

1982-03-29—Подача