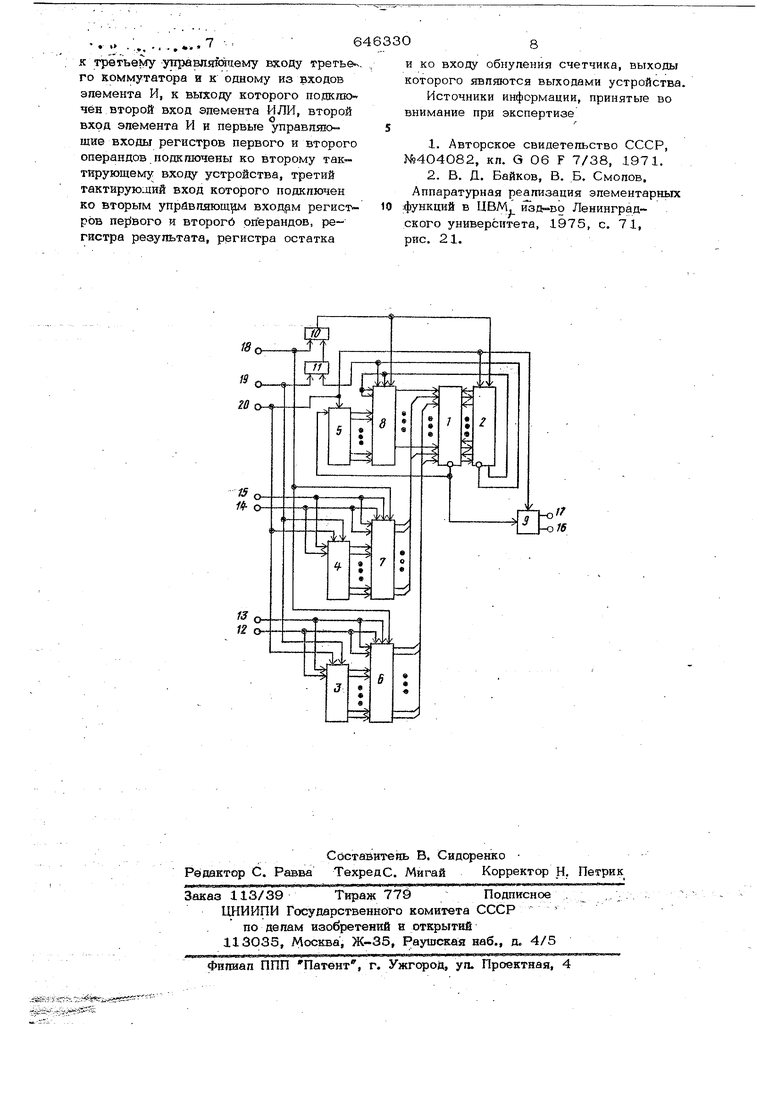

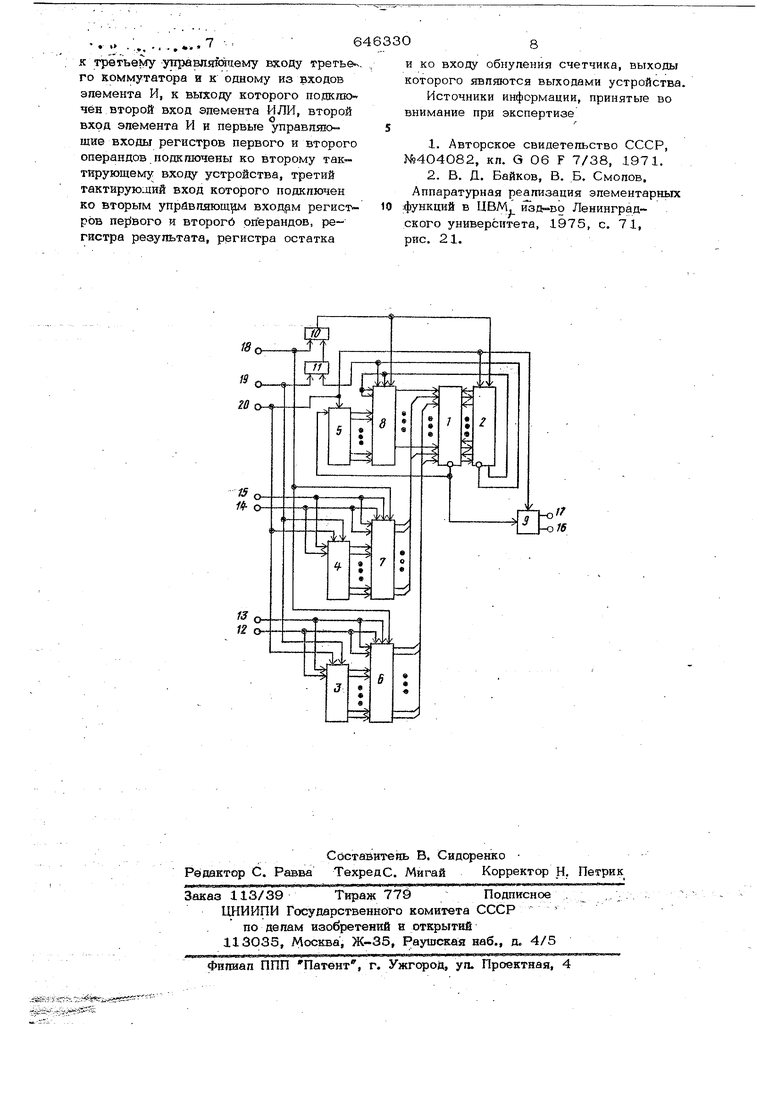

(54) УСТРОЙСТВО ДЛ Я ВЫЧИСЛ1-НИИ ФУНКЦИИ X -/А2+в2 гшющими входами первого и второго , коммутаторов и через элемент ИЛИ с первыми управп5пощими. входами третьего коммутатора и регистра остатка, прямой и. инверсный выходы старшего разряда которого подключены ко второму управпягощему входу и входам двух младших разрядов третьего коммутатора и, соответственно, к третьему управляющему входу третьего коммутатора и к одному из входов эле мента И, к выходу которого подключен второй вход элемента ИЛИ, второй вход элемента И и первые управляющие входы регистров первого и второго oneрандов подключены ко второму тактирую щему входу устройства, третий тактирую щий вход которого подключен ко вторым управляющим входам регистров первого и второго операндов, регистра результата, регистра остатка и ко входу обнуления счетчика, выходь которого явпяК тся выходами устройства. На чертеже изображена схема устрой ства, где 1-(2 11+2)-разрядн|.1й блоЖ суммирования ( h -раорядность операндо 2-(2Л+2)-разрядный регистр остатка} +2)-разрядный регистр первого операнда; 4-( п+2)-разрядный регистр второго операнда; 5-( П+2)-разрядный регистр результата; 6-( )-разрядный первый коммутатор; 7-( 11 +4)-раз рядный второй коммутатор; 8-( )разрядный третий коммутатор, 9-2-разрядный счетчик; Ю - элемент ИЛИ; 11 - элемент И; 12, 13 - входы первого операнда; 14, 15 - входы второго операнда; 16, 17 - выходы результата; 18, 19, 20 - тактирующие входы. Регистр 2 имеет цепь левого сдвига на два разряда и цепи циклического переноса из старщих разрядов в младшие. Регистры 3,4,5 имеют цепи левого сдвига на один разряд. Кроме того, два младших разряда регистров 3,4 обладают суммирующим свойством, а бсталЬньге разряды имеют цепь pacnpoci ранения переноса. Младший разряд регистра 5 обладает суммирующим свойств&м, а остальные разрядь имеют цепь распространения переноса. Исходные операнды А и В и результат X представлены двои.чным избыточНЫ1Й кодом с цифрами 0,1,2. При этом перанды А и В и результат X имеют ид п-1 A.Sa,2 , -1 В Г b, 2 , 1-1 ,2Л {од,2}... Каждый разряд числа в избыточном представлении кодируется двумя цифрами из мнОжества 0,1. При этом цифре 2 соответствует сигнал на входе 12 или 14, или выходе 16. Цифре 1 соответствует сигнал на входе 13 или 15 иди выходе 17. Цифре О соответствует отсутствие сигналов на входах 12, 13 или 14, 15 или выходах 16, 17. На величины Л и В накладьгааются следующие ограничения: 1,1/2$В 1. Работа устройства состоит в следу1ощем. В исходном состош1ии все регистры и счетчик устройства установлены в нулевое состояние. В каждом цикле вычислений на тактирующие входы 18, 19, 20 поочередно поступают соответ ственно тактирующие сигналы -fj У К началу каждого i -го цикла вычислений ( i-sl,2,... ) на входы 12, 13, и 14, 15 поступают цифры очередных разрядов 0 иЪ.В первом такте цикла вычислений сигнал 3 с входа 18 поступает на цепи выдачи кодов коммутаторов 6 и 7, на вход элемента ИЛИ 10, с выхода которого поступает сигнал на цепи выдачи кодов коммутатора 8 и регистра 2. В результате этого в блоке суммирования 1 происходит суммирование кодов, полученных на выходах регистра 2 и коммутаторов 6,7 и 8 и результат записьтается в регистр .2. При этом, если перед выполнением первого такта вычислений код регистра 2 был положительный (присутствует сигнал на инверсном вь1ходе старшего разряда регистра 2), то на четвертую группу входов блока суммирования 1 через коммутатор 8передается код со вторых входов этого коммутатора. Если же код регистра 2 был отрицательным (присутствует сигнал на прямом вьпсода старшего разрйда регистра 2), то на четвертую группу входов блока суммирования 1 передается код с первых входсж коммутатора 8. На входы четвертой группы блока суммирован11я 1, не связанные с выходами коммут .тора передается код старшего разряда этого коммутатора. Еспи существует сигнал на входе 13/15/, то через коммутатор 6/7/ на вторую третью группу входов бпока суммирования 1 передается прямой код. Есг№ существует сигнал на входе 12/14/, то через коммутатор 6/7/ на вторую (третью) группу вхо-. дов блока суммирования .1 передается удвоенный прямой код. Если сигнап Hia входах 12, 13 и 14,15 отсутствует, то коммутаторы 6 и 7 кодов не пере дают. На входы второй и третьей групп бпока суммирования 1, не связанные . с выходами коммутаторов 6 и 7, подаются, нулевые сигналы. Одновременн с этим, еспи при выполнении суммирования в бпоке суммирования 1 результат положительный (существует сигнал на инверсном выходе старшего разряда блока суммирования 1), то к содержимому регистра 5 и счетчика 9 прибавляется 1. Если результат отрицательный (соответствующий сигнал отсутст- вует) то регистр 5 и счетчик 9 не изменяет своего состояния. Во втором такте цикла вычислений сигнап входа 19 поступает на цепи левого сдвига регистров .3 и 4 и на вход элемента И 11. В результате этого происходи сдвиг на один разряд влево содержимого регистров 3 и 4. Одновре менно с этим, если существует сигнал на втором входе элемента И 11, . е. если код в регистре 2 положител ный, то сигнап с выхода элемента И 1 поступает на вход элемента ИЛИ 10, с выхода которого сигнал поступает на цепи выдачи кода регистра 2 и комму татора 8. В результате этого в блоке йуммирования 1 происходит сложение кодов, полученных на выходах регистра 2 и коммутатора 8, и изменение состо ния регистра 5 и счетчика 9 аналогично предыдущему такту. Если же сигнап на втором входе элемента И 11 отсутствует (код в регистре 2 отрицательный), то суммирования в блоке суммирования 1 не происходит в регистр 5 и счетчик 9 не изменяет своего состоя ния. После вьтолнения двух тактов то цикла в счетчике 9 находится цифра Х очередного разряда результата. В третьем такте цикла вычислений поступает сигнал с входа 2О на цепи приема кода регистров 3 и 4, на пепн сдвига регистров 2 и 5 и на цепь обнуления счетчика 9. В результате этого к содержимому регистров 3 и 4 прибавляются, соответственно цифры а., и bji содержимое регистра 2 сдвигается на два разряда влево, содержимое регистра 5 сдвигается на один разряд влево, а счетчик 9 устанавливается в нулевое состояние. При сдвиге отрицательных чисел в регистре 2 на два разряда влево в два младших разряда этого регистра записываются единицы. На этом заканчивается один цикл вычислений. Для получения М разрядов результата необходимо выполнить ц циклов вычислений. Формула изобретения Устройство для вычисления функции Хя V В, содержащее блок суммирования, первая группа входов которого подключена к выходам регистра остатка, а выходы - -ЕС входам регистра остатка, регистры первого и второго операндов, отличающееся тем, что, с целью повышения быстродействия, в него введены регистр результата, счетчик, элементы И, ИЛИ, первый, второй и третий коммутаторы, вторая, третья и четвертая группы входов блока суммирования соединены соответственно с выходами первого, второго и третьего коммутаторов, ко входам которых подключены соответственно вьь. ходы регистров первого и второго операндов и регистра результата, первый : управляющий вход которого и вход счетчика подкгаочены к инверсному выходу бпока суммирования, входы двух младших разрядов регистров первого и второго операндов, входы двух младших разрядов, первый и второй управляющие входы первого и второго коммутаторов подключены к первому и второму входам регистров соответственно первого к второго операндов, первый тактирующий вход устройства соединен с третьими управляющими входами первого и второго коммутаторов и через элемент ИЛИ - с первыми управл5пощими входами третьего коммутатора и регистра остатка, прямой и инверсный выходы старшего разряда которого подклк чены ко второму управя5пощему входу и входам двух младших разрядов треКёго коммутатора и, соответственно, -. .. .:,. ., ....7 .6 к третьему утгравлянАпему входу третье го коммутатора и к одному из входов эпемента И, к выходу которого подкгаочён второй вход эпемента ИЛИ, второй вход эпемента И и первые правпязощие входы регистров первого и второго операндов подкшочены ко второму так тирующему входу устройства, третий тактирующий вход которого подключен ко вторым управляют входам регистров и второгб операндов, регистра резупьтата, регистра остатка 0 и ко входу обнуления счетчика, выходы которого 5шпяются выходами устройства. Источники информации, принятые во внимание при экспертизе 1.Авторское свидетельство СССР, №404082, кп. G 06 F 7/38, 1971, 2.В. Д. Байков, В. Б. Смопов. Аппаратурная реализация элементарных ;функций в ЦВМ изд-во Ленинградского университета, 1975, с. 71, рис. 21.

| название | год | авторы | номер документа |

|---|---|---|---|

| Арифметическое устройство | 1977 |

|

SU669353A1 |

| Устройство для вычисления квадрата числа | 1983 |

|

SU1115051A1 |

| Устройство для деления | 1976 |

|

SU662938A1 |

| Устройство для вычисления тригонометрических функций тангенса и котангенса | 1980 |

|

SU907545A1 |

| Арифметическое устройство для выполнения операций над несколькими числами | 1976 |

|

SU662936A1 |

| Устройство для возведения в степень | 1976 |

|

SU744556A1 |

| Преобразователь двоично-десятичного кода в двоичный | 1985 |

|

SU1283979A1 |

| Устройство для извлечения квадратного корня | 1977 |

|

SU647684A1 |

| Устройство для возведения в квадрат | 1975 |

|

SU606156A1 |

| Устройство для деления | 1988 |

|

SU1513444A1 |

Авторы

Даты

1979-02-05—Публикация

1976-08-03—Подача