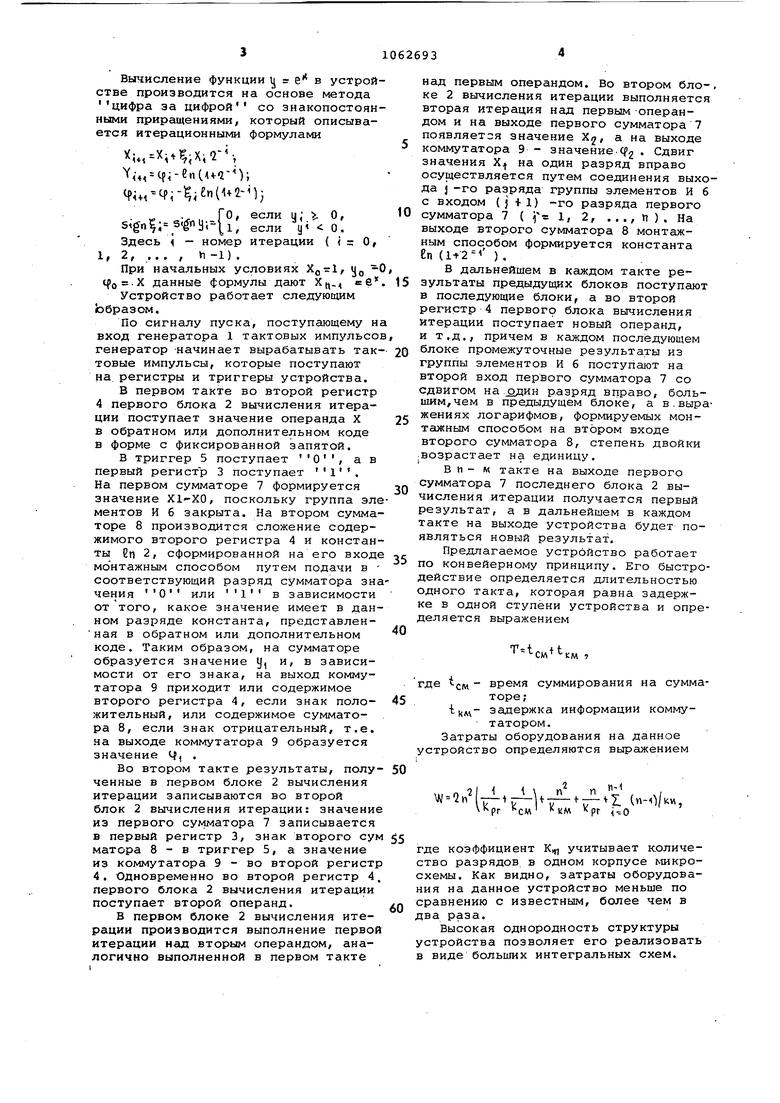

Изобретение относится к вычислительной технике и предназначено для использования в специализированных цифровых вычислительных машинах высокой производительности. Известно устройство для вычисления функции вида у -е, содержащее регистр аргумента,блок маскировани аргумента, блок постоянной памяти, блок оперативной памяти, блок выделения младшей зоны аргумента,- блок управления, блок определения нулевы значений аргумента, блок умножения И Недостатками устройства, являются низкое быстродействие, поскольку экспоненциальная функция здесь вычисляется по интегральной формуле, причем в каждой итерации использует ся времяемкая операция умножения, и большие затраты оборудования. Наиболее близким по технической сущности к изобретению является конвейер.-joe устройство для вычисления функци у е . содержащее (2п-1) блоков вычисления итерации, регистр триггер, выходной регистр, сумматор коммутатор, блок управления, каждый блок вычисления итерации которого содержит два регистра, два коммутатора, два сумматора. Данное устройство производит вычисления функции ij ь е на основе алгоритма Волдера со знакопеременными приращениями, в соответствии с которым для вычисления функции 1 г е необходимо выполнять 2)1 итераций, где h - разрядность обрабатываемых чисел Устройство пост;роено по конвейерному принципу и каждая ступень конвейе ра реализует одну итерацию алгоритма Волдера, что позволило достичь очень высокого быстродействия, определяемого задержкой в многоразрядном сумматоре pj ., Однако наличие в устройстве 2(т ступеней требует для его построения больших затрат оборудования, определяемых выражением -(- к ЬкЬЬ - микросхем, где коэффициенты Kpf , учитывают количество обрабатываемых разрядов в одном корпусе микрона которой строится соответсхемыственно регистр, сумматор, коммутатор, п 7 разрядность обрабатываемых чисел, - номер, итерации, К() число, равное i/r + 1 при i четном и равное ( if I)/-- при нечетном. Целью изобретения является сокращение оборудования. Поставленная цель достигается тем ч5:о в устройство для вычисления функции у - е , содержащее генератор тактовых импульсов и .М блоков вычисления итерации, каждый из которых содержит первый и второй регистры, первый и второй сумматоры и коммутатор, причем в каждом блоке вычисления итерации разрядные выходы первого регистра соединены с первой группой входов первого сумматора, разрядные выходы второго регистра подключены к первой группа входов второго сумматора и к информационным входам первой группы коммутатора, разрядные выходы первого сумматора каждого.блока вычисления итерации соединены с соответствующими разрядными входами первого регистра последующего блока вычисления итерации, выход генератора тактовых импульсов подключен к управляющим входам всех регистров устройства, введены в каж-дый блок вычисления итерации триггер и группа элементов И, первые входы которых соединены с соответствующими разрядными выходами первого регистра, выход триггера подключен к вторым входам элементов И группы, выходы которых соединены с второй группой входов первого сумматора, вторая группа входов второго сумматора подключена к входам константы Вя ) устройства, где i 1, ... , п, разрядные выходы второго сумматора соединены с информационными входами второй группы коммутатора, первый и второй управляющие входы которого подключены соответственно к Инверсному и прямому выходам знакового разряда второго сумматора, выход генератора тактовых импульсов соединен с управляющими входами всех триггеров устройства, прямой выход знакового разряда второго сумматора каждого блока вычисления итерации подключен к информационному входу триггера последующего блока вычисления итерации, выходы коммутатора Кс1Ждого блока вычисления итерации подключены к разрядным; входам второго регистра последующего блока вычисления итерации, На чертеже представлена блок-схема устройства для вычисления функции У е«, Устройство содержит генератор 1 тактовых импульсов и блоков 2 вычисления итерации, каждый из которых содержит первый и второй регистры 3 и 4, триггер 5, группа элементов И 6, первый и второй сумматоры 7 и 8, коммутатор 9, Коммутаторы 9 каждого-блока 2 вычисления итерации содержат две группы по и двухвходовых элементов И, объединенных элементом ИЛИ. Группа элементов И каждого блока 2 вычисления итерации содержит ( о - i ) двухвходовых элементов И,где - номер блока. Вычисление функции ij s е в устройстве производится на основе метода цифра за цифрой со знакопостоянньдми приращениями, который описывается итерационными формулами .x,, Yi.otfr nCUZ-); MU.Mr ientUl-M) Го, если у; Ь о, s gnl ; s |nB;-| l если у 0. Здесь - номер итерации ( О, 1,2,..., И-1). При начальных условиях , ijg -О if(.X данные формулы дают Х,,. 6 Устройство работает следующим Ьбразом. По сигналу пуска, поступающему н вход генератора 1 тактовых импульсо генератор -начинает вырабатывать тактовые импульсы, которые поступают на регистры и триггеры устройства. В первом такте во второй регистр 4 первого блока 2 вычисления итерации поступает значение операнда X в обратном или дополнительном коде в форме с фиксированной запятой, В триггер 5 поступает О, а в первый регистр 3 поступает , На первом сумматоре 7 формируется значение Х1-ХО, поскольку группа эле ментов И 6 закрыта. На втором сумматоре 8 производится сложение содержимого второго регистра 4 и константы Gn 2, сформированной на его входе монтажным способом путем подачи в соответствующий разряд сумматора зна 1 в зависимости от того, какое значение имеет в данном разряде константа, представлен ная в обратном или дополнительном коде. Таким образом, на сумматоре образуется значение у, и, в зависимости от его знака, на выход коммутатора 9 приходит или содержимое второго регистра 4, если знак положительный, или содержимое сумматора 8, если знак отрицательный, т.е. на выходе коммутатора 9 образуется значение t|i Во втором такте результаты, полу ченные в первом блоке 2 вычисления итерации записываются во второй блок 2 вычисления итерации: значение из первого сумматора 7 записывается в первый регистр 3, знак второго сум матора 8 - в триггер 5, а значение из коммутатора 9 - во второй регистр 4. Одновременно во второй регистр 4 первого блока 2 вычисления итерации поступает второй операнд. В первом блоке 2 вычисления итерации производится выполнение первой итерации над вторым операндом, аналогично выполненной в первом такте над первым операндом. Во втором бло-, ке 2 вычисления итерации выполняется вторая итерация над первым -операндом и на выходе первого сумматора 7 появляется значение Х, а на выходе коммутатора 9 - значение-cf . Сдвиг значения Х| на один разряд вправо осуществляется путем соединения выхода j-го разряда группы элементов И 6 с входом (J t1) -го разряда первого сумматора 7 ( 1, 2, . .., п ) . На выходе второго сумматора 8 монтажным способом формируется константа п ( ). В дальнейшем в каждом такте результаты предыдущих блоков поступают в последующие блоки, а во второй регистр 4 первого блока вычисления итерации поступает новый операнд, и т.д., причем в каждом последующем блоке промежуточные результаты из группы элементов И 6 поступают на второй вход первого сумматора 7 со сдвигом разряд вправо, большим, чем в предыдущем блоке, а в.выражениях логарифмов, формируемых монтажным способом на втором входе второго сумматора 8, степень двойки ;Возрастает на единицу. В п- м такте на выходе первого сумматора 7 последнего блока 2 вычисления итерации получается первый результат, а в дальнейшем в каждом такте на выходе устройства будет появляться новый результат. Предлагаемое устройство работает по конвейерному принципу. Его быстродействие определяется длительностью одного такта, которая равна задержке в одной ступени устройства и определяется выражением ,, где сцд- время суммирования на сумматоре ; задержка информации коммутатором. Затраты оборудования на данное устройство определяются выражением , см км рг о где коэффициент К. учитывает количество разрядов в одном корпусе микросхемы. Как видно, затраты оборудования на данное устройство меньше по сравнению с известным, более чем в два раза. Высокая однородность структуры устройства позволяет его реализовать в виде больших интегральных схем.

| название | год | авторы | номер документа |

|---|---|---|---|

| Конвейерное устройство для вычисления логарифмической и экспоненциальной функций | 1982 |

|

SU1027722A1 |

| Устройство для вычисления функции @ = @ | 1982 |

|

SU1034033A1 |

| Устройство для реализации алгоритма Волдера | 1983 |

|

SU1115049A1 |

| Устройство для поворота вектора | 1983 |

|

SU1144104A1 |

| Конвейерное устройство для вычисления гиперболических функций | 1981 |

|

SU1026141A1 |

| Конвейерное устройство для вычисления функции @ = @ | 1981 |

|

SU964635A1 |

| Устройство для цифровой обработки сигналов | 1985 |

|

SU1336028A1 |

| Конвейерное устройство для вычисления функции Y=е @ | 1981 |

|

SU962927A1 |

| Конвейерное устройство для вычисления функций синуса и косинуса | 1981 |

|

SU1003080A1 |

| Цифровой функциональный преобразователь Анишина | 1983 |

|

SU1157543A1 |

УСТРОЙСТВО ДЛЯ ВЫЧИСЛЕНИЯ ФУНКЦИИ у г содержащее генератор тактовых импульсов и п блоков вычисления итерации, каждый из которых содержит первый и второй регистры, первый и второй cy Dv aтopы и коммутатор, причем в каждом блоке вычисления итерации разрядные выходы первого регистра соединены с первой группой входов первого сумматора, разрядные выходы второго регистра подключены к первой группе входов второго сумматора и к информационным входам первой группы коммутатора, разрядные выходы первого сумматора-кс1ждого блока вычисления итерации соединены с соответствующими разрядными входами первого регистра и последующего блока вычисления итерации, выход генератора тактовых импульсов подключен к управляющим входам всех регистров устройства, отличающееся тем, что, с целью сокращения обору- дования, в каждый блок вычисления итерации введены триггер и группа элементов И, первые входы которых соединены с соответствующими разрядными выходами первого регистра, выход триггера подключен к вторым входам элементов И группы, выходы которых соединены с второй группой входов первого сумматора, вторая группа входов второго сумматора подключена к входам константы п ( ) устройства, где . 1, ..., и , разрядные выходы второго сумматора соединены с информационными входами второй группы коммутатора, первый и второй управляющие входы которого подключены соответственно к инверс(Л ному и прямому выходам знакового разряда второго сумматора, выход ге- нератора тактовых импульсов соединен с управляющими входами всех триггеров устройства, прямой выход знакового разряда второго сумматора каждого блока вычисления итерации подключен к информационному входу триггера последующего блока вычисления итерации, выходы коммутатора каждого блока вычисления итерации подключены к разрядным входам второго регистра последующего блока вычисления итерации.

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Устройство для вычисления функций | 1976 |

|

SU631924A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Конвейерное устройство для вычисления функции Y=е @ | 1981 |

|

SU962927A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1983-12-23—Публикация

1982-10-28—Подача