1027730

связан с выходом первого элемента мента запрета, вход первого элемента задержкир выход пятого элемента ИЛИ задержки подключен к выходу второго соединен с вторым входом первого эле- элемента И,

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для исправления ошибок | 1978 |

|

SU736104A1 |

| Устройство для исправления ошибок | 1983 |

|

SU1095183A1 |

| УСТРОЙСТВО ДЛЯ ИСПРАВЛЕНИЯ ОДИНОЧНЫХ ОШИБОК | 1973 |

|

SU363979A1 |

| УСТРОЙСТВО СИНХРОНИЗАЦИИ КОДОВЫХ КОМБИНАЦИЙ | 2023 |

|

RU2810267C1 |

| Оперативное запоминающее устройство с коррекцией ошибок | 1987 |

|

SU1539844A1 |

| СПОСОБ СИНХРОНИЗАЦИИ КОДОВЫХ КОМБИНАЦИЙ | 2023 |

|

RU2812335C1 |

| Устройство для обнаружения и исправления ошибок | 1985 |

|

SU1368995A1 |

| Устройство для исправления одиночных ошибок | 1977 |

|

SU648982A1 |

| Запоминающее устройство с самоконтролем | 1983 |

|

SU1167659A1 |

| Устройство для измерения коэффициента ошибок в цифровых системах передачи | 1984 |

|

SU1177920A1 |

УСТРОЙСТВО ДЛЯ ИСПРАВЛЕНИЯ ОШИБОК, содержаи ее регистр приема, регистр сдвига блока элементов И, регистр памяти, первый элемент И, матричный дешифратор, первый и второй элементы ИЛИ, первый и второй элементы запрета, первый элемент задержки, причем первый вход первого элемента И является тактовым входом устройства, второй вход первого элемента И подключен к выходу первого элемента запрета и первому входу регистра сдвига второй вход которого соединен с выходом первого элемента И, выход регистра сдвига связан с первым входом регистра приема, выход которого связан с входом матричного дешифратора, группа выходов которого подключена к группе соответствующих входов первого элемента ИЛИ, выход которого соединен с первым входом первого элемента запрета и является сигнальньм выходом устройства, группа выходов регистра памяти подключейа к группе входов блока элементов И, выход ко- , торого связан с вторым входом регист ра приема, вход первого элемента задержки соединен с первым входом второго элемента,запрета, отличаюiil е е с я тем, что, с целью повышения быстродействия коррекции О1иибок, введены дешифратор двойных ошибок, .третий, четвертый и пятый элементы ИЛИ, второй, третий и четвертый элементы И, второй элемент задержки, первый и второй элементы НЕ, причем выход регистра приема подключен к входу дешифратора двойных ошибок, группа выходов которого связана с группой соответствующих входов второго элемента ИЛИ, выход которого соединен с первым входом четвертого эле мента И, второй вход которого подключен к выходу второго элемента задеряс ки и к второму входу второго элемента запрета, первый вход которого соединен с входом второго элемента за(Л держки, выход второго элемента запре- та связан с вторым входом третьего с элемента ИЛИ, первый вход которого соединен с выходом четвертого элемента И, выход третьего элемента ИЛИ подключен к входу блока элементов И, о ю si группа выходов регистра памяти связана с группой соответстеукадих входов четвертого элемента ИЛИ, выход которого соединен с входом второго элемента НЕ и первым входом второго 60 О элемента И, второй вход которого cBir- зан с вторым входом третьего элемента И к прдкгяочен к шине Начало коррекции устройства, третий вход третьего элемента И соединен с треть им входом второго элемента И выходом первого элемента НЕ, вход которого подклочен к выходу первого элемента ИЛИ, выход второго элемента НЕ соединен с первым входом третьего элемента И, выход которого подключен к первому входу пятого элемента ИЛИ, второй вход которого

Изобретение относится к вычислительной технике и может быть использовано в устройствах переработки и передачи дискретной информации,

Известно устройство, содержащее регистр приема, матрицу, регистр сдв га, элемент И, элемент ИЛИ, элемент запрета-, элемент фиксации окончания приема кодовой комбинаций 1.,.

Недостатком устройства является возможность исправления лишь одиночных ошибок.

Наиболее близким к предлагаемому является устройство, содержащее регистр приема, регистр сдвига, матрич ный дешифратор,-дешифратор одиночных ошибок, первый и второй элементы ИЛИ блок элементов И, регистр памяти, элемент И, первый, второй, и третий элементы запрета, элемент задержки, первый вход элемента И является первым пходом ус-тройства, второй вход элемента И соединен с первым входом регистра сдвига и выходом первого элемента запрета, а выход - с вторым входом регистра сдвига, выход которого соединен с первым входом регистра приема, выход которого соединен с входом матричного дешифратора, выходы которого соединены с входами первого элемента ИЛИ, выход которого соединен с первым входом первого элемента запрета и выходом устройства, вход дешифратора одиночных ошибок соединен с выходом,регистра приема , а его выходы подключены к входам второго элемента ИЛИ, выход которого подключен к второму входу второго элемента запрета, выход которого соединен с первым входом третьего элемента запрета, второй вход которого соединен с выходом первого элемента ИЛИ, а выход - с вторым входом, блока- элементов И, первый вход блока элементов И соединен с выходом регистра памяти, а выход блока элеменТО8 И подключен к второму входу регистра приема, второй вход устройства соединен с первым входом второго элемента запрета и входом элемента за держки, выход которого подключен к второму входу первого элемента запрета 21,

Недостатком устройства является низкая скорость коррекции ошибок.

Цель изобретения - повышение бысродействия коррекции ошибок.

Поставленная цель достигается тем что в устройство для исправления ошибок, содержащее регистр приема, регистр сдвига блока элементов И, регистр памяти, первый элемент И, матричный дешифратор, первый и второй элементы ИЛИ, первый и второй элементы запрета, первый элемент задержки, причем первый вход первого элемента И является тактовым входом устройства, второй вход первого элемента И подключен к выходу первого элемента запрета и первому входу регистра сдвига, второй вход которого соединен с выходом первого элемента И, выход регистра сдвига связан с первы входом регистра приема, выход которого связан с входом матричного дешифратора, группа выходов которого подключена к группе соответствуюи1их входов первого элемента ИЛИ, выход которого соединен с первым входом первого элемента запрета и является сигнальным выходом устройства, группа выходов регистра памяти подключена к группе входов блока элементов И, выход которого связан с вторым входом регистра приема, вход первого элемента задержки соединен с первым входом второго элемента запрета, введены дешифратор двойных ошибок, третий, четвертый и пятый элементы ИЛИ, второй, третий и четвертый элементы И, второй элемент задержки, первый и второй элементы НЕ, причем выход регистра,приема подключен к вход дешифратора двойных ошибок, группа выходов которого связана с группой соответствуЮ1Цих входов второго элемента ИЛИ, выход которого соединен

с первым входом четвертого элемента И, второй вход которого подключен к выходу второго элемента задержки и к второму входу второго элемента зёпрета, первый вход которого соединен с входом второго элемента задержки, выход второго элемента запрета связан с вторым входом третьего элемента ИЛИ первый вход которого соединен с выходом четвертого элемента И, выход третьего элемента ИЛИ подключен к входу блока элементов И, группа выходов регистра памяти связана с группой соответствующих входов четвертого элемента ИЛИ, выход которого соединен с BXO дом второго элемента НЕ и первым входом второго элементами, второй вход которого связан с втьрым входом третьего элемента И и подключен к шине Начало коррекции устройства, третий вход третьего элемента И соединен с третьим входом второго элемента И и с выходом первого элемента НЕ, вход которого подключен к выходу первого элемента ИЛИ, выход второго элемен1га НЕ соединен с первым входом третьего элемента И, выход которого подключен к первому входу пятого элемента ИЛИ, второй вход которого связан с выходом первого элемента задержки , выход пятого элемента ИЛИ соединен с вторым входом первого элемента запрета, вход первого элемента задержки подключен к выходу второго элемента И.

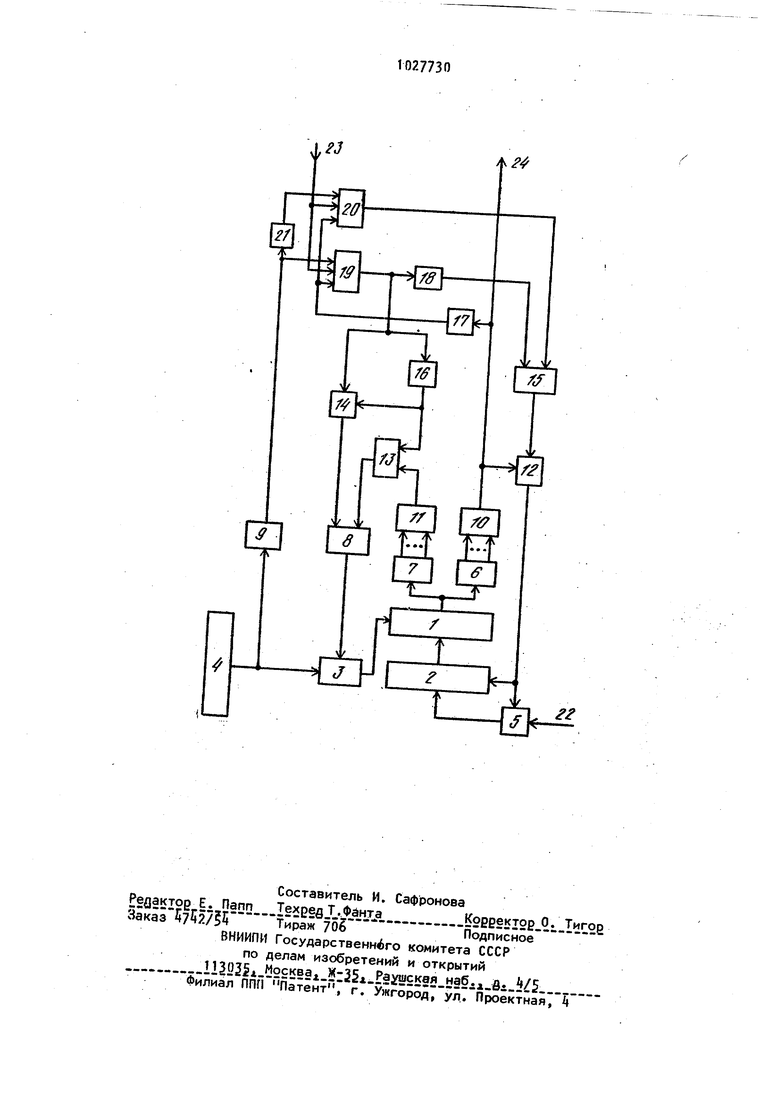

На чертеже приведена структурная схема устройства.

Устройство содержит регистр 1 приемаi регистр . сдвига, блок 3 элементов И, регистр k памяти, элемент И.5 матричный дешифратор 6, дешифратор 7 двойных ошибок, элементы ИЛИ 3-11, элемент запрета 12, элемент И 13, элемент 1 -запрета, эттемент ИЛИ 15, элемент 16 задержки, элемент НЕ 17, элемент 18 задержки, элемент И 19 и 20, элемент НЕ 21, шину 22 тактовых импульсов, шину 23 Начало коррекции, юину 2 Окончание коррекции.

Дешифратор 6 представляет собой дешифратор рабочих кодовых комбинаций. Дешифратор 7 двойных ошибок построен аналогично матричному дешифратору 6, он выделяет кодовые комбинации, еоде жащие двойные ошибки.

Регистр 4 памяти предназначен для запоминания номера разряда искажение информации в котором наблюдается устойчиво. Регистр 4 кодовыми ччинами через блок 3 элементов И соединен с регистром Г приема. Управляющий сиг- нал на открытие блока 3 элементов И поступает из третьего элемента ИЛИ 8.

f

Устройство работает следующим об-разом.

Перед приемом кодовой комбинации регистр 1 приема устанавливается в ноль. Если принятая кодовая комбинация ошибки не содержит, то на выходе матричного дешифратора б возбуждается шина, соответствующая принятой рабочей кодовой комбинации. На выходе элемента НЕ 17 формируется нулевой сигнал, который запреи(ает прохождение сигнала Начало коррекции через элементы И 19 и 20. На шине 2 Окончание коррекции устанавливается единичный сигнал.

Пусть все разряды регистра Ц памяти установлены в ноль, т.е. предположим, что нет такого разряда, искажение информации в котором наблюдается устойчиво. В этом случае на выходе элемента ИЛИ 9 будет нулевой сигнал, который закроет элемент И 19 и будет держать открытым через элемент НЕ 21 элемент И 20. Пусть на регистр 1 приема поступила кодовая комбинация, име ющая одиночную ошибку. 3 этом случае ни одна из шин дешифраторов 6 и 7 не возбуждается. На выходе элемента НЕ 17 формируется единичный сигнал, который разрешает прохождение сигнала Начало коррекции через элеMeHt И 20. Сигнал Начало коррекции с выхода элемента И 20 проходит через элемент ИЛИ 15 и элемент.12 запрета, переводит в единичное состояние младший разряд регистра 2 сдвига и обеспечивает прохождение тактовых импульсов по шине 22 через элемент И 5.

Тактовые импульсы поступают на вход регистра 2 сдвига и обеспечивают перемещение единицы в регистре сдвига, последовательно инвертируя содержимое разрядов регистра 1. Каждый приемный элемент регистра 1 изменяет свое состояние при записи единицы в связанный с ним разряд регистра сдвига и возвращается в исходное состояние при записи в этот разряд нуля. Как только в результате этой коррекции будет получен правильный код (рабочая кодовая комбинация ) возбуждается одна из Шин матричного дешифратора 6, на выходе элемента ИЛИ 10 устанавливается единичный

сигнал, а на выходе элемента 12 запрета - нулевой Сигнал.. Последний прекращает прохождение тактовых импульсов с шины 22 через элемент И 5 на регистр 2- сдвига. На шине Окончание коррекции устанавливается единичный сигнал.

Ьсли ошибка а одном и том же разряде повторяется несколько раз, что свидетельствует о наличии устойчивого отказа (неисправности кодовой шины то в соответствующий разряд регистра 4 памяти заносится единица. Наличие единицы в одном из разрядов регистра памяти фиксируется элементом ИЛИ 9, сигнал с выхода которого открывает по первому входу элемент И19 и через элемент Hi- 21 закрывает элемент-И 20.

При наличии единицы в одном из разрядов регистра k памяти и отсутствии ошибок в кодовой комбинации работа устройства не отличается от изложенного выше.

Пусть один из разрядов регистра j памяти содержит единицу и в принятой кодовой комбинации содержится одиночная ошибка, В этом случае ни одна из шин матричного дeu ифpaтopa 6 и дешифратора 7 двойных ошибок не возбуждается. Нулевой сигнал с выхода элемента ИЛИ 10, пройдя через элемент НЕ 17, открывает по третьим входам элементы И 19 и 20. Причем в данном случае элемент И 19 по первому входу открыт, а элемент И 20 закрыт. Сигнал Начало коррекции, пройдя через элемент И 19 поступает на вход элементов 1б и 18 задержки, а также через элемент 1 запрета, и элемент ИЛИ 8 открывает блок 3 элементов И. Содержимое регистра t памяти поступает в регистр 1 приемных элементов, изменяя состояние соответствующего разряда кодовой комбинации ( выполняется операция поразрядного сложения по модулю 2 )„ В результате одиночная ошибка либо сводится к двойной, либо преобразуется в рабочую кодовую комбинацию. Более вероятным является второй вариант, так как единица в данном разряде регистра k памяти говорит о неисправности кодо.вой шины этого разряда Следовательно, если неисправна одна из кодовых

шин и в кодовой комбинации присутствует одиночная ошибка, то вероятнее всего, что она возникла в разряде, имеющем неисправную кодовую шину. Таким образом, в случае коррекции ошибки возбуждается одна из шин матричного дешифратора 6, и сигнал с выхода .лемента ИЛИ 10 поступает на вход элемента 12 запрета, запрещая тем самым прохождение сигнала Начала коррекции на вход элемента И 5. Этот же сигнал поступает на шину 2 Окончание коррекции.

0 Менее вероятным оказывается случай, когда одна из кодовых шин неисправна { присутствует единица в одном из разрядов регистра памяти , а в кодовой комбинации имеет место одиночная ошибка в другом разряде. В этом случае, после описанного выше поразрядного сложения по модулю два содержимого ре гистра 1 приема с содержимым регистра j памяти, одиночная ошибка переводится в двойную. В результате этого возбуждается одна из шин деижфратора 7 двойных ошибок. Элемент 16 задержки осуществляет задержку сигнала Начала коррекции на время, необходи 5 мое для надежной переписи содержимого регистра 4 памяти в регистр 1 приема для сложения с его содержимым по модулю два. После этого сигнал с элемента 16 задержки запрещает прохождение сигнала Начало коррекции через элемент 1 запрета, это приводит к закрытию блока 3 элементов И по второму входу. В то же время сигнал с выхода элемента 16 задержки держит открытым по второму входу элемент И 13. Сигнал, возникший На одной из шин дешифратора 7 двойных ошибок, проходит через элемент ИЛИ 11, открытый по вто рому входу элемент И 13, схему ИЛИ 8 и вновь открывает блок 3 элементов И, разрешая тем самым повторное с ложение по модулю два содержимого регистра 1 приема с содержимым регистра k памяти. В результате этого двойная ошибка сво.дится к первоначально присутствующей

В кодовой комбинации одиночной ошибке. Элемент 18 задержки предназначен для задержки сигнала Начало коррекции на время, необходимое для описанной выше двойной пересылки содержимого регистра k памяти в регистр 1 приема. Сигнал с выхода элемента 18 задержки проходит через элемент ИЛИ 15, элемент 12 запрета, переводит в единичное состояние младший разряд

55 регистра 2 сдвига и обеспечивает -.прохождение тактовых импульсов через эле- мент И 5. Далее устройство работает аналогично описанному случаю, когда

имелась одиночная ошибка в кодовой . комбинации и не было ни одной единицы в регистре k памяти.

Пусть в одном из разрядов регист-, ра k памяти находится единица, а в кодовой комбинации, принятой на регистр 1 приема, имеет место двойная ошибка. В этом случае сигнал Начало .коррекции с выхода элемента И 19 проходит через элемент Vk запрета, элемент ИЛИ 8 и открывает блок 3 элементов И. Содэттимое регистра памяти поступает в регистр 1 приема и складывается с его содержимым по модулю два. В результате двойная ошибка сводится к одиночной. Начало коррекции кроме того, задержанный элементом задержки 18, проходит через элемент ИЛИ 15, элемент 1.. запрета и осу1чествляет исправление этой одиночной ouJибки.

Предлагаемое устройство обеспечивает также исправление двойной ошибки в случае неисправных двух разрядных кодовых шин 1 когда в регистре k памяти имеются единицы в двух-разрядах )о

Таким образом, предлагаемое устройство выполняет те же функции, что и прототип, однако скорость исправления наиболее вероятных ошибок у него выше. Так, в случае одиночной ошибки в кодовой комбинации и при наличии нулевой во всех разрядах регистра k памяти сигнал Начало коррекции проходит через элемент И 20, элемент ИЛИ 15, элемент 12 запрета, . в обход элемента 1B задержки, чем обеспечивается выигрьпч во йремени исправления одиночной ошибки по сравнению с прототипом на время задержки сигнала Начало коррекции элементом 13 задержки. . В том случае, если неисправна одна из кодовых шин т,е. в одном из разрядов регистра Ц памяти присутствует единица и в кодовой комбинации содержится .одиночная ошибка, то вероятнее всего, что эта ошибка будет

в разряде с неисправной кодовой шиной. Нсли кодовая комбинация содержит П разрядов и вероятности отказа кодовых шин каждого разряда одинаковы, то математическое ожидание номера отказавшего разряда равно п/2. Следовательно, в среднем для такого случая предлагаемое устройство позволяет сократить время исправления одиночной ошибки на время выполнения опера ций сдвига в регистре 2 сдвига и h/2

операции сложения в регистре приема у

/J

I

/

т

ff

1

//

i , V I

ФФ

I и

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| УСТРОЙСТВО ДЛЯ ИСПРАВЛЕНИЯ ОДИНОЧНЫХ ОШИБОК | 0 |

|

SU363979A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Способ тушения бензина и других легко воспламеняющихся обезвоженных жидкостей | 1947 |

|

SU73610A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

Авторы

Даты

1983-07-07—Публикация

1982-03-22—Подача