1095183 соединен с входом сдвига регистра дом сдвига, второй вход первого элемента, К соединен с устаиовочным вхо-сяза. регистра сдрига и являетустройсТвходом запуска

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для исправления @ -кратных ошибок | 1985 |

|

SU1425849A2 |

| Устройство для исправления ошибок | 1990 |

|

SU1783622A1 |

| Устройство для исправления модульных ошибок | 1988 |

|

SU1522414A1 |

| Декодирующее устройство линейного циклического кода | 1990 |

|

SU1718386A1 |

| Устройство для исправления ошибок | 1982 |

|

SU1027730A1 |

| Устройство кодирования-декодирования числовых последовательностей | 1990 |

|

SU1809541A1 |

| Устройство для исправления ошибок | 1978 |

|

SU736104A1 |

| Устройство для обнаружения и исправления ошибок в кодовой последовательности | 1988 |

|

SU1580568A1 |

| Устройство для дешифрации команд | 1987 |

|

SU1532932A1 |

| УСТРОЙСТВО КОДОВОЙ ЦИКЛОВОЙ СИНХРОНИЗАЦИИ | 2008 |

|

RU2383104C2 |

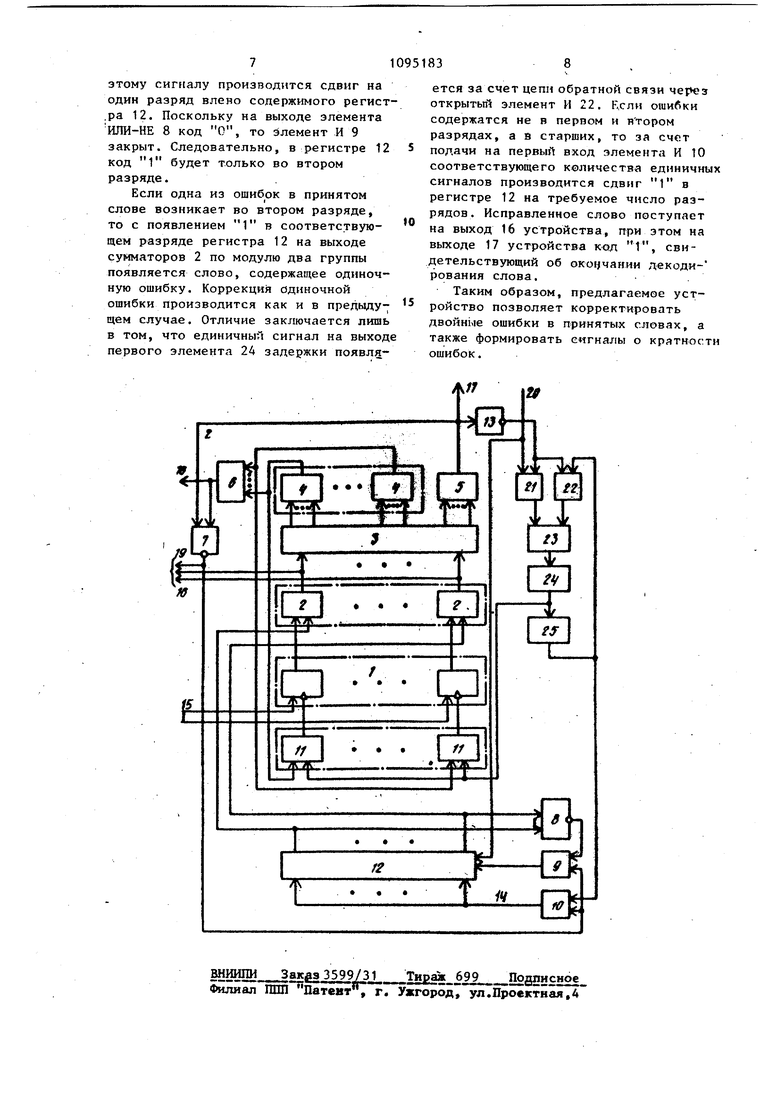

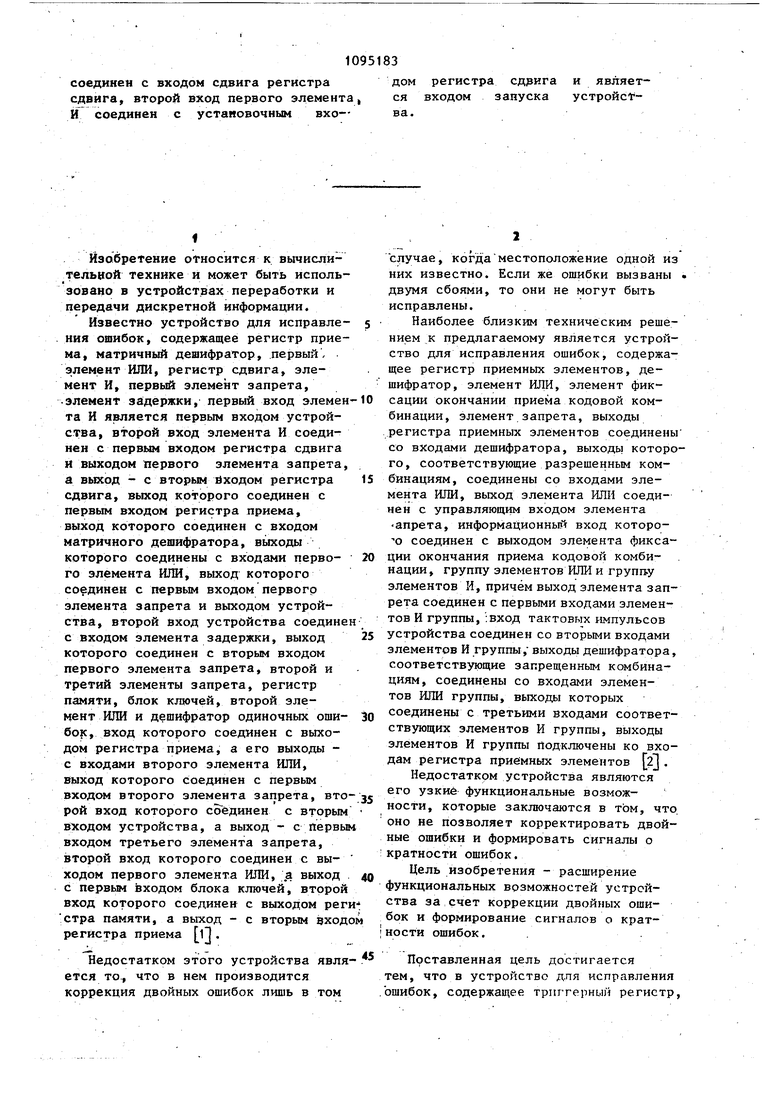

УСТРОЙСТВО ДЛЯ ИСПРАВЛЕНИЯ ОШИБОК, содержащее триггерный регистр, дешифратор, первый элемент ИЛИ, группу элементов И, группу элементов ИЛИ, причем информационные входы триггерного регистра являются информационными входами устройства, выходы дешифратора, соответствующие разрешенным комбинациям, соединены с входами первого элемента ИЛИ, выходы дешифратора, соответствующие запрещенным комбинациям с одиночной ошибкой в i -м разряде, соединены с входами i -го элемента ИЛИ группы, выход которого соединен с первым входом i-го элемента И группы, выход которого соединен со счетным входом i-го разряда триггёрного регистра, вторые входы всех элементов И группы объединены, отличающее ся тем, что, с целью расширения функциональных возможное-тей устройства путем коррекции двойных ошибок и формирования сигналов кратности ошибок, в него введены регистр сдвига, второй и третий элементыШШ, два элемента ИПИ-НЕ, четыре элемента И, элемент НЕ, два элемента задержки и группа сумматоров по модулю два, причем выходы регистра соединены с первыми входами соответствующих сумматоров по модулю два группы, выходы сумматоров по модулю два группы соединены с входами дешифратора и являются информационными входами устройства, выходы элементов ИЛИ группы соединены с входами второго элемента ИЛИ, выход которого соединен с первьш входом первого элемента ИЛИ-НЕ и является выходом одиночной оншбки устройства, выход первого элемента ИЛИ является выходом исправности устройства и соединен с вторым входом первого элемента ИЛИ-НЕ и входом элемента НЕ, выход которого g соединен с первьми входами первого и второго элементов И, выходы кото(Л рых соединены с входами третьего (Элемента ИЛИ, выход которого через первый элемент задержки соединен с (вторым входом первого элемента И группы к входом второго элемента . задержки, выход которого соединен с вторым входом второго элемента И, выходы регистра сдвига соединены со 1C вторыми входами сумматоров по О1 модулю два группы и входами второго элемента ИЛИ-НЕ, выход которого 00 соединен с первым входом третьего элемента И, выход которого соедисо нен с единичным входом младшего раз ряда регистра сдвига, первый вход четвертого элементаИ соединен с выходом второго элемента задержки, . ,выход первого, элемента ИЛИ-НЕ является выходом двойной ошибки устройства и соединен с вторыми входами третьего и четвертого элементов И, вькод четвертого элемента И

Йзобретение относится к вычислительной технике и может быть использовано в устройствах переработки и передачи дискретной информации.

Известно устройство для исправления ошибок, содержащее регистр приема, матричный дешифратор, первый, элемент ШШ, регистр сдвига, элемент И, первьй элемент запрета, элемент за:держки, первый вход элемен та И является первым входом устройства, второй вход элемента И соединен с первым входом регистра сдвига и выходом первого элемента запрета, а вьвсод - с вторым входом регистра сдвига, выход которого соединен с первым входом регистра приема, выход которого соединен с входом матричного дешифратора, выходы которого соединены с входами первого элемента ИЛИ, выход которого соединен с первым входом первого элемента запрета и выходом устройства, второй вход устройства соедине с входом элемента задержки, выход которого соединен с вторым входом первого элемента запрета, второй и третий элементы запрета, регистр памяти, блок ключей, второй элемент ИЛИ и дешифратор одиночных ошибок, вход которого соединен с выходом регистра приема, а его выходы с входами второго элемента ШШ, выход которого соединен с первым входом второго элемента запрета, вто рой вход которого соединен с вторым входом устройства, а выход - с Первы входом третьего элемента запрета, второй вход которого соединен с выходом первого элемента ИЛИ, а выход с первым входом блока ключей, второй вход которого соединен с выходом рег стра памяти, а выход - с вторым вход регистра приема .

Недостатком этого устройства явля ется то, что в нем производится коррекция двойных ошибок лишь в том

случае, когдаместоположение одной из них известно. Если же ошибки вызваны . двумя сбоями, то они не могут быть исправлены.

Наиболее близким техническим решением к предлагаемому является устройство для исправления ошибок, содержащее регистр приемных элементов, дешифратор, элемент ИЛИ, элемент фиксации окончании приема кодовой комбинации, элемент запрета, выходы регистра приемных элементов соединены со входами дешифратора, выходы которого, соответствующие разрешенным комбинациям, соединены со входами элемента ИЛИ, выход элемента РШИ соединен с управляющим входом элемента апрета, информационный вход которо-о соединен с выходом элемента фиксации окончания приема кодовой комбинации, группу элементов ИЛИ и группу элементов И, причём выход элемента запрета соединен с первыми входами элементов И группы,: вход тактовых импульсов устройства соединен со вторыми входами элементов И группы, выходы дешифратора, соответствующие эапрещенным комбинациям, соединены со входами элементов ИЛИ группы, выходы которых соединены с третьими входами соответствующих элементов И группы, выходы элементов И группы Подключены ко входам регистра приемных элементов 2.

Недостатком устройства являются его узкие функциональные возможности, которые заключаются в том, что. оно не позволяет корректировать двойные ошибки и формировать сигналы о

кратности ошибок.

Цель изобретения - расширение ункциональных возможностей устройства за счет коррекции двойных ошиок и формирование сигналов о кратости ошибок. ..

Поставленная цель достигается ем, что в устройство для исправления шибок, содержащее трпггерныи регистр. дешифратор, первый элемент ИЛИ, группу элементов И, группу элементов ИЛИ, причем информационные входы триггерного регистра являются информационными входами устройства, выход дешифратора, соответствующие разреше ным комбинациям, соединены со входами первого элемента ИЛИ, выходы дешифратора, соответствующие запреще ньт комбинациям с одиночной ошибкой в i-M разряде соединены со входами i-ro элемента ИЛИ группы, выход которого соединен с первым входом i-ro элемента И группы выход которого соединен со счетным входом i-ro разряда триггерного регистра, вторые входы всех элементов И группы объединены, введены регистр сдвига, второй и третий элементы ИЛИ, два элемента ИЛИ-НЕ, четыре элемента И,элемент НЕ, два элемента задержки и группа сумматоров по модулю дв.а, причем выходы регистра соединены с первыми входами соответствующих сумматоров по модулю два группы, выходы сумматоров по модулю два группы соединены со сходами дешифратора и являются информационными входами устройства, выходы элементов ИЛИ группы соединены со входами второго элемента ИЛИ, выход которого соеди нен с первьм входом первого элемента ИЛИ-НЕ и является выходом одиночной ошибки устройства, выход первого элемента ИЛИ является выходом исправ

ности устройства и соединен со вторым входом первого элемента ИЛИ-НЕ и входом элемента НЕ, выход которого соединен с-первыми входами первого и второго элементов И, выходы которых 40 соединены со входами третьего элемента ИЛИ, выход которого через первый элемент задержки соединен со вторым входом первого элемента И группы и входом второго элемента задержки, выход 45 которого соединен со вторым входом , второго элемента И,, выходы регистра сдвига соединены со вторыми входами сумматоров по модулю два группь и входами isToporo элемента ИЛИ-НЕ, выход15о

которого соединен с первым входом третьего элемента И, выход которого соединен с единичным входом младшего разряда регистра сдвига, первый вход , четвертого элемента И соединен с выходом второго элемента задержки, выход первого элемента ИЛИ-НЕ является выходом двойной ошибки устройства и соединен со вторыми входами третьеполагается, что поступившее слово закодировано с помощью избыточного кода, позволяющего исправлять двойные ошибки (т.е. кодовое расстояние не

Если в принятом слове нет ошибок, 1 то записанное в регистр 1 слово без изменений через сумматоры 2 по модулю два группы поступает на входы дегдифратора 3. На одном из выходов дешифратора, которые соединены со входами элемента ИЛИ 5, имеется единичный уровень. Этот единичный сигнал го А четвертого элементов И, выход четвертого элемента И соединен со входом сдвига регистра сдвига, второй вход первого элемента И соединен с устано вочным входом регистра сдвига и является входом запуска устройства. На чертеже приведена структурная схема устройства для исправления ошибок. В состав устройства для исправлениг ошибок входят триггерный регистр 1, группа 2 сумматоров по модулю два, дешифратор 3, группа 4 элементов ИЛИ, первый элемент ИЛИ 5, второй элемент ДИ 6, первый и второй элементы ИЛИ-НЕ 7 и 8, третий и четвертый элементы И 9 и 10 группа 11 элементов И, регистр 12 сдвига, элемент НЕ 13, вход 1Л сдвига регистра 12 сдвига , информационные входы 15 устройства, информационные выходы 16 устройства, выход 17 исправности устройства, выход 18 одиночной ошибки устройства, выход 19 двойной ошибки уст- . ройства, вход 20 запуска устройства, первый и второй элементы И 21 и 22, третий элемент ИЛИ 23, .первый и второй элементы задержки 24 и 25. Устройство работает следующим образом. В исходном состоянии регистр 1 и регистр 12 сдвига обнулены. На информационные входы 15 устройства поступает декодируемое слово и записывается в регистр 1. Далее предменьше пяти). После приема слова в регистр 1 на вход 20 запуска устройства подается единичный импульс, свидетельствующий о начале декодирования слова. По этому сигналу производится обнуление регистра12 сдвига и при наличии ошибок их исправление. Процесс функционирования устройства при трех различных ситуациях которые могут возникнуть при декодировании слова, следующий. j10 поступает на выход 17 исправности устройства и свидетельствует о том, что с информационных выходов 16 устройства можно считывать декодированное слово. Одновременно этот сигнал поступает на вход элемента НЕ 13. За счет этого элементы И 21 и 22 закрыты. На выходах 18 и 19 уст ройства в этой ситуации код О, Если в принятом слове одна ошибка то слово также из регистра 1 без изм нений через сумматоры 2 по модулю два группы поступает на входы дешифратора 3. На одном из выходов дешифратора 3, соединенном с соответствую щим элементом ИЛИ 4 группы, появляется единичный сигнал. Этот сигнал поступает на соответствующий элемент И 11 группы и через элемент ИЛИ 6 на выход 18 одиночнойошибки устройства, свидетельствуя о аличии одиночной ошибки. На выходах 17 и 19 при этом код О. Единичный сигнал с входа 20 запуска устройства поступает на второй вход элемента. И 21 и открывает его, так как с выхода элемента НЕ 13 поступает код 1. Единичный сигнал через элемент ИЛИ 2 и элемент задержки 24 открывает один из элементов И 11 группы, соответс-вв ющий разряду, принятому с искажением и в регистре 1 произв:одится исправление искаженного разряда путем инвертирования за счет подачи сигнала на счетный вход триггера. На одном из выходов дешифратора 3, соединенно со входами элемента ИЛИ 5, появляетс единичный уровень, который выдается на выход 17 устройства, свидетельств об окончании декодирования слова. Од новременно на выходе элемента НЕ 13 появляется код О, который закрывае элементы И 21 и 22. Декодированное слово выдается на выход 16 устройства. I . .,.-,,Если в принятом слове две ошибки, то ни на одном выходе дешифратора 3 не будет единичного сигнала. На выхо дах элементов: ИЛИ 4 группы элемента ИЛИ. 5 и элемента ИЛИ 6 код О. На выходе элемента ИЖ-НЕ 7, и следовательно, на выходе 19 устройства код который свидетельствует .о наличии двойной ошибки. Регистр 12 сдвига предварительно обнулен сигналом Со входа 20 запуска устройства. Поэтому на выходе элемента ИЛИ-НЕ,8 код 1 и единичный уровень с выхода 36 элемента ИЛИ-НЕ 7 открывает Злемент И 9 и производится запись единицы в младший разряд регистра сдвига 12. Рассмотрим два случая: одна из ошибок возникли в младшем разряде принятого слова; в младшем разряде принятого слова нет ошибок. Младшие разряды принятого слова располагаются в разрядах регистра 1, показанных справа. В первом случае появление 1 на выходе младшего разряда регистра 12 сдвига приводит к тому, что младший искаженный разряд принятого слова с помощью соответствующего сумматора 2 по модулю два инвертируется. При этом на выходе сумматоров 2.по модулю два группы появляется слово, содержащее всего лишь одну ошибку. Поэтому на соответствующем выходе дешифраторов 3 появляется код 1, который поступает на вход одного из элементов ИЛИ 4 группы с появлением кода 1 на выходе первого элемента 24 задерж-. ки открывается один из элементов И 11 группы, и вторая ошибка исправляется. На одном из выходов дешифратора 3, соединенном со входами элемента ИЛИ 5, появляется единичный сигнал, которьй проходит на выход элемента РШИ 5 и свидетельствует об окончаНИИ декодирования принятого слова. Одновременно код О с выхода эле мента НЕ 13 поступает напервые входы элементов И 21 и 22 и закрывает их. Кроме того, код О с выхода элемента ИЛИ-НЕ 7 поступает на вход элемента И 10 и запрещает прохождение единичного сигнала с выхода второго элемента 25 задержки в шину сдвига регистра 12 сдвига. Исправленное слово выдается ни выход 16 устройства. При этом младший разряд слова корректируется за счет наличия 1 в младшем разряде регистра 12 сдвига, а другой искаженный разряд проинвертирован за счет подачи кода 1 на соответствующий триггер регистра 1. Когда при двойкой ошибке в младшем разряде принятого слова нет ошибки, то появление 1 в младшем разряде регистра 12 не приводит к появлению на выходе сумматоров 2 по модулю два группы слова, которое имеет один искаженный разряд. Следовательно, на всех выходах дешифратора 3 код О, Единичный сигнал .с выхода элемента ИЛИ-НЕ 7 разрешает прохождение кода 1 с выхода второго элемента 25 эадержки через элемент И шТ По

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Устройство для исправления ошибок | 1978 |

|

SU736104A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Устройство для исправления одиночных ошибок | 1975 |

|

SU614437A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1984-05-30—Публикация

1983-03-17—Подача