1

Изобретение относится к вычислительной технике и южет быть использовано в устройствах переработки и передачи дискретной информации.

Известно устройство, содержащее регистр приема, двухступенчатую матрицу и элементы ИЛИ, позволяющее эффективно корректировать одиночные ошибки 1 .

Недостаток устройства - невозможность исправления двойных ошибок.

Наиболее близким к изобретению является устройство, содержащее регистр приема, матрицу, регистр сдвига, элемент И, элемент ИЛИ, элемент запрета, элемент фиксации окончания приема кодовой комбинации, выход которого соединен с первым входом элемента запрета, второй вход которого соединен с выходом элемента ИЛИ, а выход с первыми входами регистра сдвига и элемента И, второй вход которого соединен со входом уст ройотна, третий вход - с выходом регистра сдвига, а выход - с вторым входом регистра сдвига, группа выходов последнего соединена с группой входов регистра приема, выходы которого соединены с соответствующими входами матрицы, выходы которой соединены со входами элемента ИЛИ.

Недостаток устройства - возможность исправления лишь одиночных 5 оши бо к.

Цель изобретения - расширение функциональных возможностей,заключающихся в коррекции двойных ошибок. Поставленная цель достигается тем,

10 что в устройство, содержащее регистр приема, матричный дешифратор, первый элемент ИЛИ, регистр сдвига, элемент И, первый элемент запрета,элемент задержки, первый вход элемента И

15 является первым входом устройства, второй вход элемента И соединен с первым входом регистра сдвига и выходом первого элемента запрета, а выход - с втбрым входом регистра

20 сдвига, выход которого соединен с первым входом регистра приема, выход которого соединен с входом матричного дешифратора, выходы которого, соединены с входами первого элемента

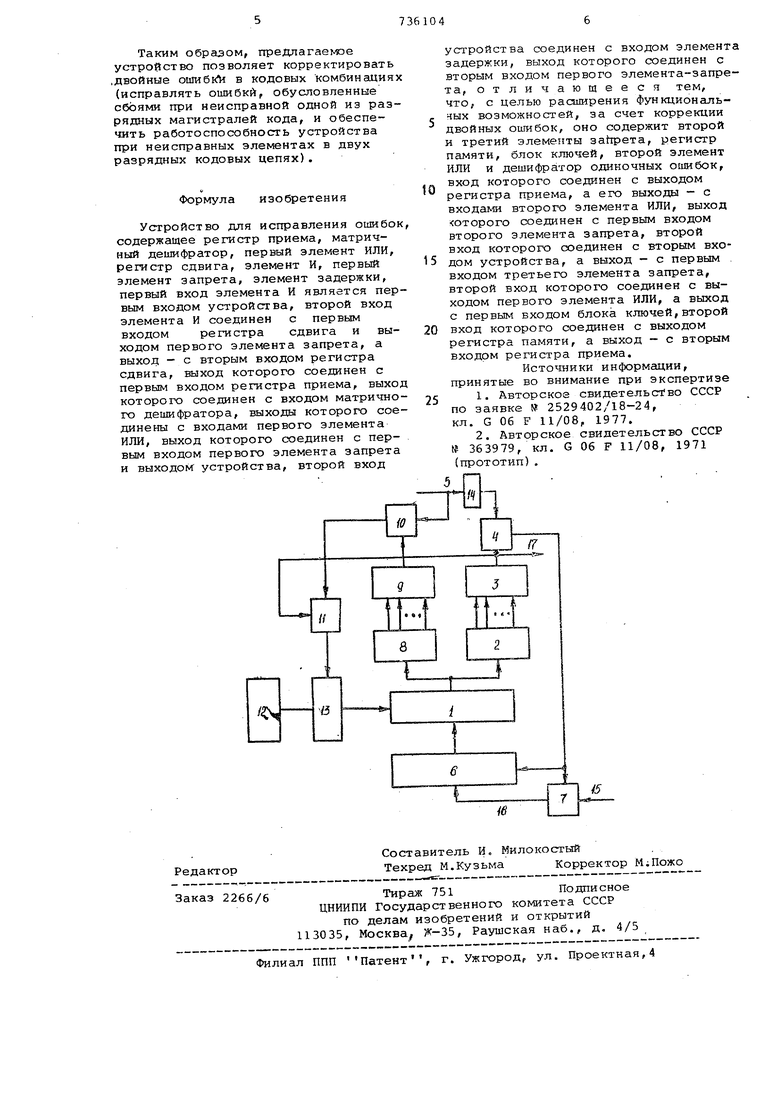

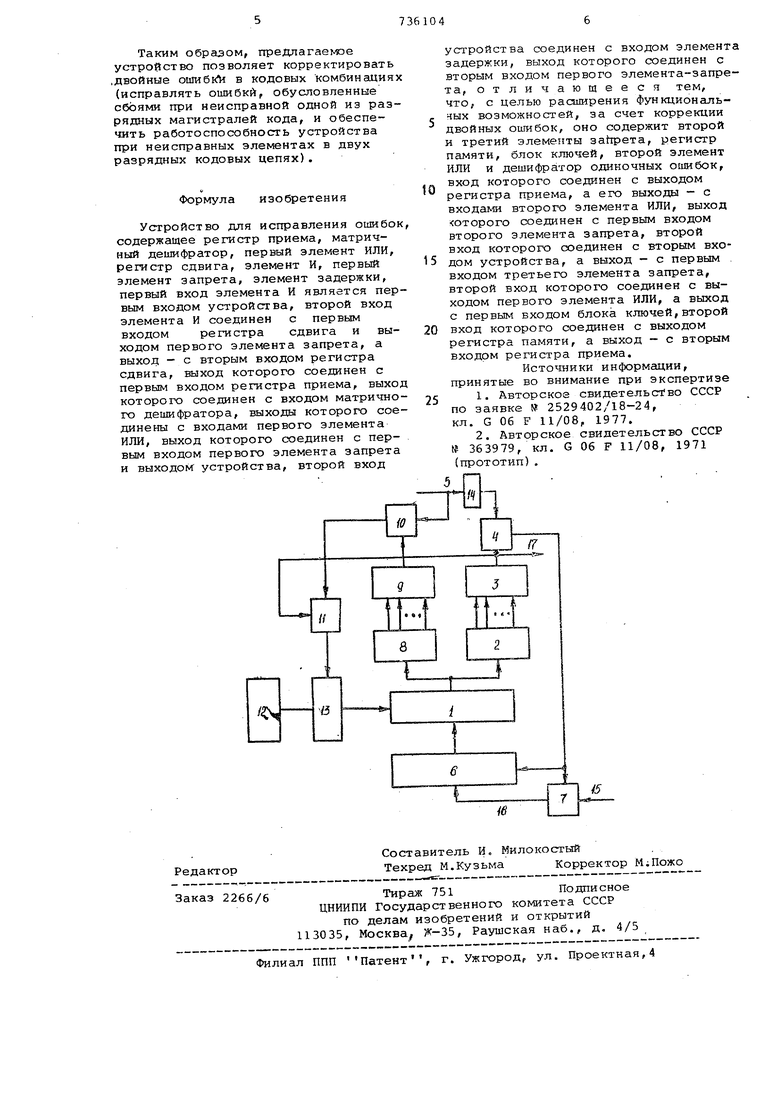

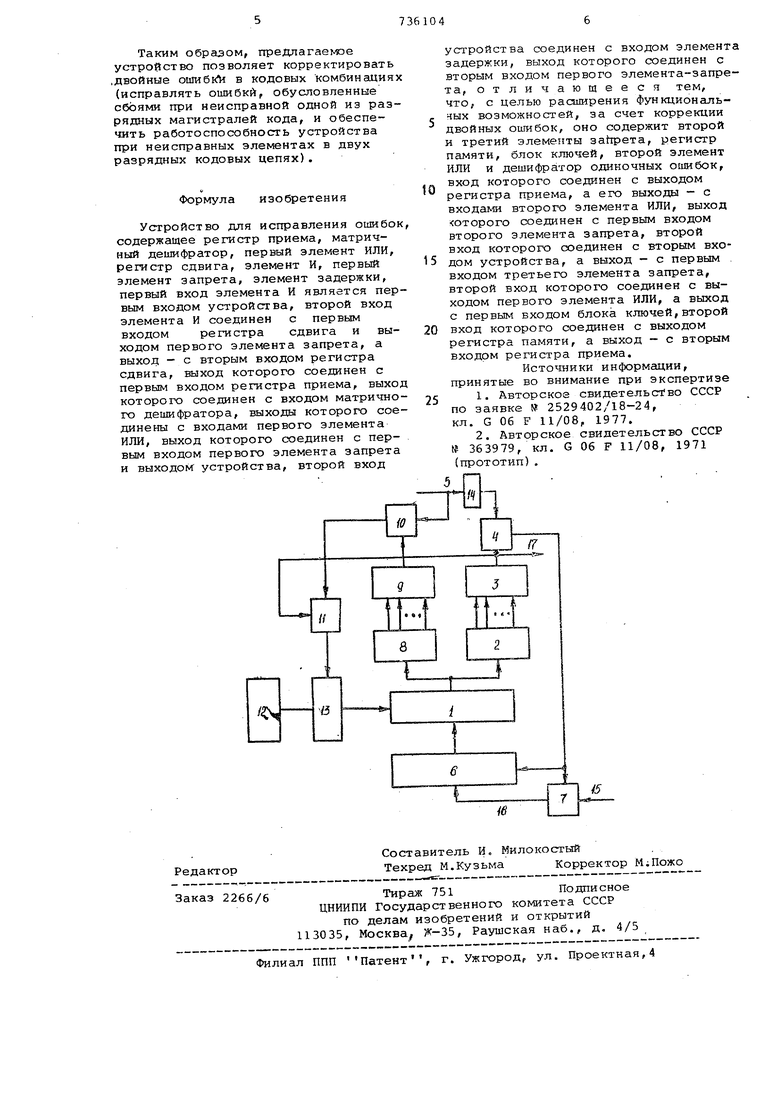

25 ИЛИ, выход которого соединен с первым входом первого элемента запрета и выходом уегройства, второй вход устройства соединен с -входом элемента задержки, дополнительно введены второй и третий элементы запрета регистр памяти, группу ключей, второй элемент ИЛИ и дешифратор одиноч ных ошибок, вход которого соединен с выходом резгистра приема, а его выходы - с входами второго элемента ИЛИ, выход которого соединен с первым входом второго элемента аащ)ета второй вход которого соединен с вторым входом устройства, а выход - с первым входом третьего элемента запрета, второй вход которого соеди нен с выходом первого элемента ИЛИ, а выход - с первым входом групшл ключей, второй вход которого соединен с влходом регистра памяти, а выход - с вторым входом регистра приема. На чертеже приведена структу1эная схема устройства. Устройство содержит регистр 1 при ема, матричный дешифратор 2, первый элемент ИЛИ 3, первый элемент 4 запрета, шину 5 начало коррекции , регистр б сдвига, элемент И 7, дешифратор 8 одиночных ошибок, второй элемент ИЛИ 9, - второй и третий эле менты 10 и 11 запрета, регистр 12 памяти, группу ключей 13, элемент 1 задержки, шину 15 тактовых импульсо сдвигающую шину 16 и шину 17 окончание коррекции Дешифратор 8 одиночных ошибок построен аналогично матричному дешифратору 2, представляющий собой фактически дешифратор рабочих кодовых комбинаций. Регистр 12 памяти предназначен для запоминания номера разряда, искажение информации в котором наблюда ется устойчиво. Регистр 12 кодовым ,1 имнами через ключи 13 соединен.с регистром 1 приема. Управляющей сигнал на открытие ключей 13 поступает из третьего элемента 11 запрета. Элемент 14 задержки предназначен для задержки сигнала начало коррекции на время, необходимое для пересылки содержимого регистра 12 памяти на регистр приема в случае, когда в кодовой комбинации содержит .два и более искаженных символа. Устройство работает следующим об разом. Перед приемом кодовой комбинации регистр 1 приема устанавливается в ноль. Если принятая кодовая комбинация ошибки не содержит, то на выхо де матричного деишфратора 2 возбуждается шина,соответствующая принятой рабочей кодовой комбинации. На выход элемента ИЛИ 3 формируется единичный сигнал, который запрещает прохождение сигнала начало коррекции через элемент запрета. На шине 17 окончание коррекции устанавливается единичный сигнал. Пусть поступила кодовая коме5инация, имеющая одиночную ошибку, В этом случае возбуждается одна из шнн леишфратора 8 одиночных оамбок 8, на выходе элемента ИЛИ 9 формируется рдиничный сигнал, который запрещает прохождение сигнала начало коррекции через элемент 10 запрета.. Сигнал начало коррекции проходит через элемент 4 запрета, переводит в единичное состояние младший разряд регистра 6 сдвига и обеспечивает прохождение тактовых импульсов через элемент И 7, Тактовые импульсы, поступающие по шмне 16 как импульсы сдвига, обеспечивают перемещение единицы в регистре сдвига, последовательно инвертируя содержимое разрядов регистра 1. Каждый приемный элемент регистра 1 изменяет свое состояние при записи 1 в связанный с ним разряд регистра сдвига и возвращается в исходное состояние при записи в этот разряд О, Как только в результате этой коррекции будет получен правильный код (рабочая кодовая комбинация), возбуждается одна из шин матричного дешифратора 2, на выходе логической схемы ИЛИ 3 устанавливается единичный сигнал, а на выходе элемента 4 запрета - нулевой сигнал. Последний прекращает прохождение тактовых импульсов с шины 15 через элемент И на шину 16 сдвига. На шине окончание коррекции устанавливается единичный сигнал. Если ошибка в одНом и том же разряде повторяется несколько раз, что свидетельствует о наличии устойчивого отказа (неисправности кодовой шины), то в соответствующий разряд регистра 12 памяти заносится единица. При наличии единицы в одном из разрядов регистра 12 памяти и отсутствии ошибок в кодовой комбинации или в других разрядах кодовой комбинации, работа устройства не отличается от изложенного выше. В том случае, когда имеет место двойная ошибка, ни одна из шин матричного дешифратора 2 и дешифратора 8 не возбуждаются. Сигнал начало коррекции с шины 5 через элементы 10 и 11 запрета поступает на управляющие входы ключей 13. Ключи 13 открываются и содержимое регистра 12 памяти поступа ет в регистр 1 прием-ных элементов, изменяя состояние соответствующего элемента памяти (выполняется операция поразрядного сложения по модулю 2). В результате двойная ошибка сводится к одиночной. Этот же сигнал с шины 5, задержанный элементом 14 задержки на время коррекции кода в рег-истре , поступает через элемент 4 запрета на регистр 6 сдвига и схему И 7. Далее устройство работает так же как и при наличии одиночной ошибки в кодовой комбинации.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для исправления ошибок | 1982 |

|

SU1027730A1 |

| Устройство для исправления ошибок | 1983 |

|

SU1095183A1 |

| УСТРОЙСТВО ДЛЯ ИСПРАВЛЕНИЯ ОДИНОЧНЫХ ОШИБОК | 1973 |

|

SU363979A1 |

| Устройство для исправления одиночных ошибок | 1977 |

|

SU648982A1 |

| Устройство для приема дискретной информации, закодированной корректирующим кодом | 1987 |

|

SU1462492A1 |

| ДЕКОДИРУЮЩЕЕ УСТРОЙСТВО | 1991 |

|

RU2037272C1 |

| СПОСОБ СИНХРОНИЗАЦИИ КОДОВЫХ КОМБИНАЦИЙ | 2023 |

|

RU2812335C1 |

| УСТРОЙСТВО СИНХРОНИЗАЦИИ КОДОВЫХ КОМБИНАЦИЙ | 2023 |

|

RU2810267C1 |

| Устройство для обнаружения и исправления ошибок | 1985 |

|

SU1368995A1 |

| УСТРОЙСТВО СИНХРОНИЗАЦИИ НА ОСНОВЕ МАТРИЧНОЙ ОБРАБОТКИ И ДЕЦИМАЦИИ РЕКУРРЕНТНОЙ ПОСЛЕДОВАТЕЛЬНОСТИ | 2023 |

|

RU2820337C1 |

Авторы

Даты

1980-05-25—Публикация

1978-02-28—Подача