соединены с вькодом второго триггера и через третий элемент И с третьим входом счетчика, выход которого соединен с первым входом второго триггера, вторюй вход которого через первый элемент И соединен с четвертгдм входом блока и,входом второго элемента И, выход первого триггера соединен с выходом блока и входом третьего элемента И.

| название | год | авторы | номер документа |

|---|---|---|---|

| Многоканальная система для контроля и диагностики цифровых блоков | 1984 |

|

SU1269137A1 |

| Устройство для вывода информации | 1981 |

|

SU993236A1 |

| Устройство для функционального контроля цифровых блоков | 1989 |

|

SU1656538A1 |

| Устройство для индикации | 1985 |

|

SU1261005A1 |

| Мультиплексный канал | 1980 |

|

SU957199A1 |

| Устройство для обработки сейсмической информации | 1984 |

|

SU1208561A1 |

| Система ввода-вывода для микропрограммируемой ЭВМ | 1988 |

|

SU1667084A1 |

| Устройство для приема и обработки команд телеуправления | 1989 |

|

SU1667137A1 |

| Устройство для сопряжения цифровой вычислительной машины с периферийными устройствами | 1980 |

|

SU962899A1 |

| Устройство для ввода информации | 1983 |

|

SU1145336A1 |

1. УСТРОЙСТВО ДЛЯ СОПРЯЖЕНИЯ, содержащее блок ввода, информационный и установочный входл которого являются входаг и устройства, первый выход которого соединен с первым управляющим выходсда блока ввода, второй управляющий выход которого соединен с первьзми входами первого коммутатора, буферной памяти и блока управления, первый и второй выходы которого соединены с тактовыми входами блока ввода, первый информационный выход которого соединен с вторым входом первого коммутатора, выход которого соединен с первым входом второго коммутатора, выход которого соединен с входом буферной памяти, третий вход которой соединен с вторым инфо ационнь 1 выходом блока ввода, генератор, вы- ход которого соединен с вторьм входе блока управления и первьвл входом регистра сдвига, выход которого через суг/алатор соединен с вторым выходом устройства, вторюй вход регистра сдвига соединен с третьим выходсм блока управления, входом распределителя и первым входом первого счетчика, выход которого соединен с вторь 1 входом второго коммутатора, третий вход которого соединен с четвертым выходом блока управления и вторым входом первого счетчика, первый, второй и третий выходы распределителя соединены соответственно с входом сумматора, первым входе второго счетчика и третьим входом блока управления, пятый и третий выходы которого соединены соответственно с третьим входом первого коммутатора и вторым входом второго счетчика, выход которого соединен с четверть входом первого коммутатора, шестой и седьмой выхогил блока управления соединены с четвертью и пятьвл входами буферной памяти, отличающеес я тем, что/ с целью упрощения S устройства и повышения коэффициента использования оборудования, в него сл введены блок формирования команд за- , держек и регистр, причем выход буфер- .ной памяти через регистр соединен с третьим входе регистра сдвига и первьэ входом блока формирования команд Зсщёржек, выход которого соединен с четвертым входом регистра сдвига и четвертым входом управления, восьмой выход которого соединен с входсяи регистра и вторым оо о входом блока формирования команд задержек, третий и четвертый входа которого соединены соответственно с третьим выходом управления блока CD управления и третьим выходом распределителя . 2. Устройство по п.1, отличающееся тем, что блок форми рования команд задержек содержит счетчик г два триггера, три элемента И, причем выход блока соединен с информациэнным входом счетчика и первым 3XORCM первого элемента Н, второй : ход которого соединен с вторым входом блока, третий вход которого соединен через второй элемент И с первыми входами счетчика и пер-аого триггера, вторые входы которых

Изобретение относится к вычислительной технике и может быть испольэовано для сопряжения вычислительной машины с абонентским пультом, например дисплеем.

Известно устройство, содержащее блок ввода, блок управления, счеТчики, регистр сдвига, генератор, коммутаторы, блок синхронизацииti.

Недостатком устройства является значительный объем оборудования и сложность организации при решении задачи отображения.

Наиболее близким к изобретению по технической сущности является устройство, содержащее блок ВЕюда, информационный и установочный входы которого являются входами уст1хэйства| первый выход которого соединен с первым управляющим выходом блока ввода, второй упрашляииций выход которого соединен с первыми входами первого коммутатора, буферной памяти и блока управления, первый и второй выходы которого соединены с тактовьми входами блока ввода, первый информационный выход которого соединен с вторым входом первого коммутатора, выход которого соединен с первым входсм второго коммутатора, выход которого соединен с вторшл входом буферной памяти, третий вход которой соединен с вторым информационньш входом блока ввода, генератор, выход которого соединен с вторым управляюЙ1ИМ -входом блока управления и первым входом регистра сдвига, выход которого через сушлатор соединен с втораом выходе устройства/ второй вход регистра сдвига соединен с третьим выходом блока управления, входом распределителя и первым вхоцом первого счетчика, выход которого соединен с четвертым выходом блока управления, и BToptatA входсйй первого счетчика, первый, второй и третий выходы распределителя соединены сответственно с входе сукалатора, ервьм входом второго счетчика и ретьим входом блока управления, пяый и третий выходы которого соедиеиы соответственно с третьим вхоом перйого коммутатора и ходом второго счетчика, выход KOTOI ого соединен с четвертым входом

первого коммутатора, шестой и седьмой выходы блока управления соединены с четвертым и пятым входами буферной памяти 2.

Недостатком известного устройства является требование большого объема буферной памяти, что усложняет устройство и снижает его эффективность,

Целью изобретения является упрощение устройства и повышение коэффициента использования оборудования.

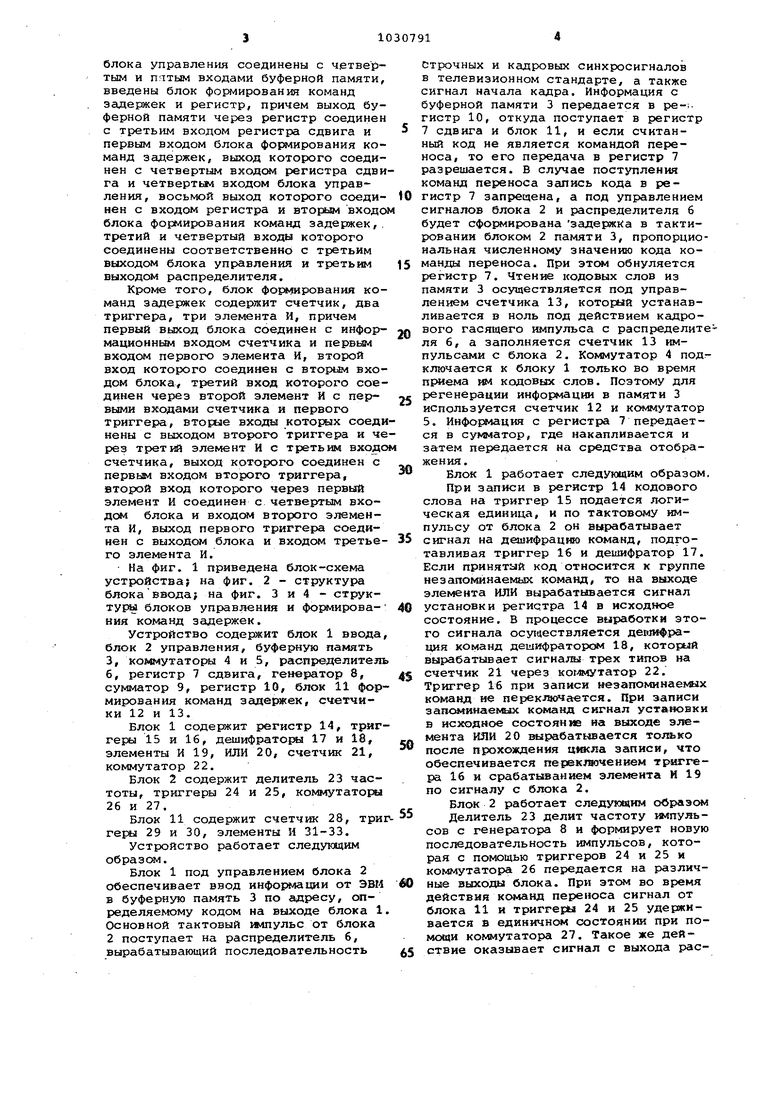

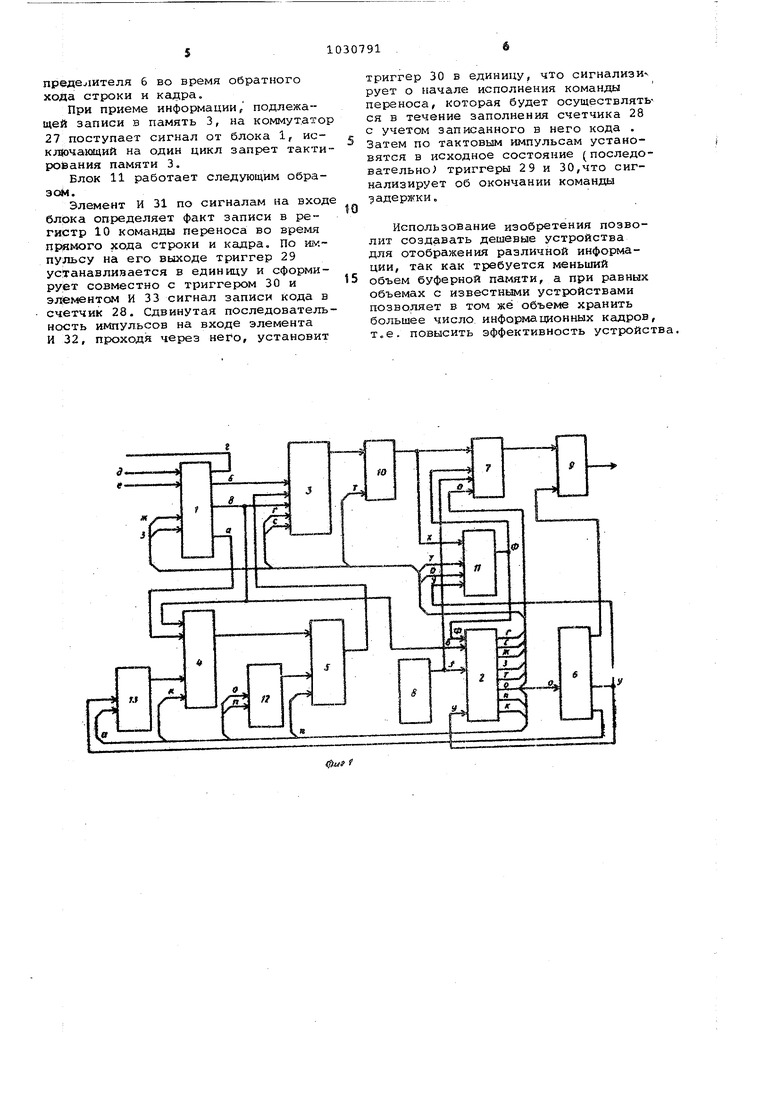

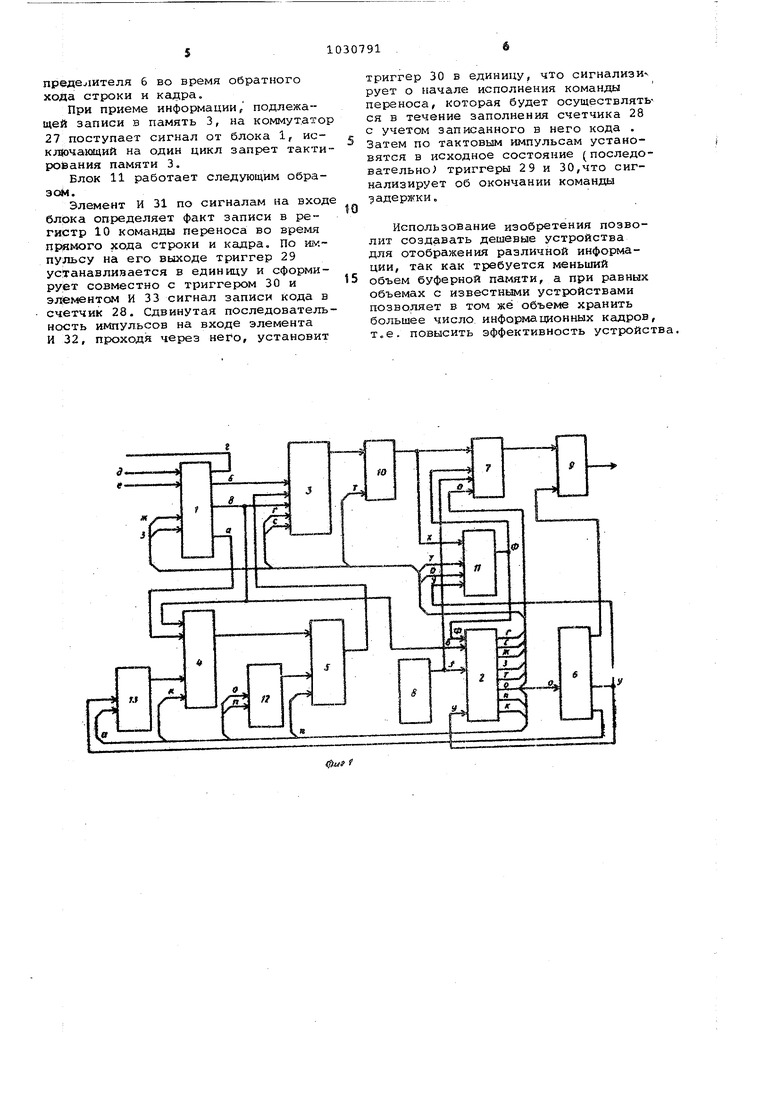

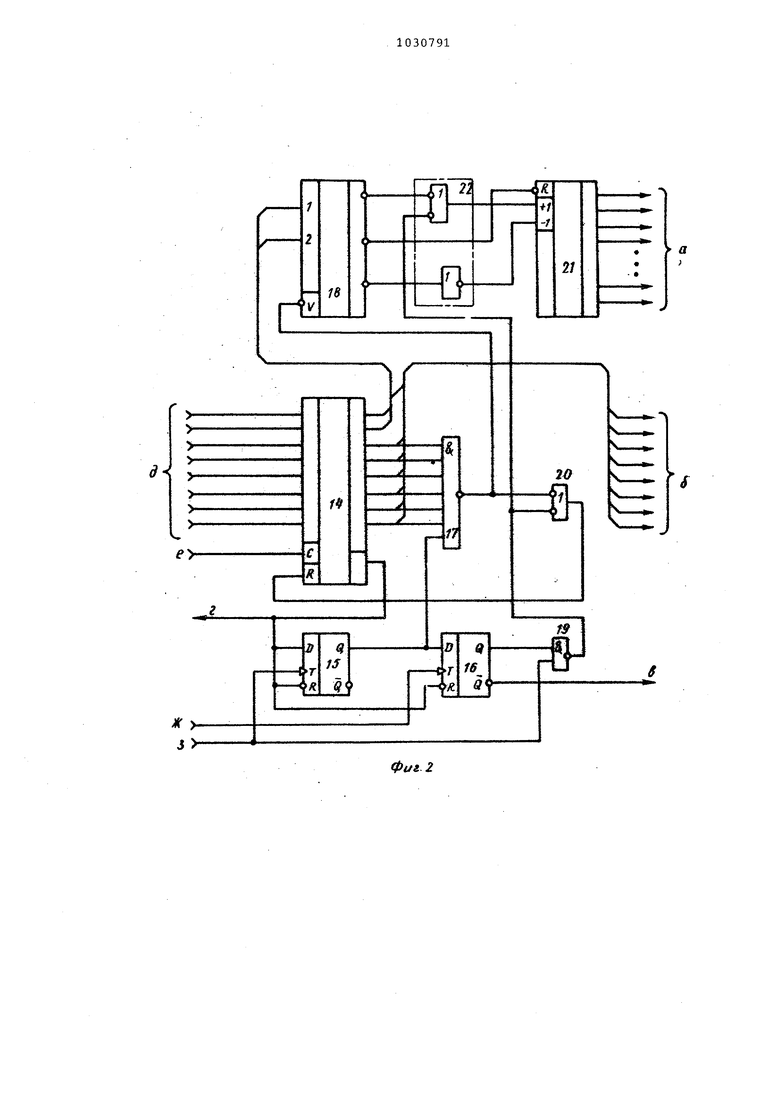

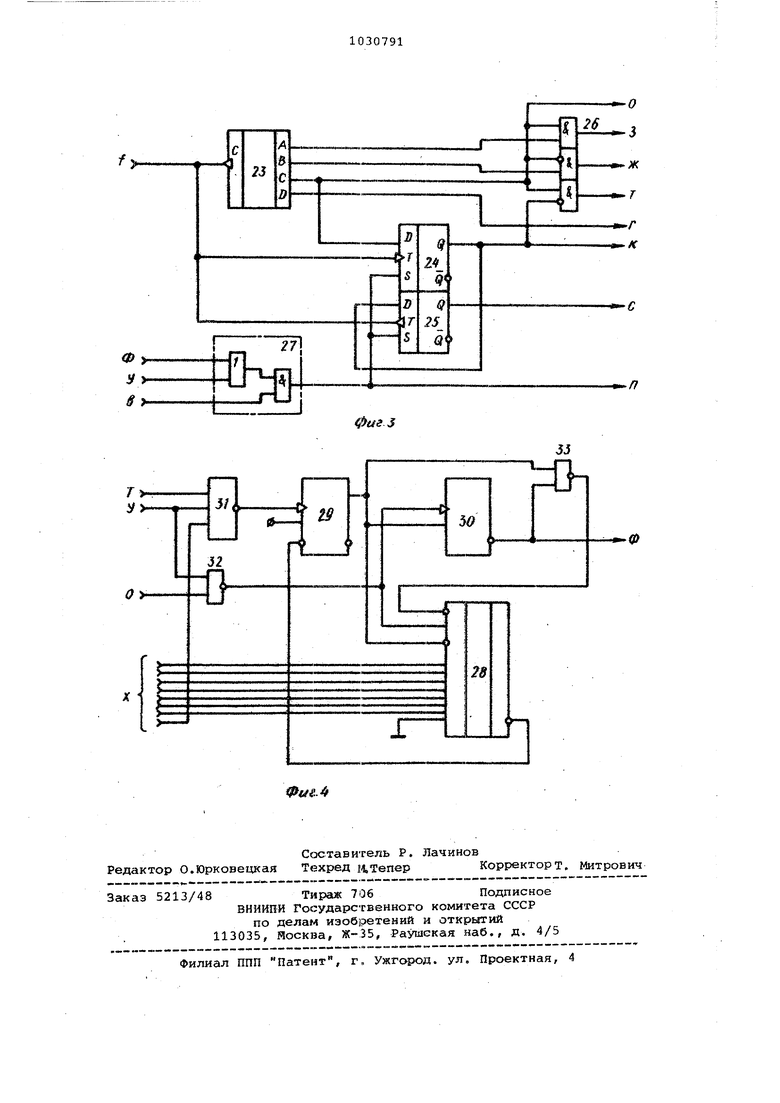

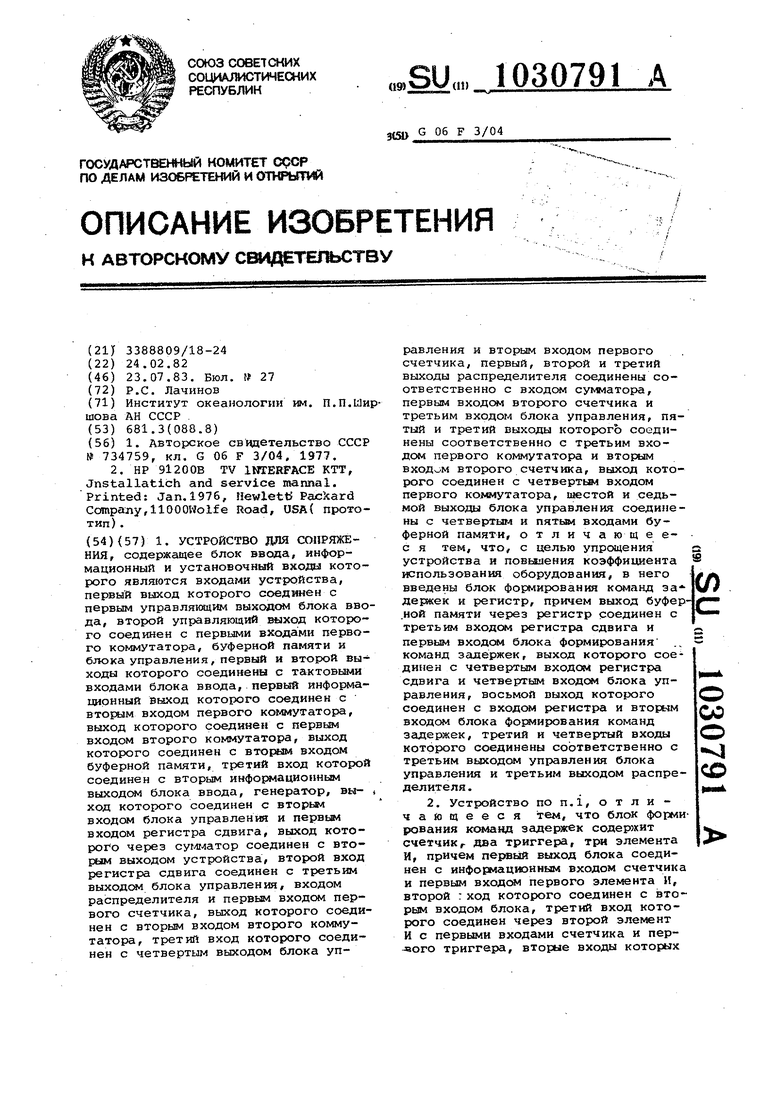

ГЕоставленная цель достигается тем, что в устройство, содержащее блок ввода, информационный и установочный входы которого являются входами устройства, первый выход которого соединен с первым управляющим выходом блока ввода, второй управляющий выход которого соединен с первыми входами первого ког мутатора, буферной памяти и блока управленш, первый и второй выходы которого соединены с тактов1 и входамиблока ввода, первьнй информационный выход которого соединен с вторым входом первого кок1мутатора, выход которого соединен с первым входом второго коммутатора, выход которого соединен с вторым входом буферной памяти, третий вход которой соединен с BTOE«IM информационньа выходом блока ввода, генератор, выход которого соединен с вторым входом блока управления и первым входом регистра сдвига, выход которого через сумматор соединен с выходом устройства, второй вход регистра сдвига соединен с третьим выходом блока управления, входом распределителя и первьяч входо первого счетчика, выход которого соединен с вторым входом второго коммутатора, третий вход которого соединен с четвертым выходом блока управления и вторым входом первого счетчик-а, первый, второй и третий выходы распределителя соединены соответственно с входом сумматора, пер входом второго счетчика и третьWM входсм блока управления, пятый и третий выходы которого соединены соответственно с третьим входсй кс шутатора и вторым входсм второго счетчика, выход которого .соединен с четвертым входом первргО коммутатора, шестой и седьмой выходы блока управления соединены с четвертым и пятым входами буферной памяти введены блок формирования команд задержек и регистр, причем выход буферной памяти через регистр соединен с третьим входом регистра сдвига и первым входом блока формирования команд задержек, выход которого соединен с четвертым входом регистра сдви га и четверть входом блока управления, восьмой выход которого соедийен с входом регистра и вторым входо блока формирования команд задержек, третий и четвертый входы которого соединены соответственно с третьим выходом блока управления и третьим выходом распределителя. Кроме того, блок формирования команд задержек содержит счетчик, два триггера, три элемента И, причем первый выход блока соединен с информационньйм входом счетчика и первьал входом первого элемента И, второй вход которого соединен с вторым входом блока, третий вход которого сое динен через второй элемент И с первыми входами счетчика и первого триггера, вторые входы которых соеди нены с выходом второго триггера и че рез третий элемент И с третьим входо счетчика, выход которого соединен с первьач входом второго триггера, второй вход которого через первый элемент И соединен с четвертым входом блока и входов второго элемента И, выход первого триггера соединен с выходом блока и входом третье го элемента И. На фиг. 1 приведена блок-схема устройства на фиг. 2 - структура блока ввода; на фиг. 3 и 4 - струкТУЕ блоков управления и фор 1ирования команд задержек. Устройство содержит блок 1 ввода блок 2 управления, буферную память 3, коммутаторы 4 и 5, распределитезрг б, регистр 7 сдвига, генератор 8, сумматор 9, регистр 10, блок 11 фор мирования команд задержек, счетчнки 12 и 13. Блок 1 содержит регистр 14, триг геры 15 и 16, дешифрато1ял 17 и 18, элементы И 19, ИЛИ 20, счетчик 21, коммутатор 22. Блок 2 содержит делитель 23 частоты, триггеры 24 и 25, коммутатор 26 и 27. Блок 11 содержит счетчик 28, три геры 29 и 30, элементы И 31-33. Устройство работает следующим образом. Блок 1 под управлением блока 2 обеспечивает ввод информации от ЭВМ в буферную память 3 по адресу, сятределяемому кодом на выходе блока 1 Основной тактовый илпульс от блока 2 поступает на распределитель 6, вырабатывающий последовательность Строчных и кадровьк синхросигналов в телевизионном стандарте, а также сигнал начала кадра. Информация с буферной памяти 3 передается в ре-;, гистр 10, откуда поступает в регистр 7 сдвига и блок 11, и если считанный код не является командой переноса, то его передача в регистр 7 разрешается. В случае поступления команд переноса запись кода в регистр 7 запресчена, а под управлением сигналов блока 2 и распределителя 6 будет сформирована задеркка в тактировании блоком 2 памяти 3, пропорциональная численному значению кода команды переноса. При этом обнуляется регистр 7. Чтение кодовых слов из памяти 3 осуществляется под управлением счетчика 13, который устанавливается в ноль под действием кадрового гасящего импульса с распределителя 6, а заполняется счетчик 13 импульсами с блока 2. Коммутатор 4 подтключается к блоку 1 только во время приема №4 кодовых слов. Поэтому для регенерации информации в памяти 3 используется счетчик 12 и коммутатор 5. Информация с регистра 7 передается в сумматор, где накапливается и затем передается на средства отображения. Влок 1 работает следующим образом. При записи в регистр 14 кодового слова на триггер 15 подается логическая единица, и по тактовому импульсу от блока 2 он вырабатывает сигнал на дешифрацию команд, подготавливая триггер 16 и дешифратор 17. Если принятый код относится к группе не запоминаемых команд, то на виисоде элемента ИЛИ вырабатывается сигнал установки регистра 14 в исходное состояние. В процессе выработки этого сигнала осу Е1ествляется девя фрация команд дешифратором 18, который вырабатывает сигналы трех типов на счетчик 21 через ког-ямутатор 22. Триггер 16 при записи еэапоминаемых команд не переключается. При записи 3агюминаег«лх команд сигнал установки в исходное состояние иа выходе элемента ИЛИ 20 вырабатывается fof&KO после прохождения записи, что обеспечивается nepeKJW34eHKeM триггера 16 и срабатыванием элемента И 19 по сигналу с блока 2. Блок 2 работает следующим образом Делитель 23 делит частоту импульсов с генератора 8 и формирует новую последовательность импульсов, которая с помощью триггеров 24 и 25 и коммутатора 26 передается на различные выходы блока. При этсм во время действия команд переноса сигнал от блока 11 и триггеры 24 и 25 удерживается в единичном состоянии при помощи KONwyTaTopa 27. Такое же действие оказывает сигнал с выхода расnpeflSjiHTenH 6 BO время обратного хода строки и кадра,

При приеме информации, подлежащей записи в память 3, на коммутатор 27 поступает сигнал от блока 1, исклЧочающий на один цикл запрет тактирования памяти 3,

Блок 11 работает следующим образом.

Элемент И 31 по сигналам на входе блока определяет факт записи в регистр 10 команды переноса во время П1ЖМОГО хода строки и кадра. По И1У. пульсу на его выходе триггер 29 устанавливается в единицу и сформирует совместно с триггером 30 и элементом И 33 сигнал записи кода в счетчик 28. Сдвинутая последовательность импульсов на входе элемента И 32, проходя через него, установит

триггер 30 в единицу, что сигнализи-. рует о начале исполнения команды переноса, которая будет осуществляться в течение заполнения счетчика 28 с учетом зап1«закного в него кода . Затем по тактовым импульсам установятся в исходное состояние (последовательно) триггеры 29 и 30,что сигнализирует об окончании команды радерлски.

Использование изобретения позволит создавать дешевые устройства для отображения различной информации, так как требуется меньший объем буферной памяти, а при равных объемах с известнь&ли устройствами позволяет в том же объеме хранить большее число информаодонных кадров, т„е. повысить эффективность устройст

1

2

21

а

)

2/

18

Р

д

f

2д

/

F/1

В IS

9 16

it

2

фаг

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Устройство для отображения информации | 1977 |

|

SU734759A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Шеститрубный элемент пароперегревателя в жаровых трубках | 1918 |

|

SU1977A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Электронно-лучевой индикатор | 1950 |

|

SU91200A1 |

| Printed: Jan | |||

| Планшайба для точной расточки лекал и выработок | 1922 |

|

SU1976A1 |

Авторы

Даты

1983-07-23—Публикация

1982-02-24—Подача