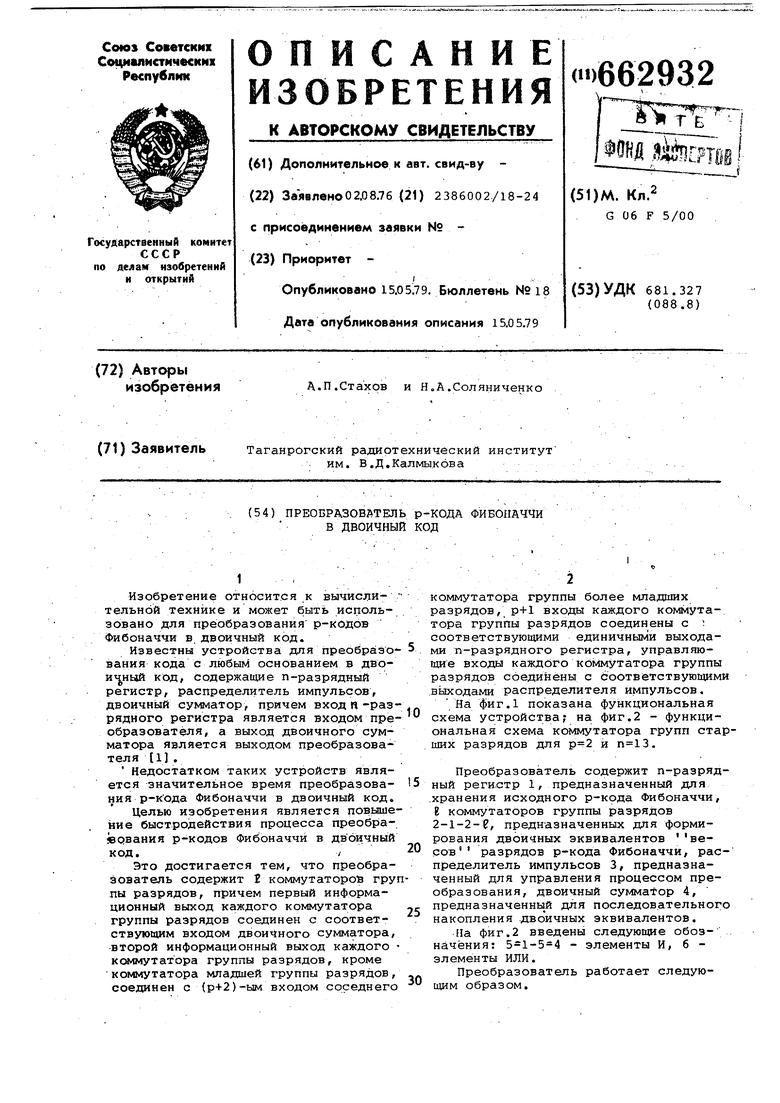

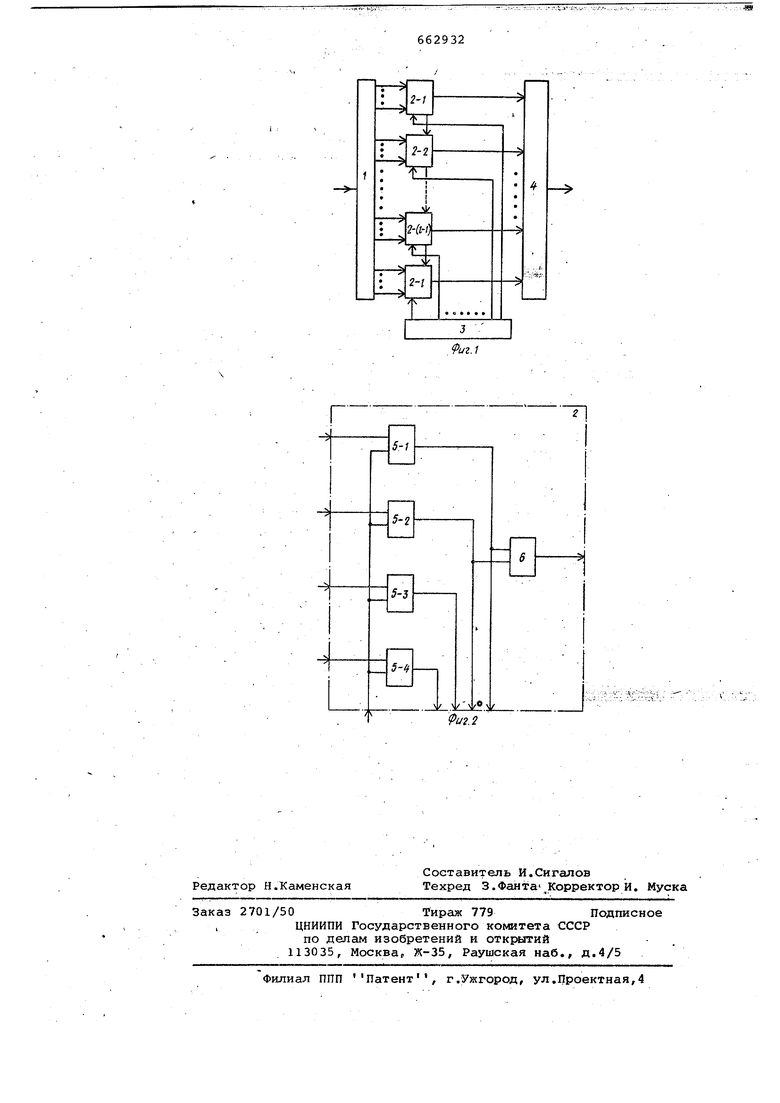

1 .. , Изобретение относится к вычислительной технике и может быть использовано для преобразованияр-кодов Фибоначчи в, двоичный код. Известны устройства для преобраэо вания кода с любым основанием в двои ный код, содержащие п-разрядный регистр, распределитель импульсов, двоичный сумматор, причем вход п-раз рядного регистра является входом пре образоватёля, а выход двоичного сумматора является выходом преобразователя 1 . Недостатком таких устройств является значительное время преобразования р-кода Фибоначчи в двоичный код. Целью изобретения является повыше ние быстродействия процесса преобра«рвания р-кодов Фибоначчи в двоичный код.; Это достигается тем, что преобразователь содержит I коммутаторов гру пы разрядов, причем первый информационный вьпсод каждого коммутатора группы разрядов соединен с соответствующим входом двоичного сумматора, второй информационный выход каждого коммутатора группы разрядов, кроме коммутатора младшей группы разрядов, соединен с (р+2)-ым входом соседнего коммутатора группы более младших разрядов, р+1 входы каждого коммутатора группы разрядов соединены с соответствующими единичными выходами п-разрядного регистра, управляющие входы каждого коммутатора группы разрядов соединены с боответствующими выходами распределителя импульсов. На фиг.1 показана функциональная схема устройства; на фиг.2 - функциональная схема коммутатора групп старших разрядов для и . Преобразователь содержит п-разрядный регистр 1, предназначенный для .хранения исходного р-кода Фибоначчи, Е коммутаторов группы разрядов 2-1-2-, предназначенных для формирования двоичных эквивалентов весов разрядов р-кода Фибоначчи, распределитель импульсов 3, предназначенный для управления процессом преобразования, двоичный сумматор 4, предназначенными для последовательного накопления .двоичных эквивалентов. На фиг.2 введены следующие обозначения: - элементы И, 6 элементы ИЛИ. Преобразователь работает следующим образом. 3 Перед началом преобразования исходный р-код Фибоначчи заносится в п-разрядный регистр 1, а триггеры двоичного сумматора 4 устанавливаются в нулевое состояние. По приходу первого тактового импульса на распределитель импульсов 3, на первом выходе последнего появляется единичный потенциал, который поступает-на управляющий вход коммутатора старшей группы разрядов. Если в п-разрядном регистре 1, в каком либо из подряд идущих, начиная со старших, разрядов записана е диница, то на выходе тех коммутаторов группы разрядов, номера кбторых совпадают с .номерами единичных разрядов в двоичном эквиваленте веса данно -о единичного разряда р-кода Фибоначчи, появится единичный сигнал. При этом необходимо подчеркйуть, что в группе из р подряд идущих разрядов р-кода Фибоначчи может находиться только одна единица, что вытекает из определения нормального р-кода Фибоначчи. В дво,ичномсумматоре 4 происходит сложение полученHord дйог чнОго эквивалента с содержанием сумматора. По приходу второго тайтрйогр импульса на BTopbwt выходе | аспределителя импульсов 3 пdявляetcя единичный потенциал, который .hocfynaeT на коммутатор следующей группы разрядов Если в n-paзpяjEitнoм регистре 1, в ка ком либо из ел едуюйщх р подряд идущих 1разрядо в, Написана единица, то на двоичном cyNMaTope 4 аналогичным образом происходит сложение двоичного эквив.алента веса данного : единичного разряда р-кода Фйбоначчи с содержимым сумматора. На Дйойчнбм cyMjiiaTdpe 4 таким образом накапливается сумма . , , в Операция суммирования даеичных эквивалентов веСов ёдйничнЕох разрядЪв Фибоначчи продолжается .до тех пор, пока не произойдет опро всех коммутаторов групп разрядов. При этом максимальное Количество тактов, необходимых для преобразова ния, будет равноЗ яакс ® число коммутаторов группы разрядов t определАется из неравенства (п) По окончании процесса преобразования в двоичном сумматоре 4 будет находиться двоичный эквивалент числа, записанного в р-коде 1ч1боначчи. I, Первые входы элементов И 5 1-5 4 соединены с выходами разрядов, ве 2 са которых равны соответственно 26, 19 , 14 и 10. Вторые входы каждого элемента И 5 1-5-4 соединены с управляющим входом коммутатора групп разрядов. Выход элемента ИЛИ 6 соединен со входом того разряда двоичного сумматора 4, вес которого равен 14. Выходы каждого элемента И 5-1-5-4 являются входными для следующего коммутатора группы разрядов и соединены с соответствующими входами элемента ИЛИ 6 следующего коммутатора группы раэрядов и также являются входными для последующих коммутаторов группы разрядов . i . Необходимо отметить, что коммутаторы группы младших разрядов могут, в зависимости от длины преобразуемого р-кода Фибоначчи, содержать или искомое число элементов И ,и элемент ИЛИ, или только один элемент ИЛИ. Формула изобретения Преобразователь р-кода Фибоначчи в двоичный код, содержащий п-разряднь1й регистр, распределитель импульсов двоичный сумматор, причем вход п-разрядного регистра является вхог дом преобразователя, выход двоичного сумматора является выходом преобразователя, отличающийся тем, что, с цеЛью повышения быстродействия, преобразователь содержит J коммутаторов группы разрядов, причем первый информационный выход каждого коммутатора группы разрядов соединен с соответствующим входом двоичного сумматора, второй инфор-. мацйонНый выход каждого коммутатора группы разрядов/ кроме коммутатора младшей группы разрядов, соединен с (р+2) входом соседнего коммутатора группы более младдаих разрядов,(р+1) входы каждого, коммутатора группы разрядов соединены с йоответствуюпщми единичными выходами п-разрядного регистра, управляющие входы каждого коммутатора группы разрядов соединены с соответствующими выходами распределителя импульсов. . Источники информации, принятые во внимание при экспертизе 1. йвторское свидетельство СССР № 439801, кл. G 06 F 5/02, 1974.

| название | год | авторы | номер документа |

|---|---|---|---|

| "Преобразователь кода Фибоначчи в код "золотой" пропорции" | 1990 |

|

SU1783616A1 |

| Преобразователь кода Фибоначчи в двоичный код | 1986 |

|

SU1432789A1 |

| "Преобразователь кода Фибоначчи-1 в код "золотой"-1 пропорции" | 1988 |

|

SU1649671A1 |

| Преобразователь кодов | 1978 |

|

SU744548A1 |

| Преобразователь кодов | 1986 |

|

SU1438008A1 |

| Преобразователь кодов | 1988 |

|

SU1552380A1 |

| Преобразователь двоичного кода в позиционный код со смешанным основанием | 1980 |

|

SU960792A1 |

| Преобразователь прямого кода в обратный | 1982 |

|

SU1032448A1 |

| Преобразователь двоичного кода в код с постоянным весом | 1984 |

|

SU1229964A1 |

| Преобразователь двоичного кода в непозиционный код Фибоначчи | 1988 |

|

SU1767700A1 |

Авторы

Даты

1979-05-15—Публикация

1976-08-02—Подача