сл

со

00 О5

со ;о ;о

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля цифровых узлов | 1981 |

|

SU1013960A1 |

| Устройство для функционального контроля цифровых блоков | 1989 |

|

SU1656538A1 |

| Устройство для контроля логических блоков | 1988 |

|

SU1608672A1 |

| Формирователь тестов | 1985 |

|

SU1260963A1 |

| Устройство тестового контроля | 1989 |

|

SU1691842A1 |

| УСТРОЙСТВО ТЕСТОВОГО КОНТРОЛЯ | 2014 |

|

RU2565474C1 |

| Устройство для контроля блоков памяти | 1986 |

|

SU1444896A1 |

| Многоканальное устройство тестового контроля логических узлов | 1988 |

|

SU1564623A1 |

| Устройство для тестового контроля цифровых узлов | 1987 |

|

SU1425682A1 |

| Устройство для контроля дискретной аппаратуры с блочной структурой | 1987 |

|

SU1539783A1 |

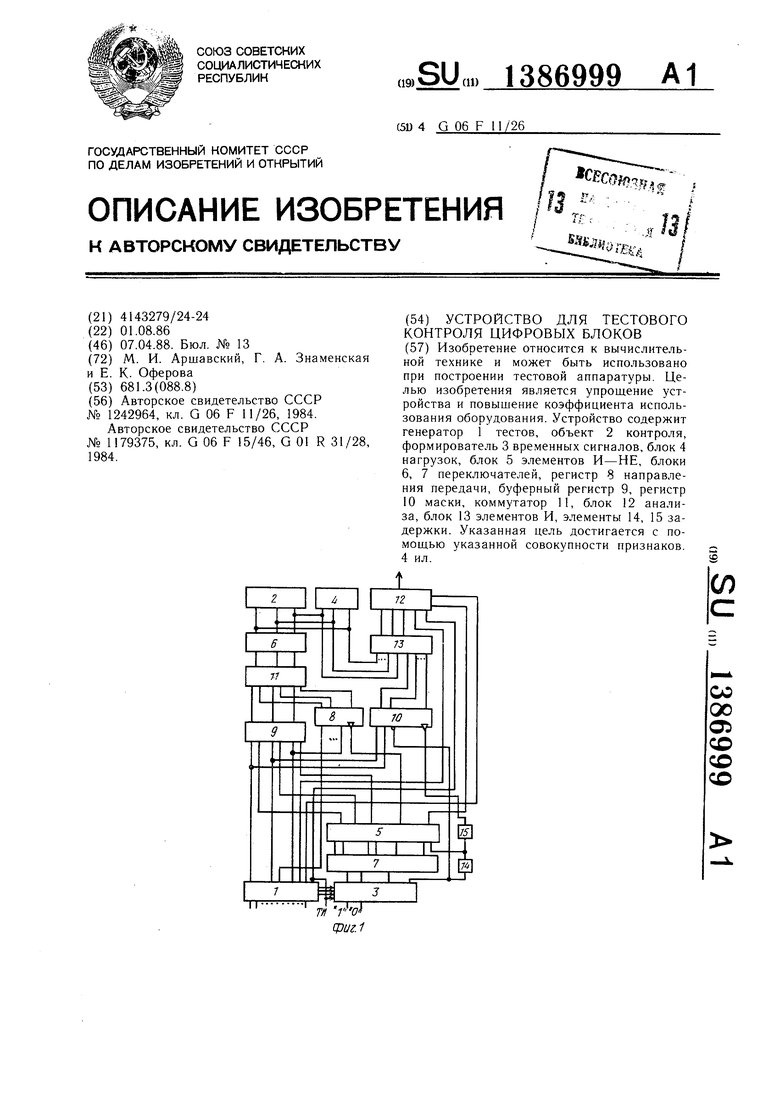

Изобретение относится к вычислительной технике и может быть использовано при построении тестовой аппаратуры. Целью изобретения является упрощение устройства и повышение коэффициента использования оборудования. Устройство содержит генератор 1 тестов, объект 2 контроля, формирователь 3 временных сигналов, блок 4 нагрузок, блок 5 элементов И-НЕ, блоки 6, 7 переключателей, регистр 8 направления передачи, буферный регистр 9, регистр IO маски, коммутатор 11, блок 12 анализа, блок 13 элементов И, элементы 14, 15 задержки. Указанная цель достигается с помощью указанной совокупности признаков. 4 ил. 1C

тн Фиг.1

Изобретение относится к цифровой вы- числительной технике и может быть использовано при ностроении тестовой апнаратуры. Целью изобретения является упрощение

устройства и повышение коэффициента использования оборудования.

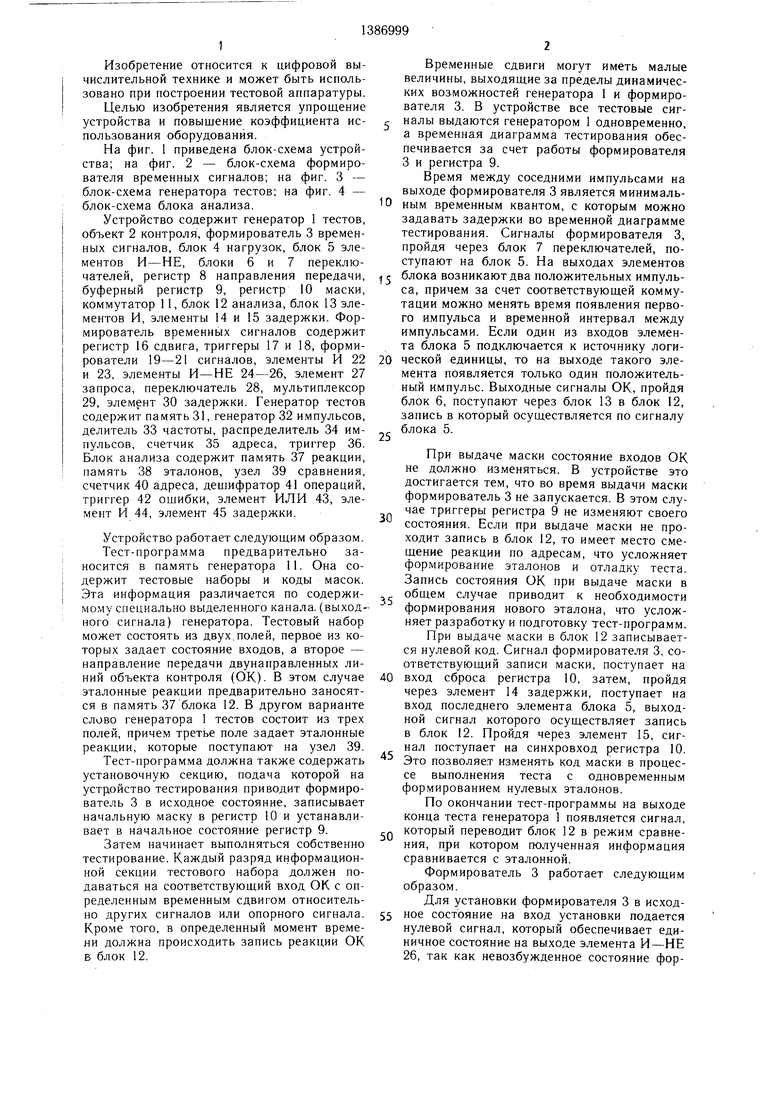

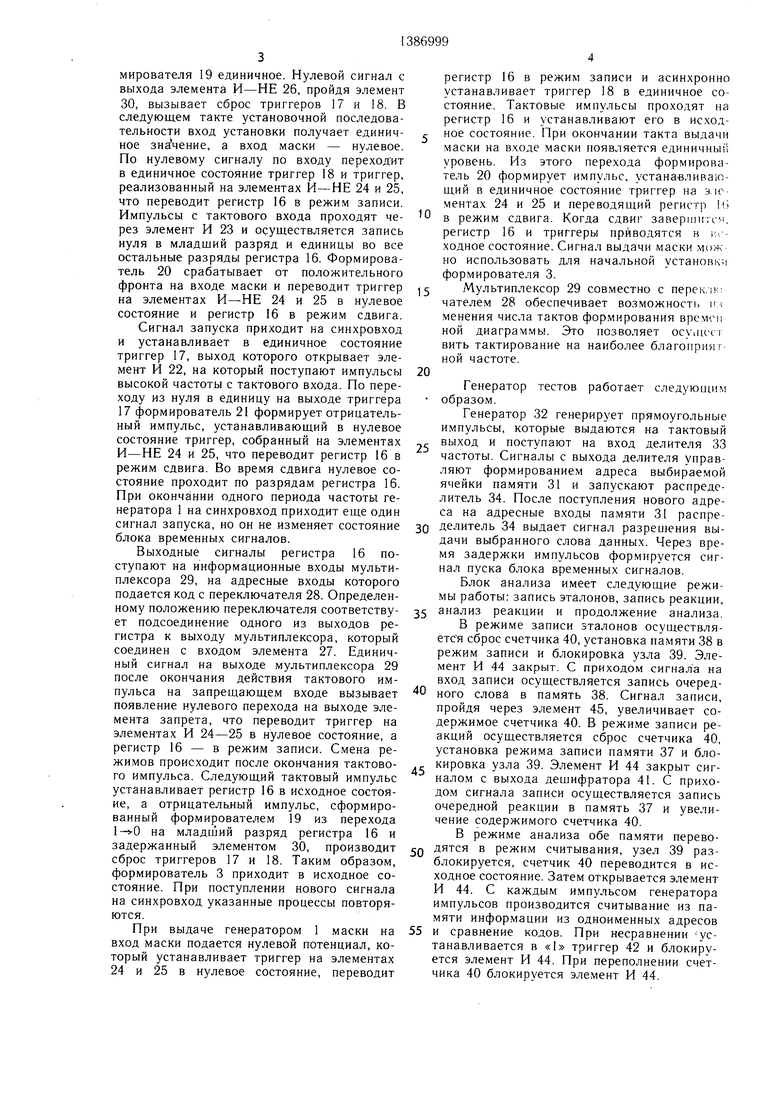

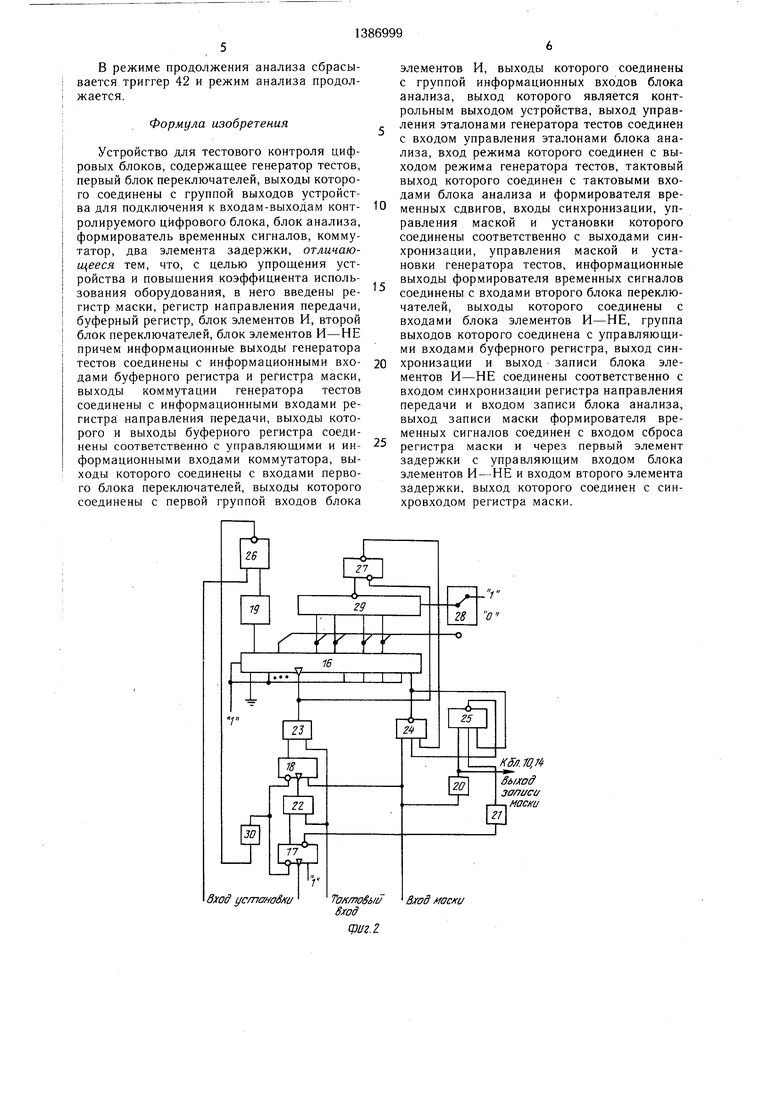

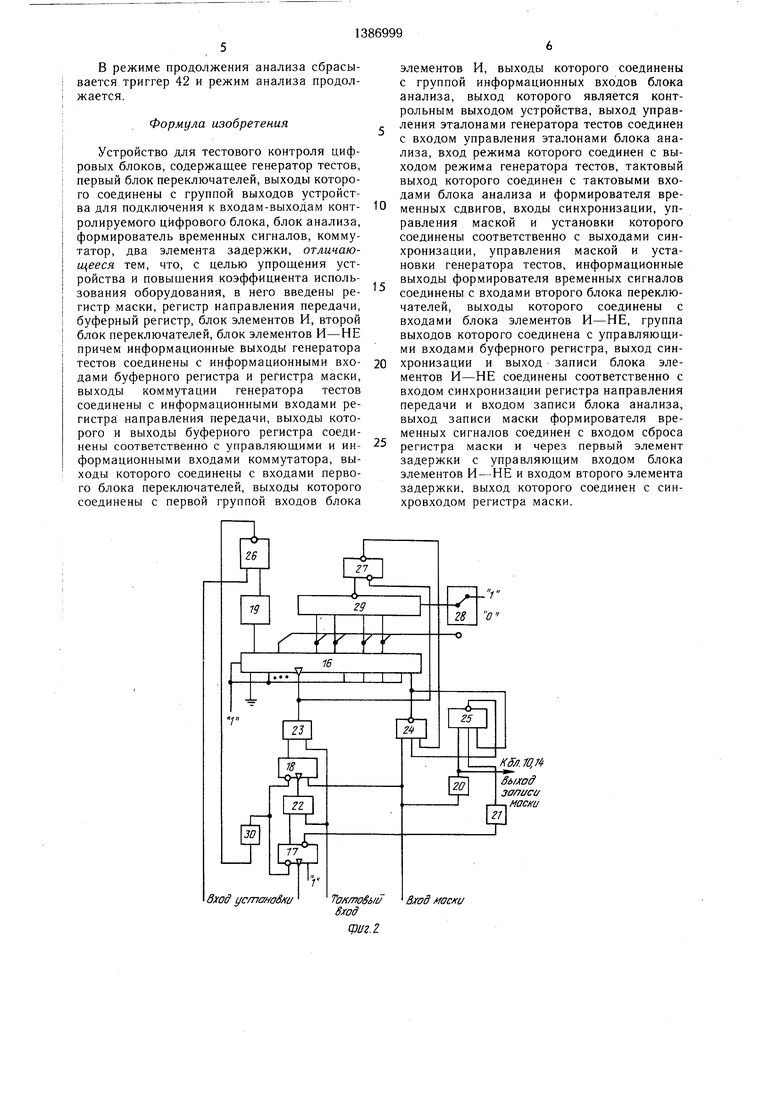

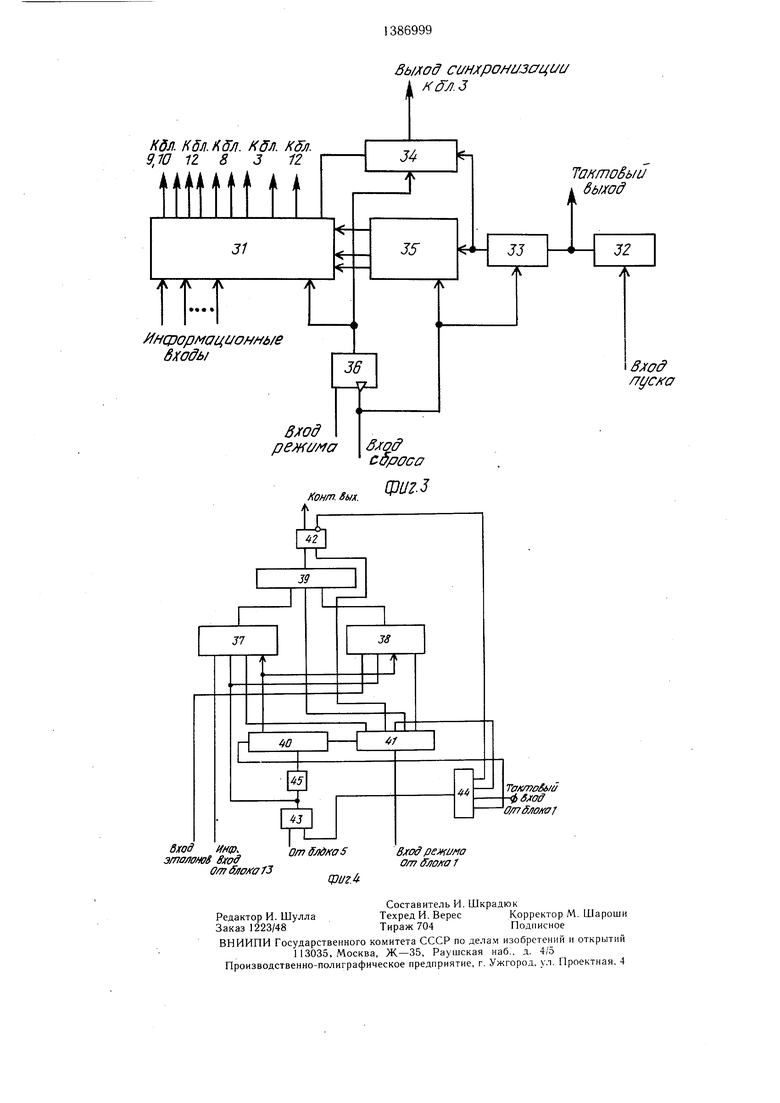

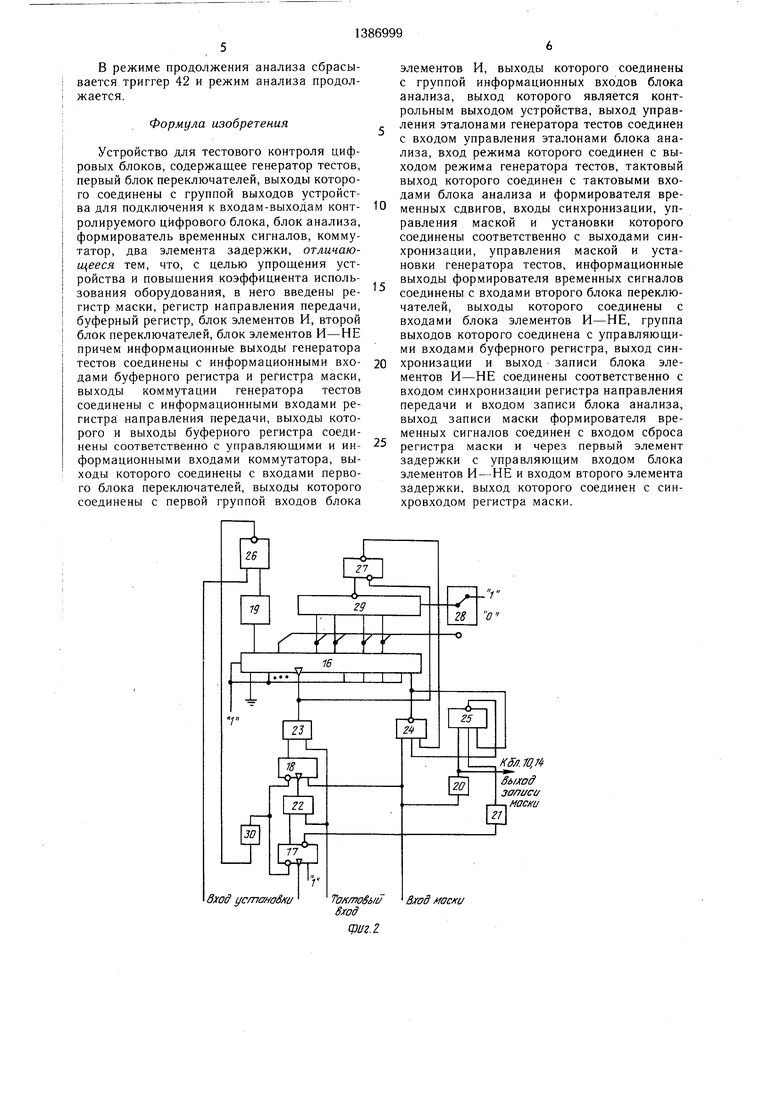

На фиг. 1 приведена блок-схема устройства; на фиг. 2 - блок-схема формирователя временных сигналов; на фиг. 3 - блок-схема генератора тестов; на фиг. 4 - блок-схема блока анализа.

Устройство содержит генератор 1 тестов, объект 2 контроля, формирователь 3 временных сигналов, блок 4 нагрузок, блок 5 элементов И-НЕ, блоки 6 и 7 переключателей, регистр 8 направления передачи, буферный регистр 9, регистр 10 маски, коммутатор 11, блок 12 анализа, блок 13 элементов И, элементы 14 и 15 задержки. Формирователь временных сигналов содержит регистр 16 сдвига, триггеры 17 и 18, формирователи 19-21 сигналов, элементы И 22 и 23, элементы 24-26, элемент 27 запроса, переключатель 28, мультиплексор 29, элемент 30 задержки. Генератор тестов содержит память 31, генератор 32 импульсов, делитель 33 частоты, распределитель 34 импульсов, счетчик 35 адреса, триггер 36. Блок анализа содержит память 37 реакции, память 38 эталонов, узел 39 сравнения, счетчик 40 адреса, дешифратор 41 операций, триггер 42 ошибки, элемент ИЛИ 43, элемент И 44, элемент 45 задержки.

Устройство работает следующим образом.

Тест-программа предварительно заносится в память генератора 11. Она содержит тестовые наборы и коды масок. Эта информация различается по содержимому специально выделенного канала, (выходного сигнала) генератора. Тестовый набор может состоять из двух.полей, первое из которых задает состояние входов, а второе - направление передачи двунаправленных линий объекта контроля (ОК). В этом случае эталонные реакции предварительно заносятся в память 37 блока 12. В другом варианте слово генератора 1 тестов состоит из трех полей, причем третье поле задает эталонные реакции, которые поступают на узел 39.

Тест-программа должна также содержать установочную секцию, подача которой на устройство тестирования приводит формирователь 3 в исходное состояние, записывает начальную маску в регистр 10 и устанавливает в начальное состояние регистр 9.

Затем начинает выполняться собственно тестирование. Каждый разряд информационной секции тестового набора должен подаваться на соответствующий вход ОК с определенным временным сдвигом относительно других сигналов или опорного сигнала. Кроме того, в определенный момент времени должна происходить запись реакции ОК Б блок 12.

Временные сдвиги могут иметь малые величины, выходящие за пределы динамических возможностей генератора I и формирователя 3. В устройстве все тестовые сигналы выдаются генератором 1 одновременно, а временная диаграмма тестирования обеспечивается за счет работы формирователя 3 и регистра 9.

Время между соседними импульсами на выходе формирователя 3 является минималь0 ным временным квантом, с которым можно задавать задержки во временной диаграмме тестирования. Сигналы формирователя 3, пройдя через блок 7 переключателей, поступают на блок 5. На выходах элементов

блока возникают два положительных импульса, причем за счет соответствующей коммутации можно менять время появления первого импульса и временной интервал между импульсами. Если один из входов элемента блока 5 подключается к источнику логи0 ческой единицы, то на выходе такого элемента появляется только один положительный импульс. Выходные сигналы ОК, пройдя блок 6, поступают через блок 13 в блок 12, запись в который осуществляется по сигналу блока 5.

При выдаче маски состояние входов ОК не должно изменяться. В устройстве это достигается тем, что во время выдачи маски формирователь 3 не запускается. В этом слу- чае триггеры регистра 9 не изменяют своего состояния. Если при выдаче маски не проходит запись в блок 12, то имеет место смещение реакции по адресам, что усложняет формирование эталонов и отладку теста. Запись состояния ОК при выдаче маски в общем случае приводит к необходимости формирования нового эталона, что усложняет разработку и подготовку тест-программ.

При выдаче маски в блок 12 записывается нулевой код. Сигнал формирователя 3, соответствующий записи маски, поступает на 0 вход сброса регистра 10, затем, пройдя через элемент 14 задержки, поступает на вход последнего элемента блока 5, выходной сигнал которого осуществляет запись в блок 12. Пройдя через элемент 15, сигнал поступает на синхровход регистра 10. Это позволяет изменять код маски в процессе выполнения теста с одновременным формированием нулевых эталонов.

По окончании тест-программы на выходе конца теста генератора 1 появляется сигнал, Q который переводит блок 12 в режим сравнения, при котором полученная информация сравнивается с эталонной.

Формирователь 3 работает следующим образом.

Для установки формирователя 3 в исход- 5 ное состояние на вход установки подается нулевой сигнал, который обеспечивает единичное состояние на выходе элемента И-НЕ 26, так как невозбужденное состояние формирователя 19 единичное. Нулевой сигнал с выхода элемента И-НЕ 26, пройдя элемент 30, вызывает сброс триггеров 17 и 18. В следующем такте установочной последовательности вход установки получает единичное зна чение, а вход маски - нулевое. По нулевому сигналу по входу переходит в единичное состояние триггер 18 и триггер, реализованный на элементах И-НЕ 24 и 25, что переводит регистр 16 в режим записи. Импульсы с тактового входа проходят через элемент И 23 и осуществляется запись нуля в младщий разряд и единицы во все остальные разряды регистра 16. Формирователь 20 срабатывает от положительного фронта на входе маски и переводит триггер на элементах И-НЕ 24 и 25 в нулевое состояние и регистр 16 в режим сдвига.

Сигнал запуска приходит на синхровход и устанавливает в единичное состояние триггер 17, выход которого открывает элемент И 22, на который поступают импульсы высокой частоты с тактового входа. По переходу из нуля в единицу на выходе триггера 17 формирователь 21 формирует отрицательный импульс, устанавливающий в нулевое состояние триггер, собранный на элементах И-НЕ 24 и 25, что переводит регистр 16 в режим сдвига. Во время сдвига нулевое состояние проходит по разрядам регистра 16. При окончании одного периода частоты генератора 1 на синхровход приходит еще один сигнал запуска, но он не изменяет состояние блока временных сигналов.

Выходные сигналы регистра 16 поступают на информационные входы мультиплексора 29, на адресные входы которого подается код с переключателя 28. Определенному положению переключателя соответствует подсоединение одного из выходов регистра к выходу мультиплексора, который соединен с входом элемента 27. Единичный сигнал на выходе мультиплексора 29 после окончания действия тактового импульса на запрещающем входе вызывает появление нулевого перехода на выходе элемента запрета, что переводит триггер на элементах И 24-25 в нулевое состояние, а регистр 16 - в режим записи. Смена режимов происходит после окончания тактового импульса. Следующий тактовый импульс устанавливает регистр 16 в исходное состоя- ие, а отрицательный импульс, сформированный формирователем 19 из перехода на младплий разряд регистра 16 и задержанный элементом 30, производит сброс триггеров 17 и 18. Таким образом, формирователь 3 приходит в исходное состояние. При поступлении нового сигнала на синхровход указанные процессы повторяются.

При выдаче генератором 1 маски на вход маски подается нулевой потенциал, который устанавливает триггер на элементах 24 и 25 в нулевое состояние, переводит

регистр 16 в режим записи и асинхронно устанавливает триггер 18 в единичное состояние. Тактовые импульсы проходят на регистр 16 и устанавливают его в исходс- ное состояние. При окончании такта выдачи маски на входе маски появляется единичный уровень. Из этого перехода формирователь 20 формирует импульс, устанавливающий в единичное состояние триггер на э.ю ментах 24 и 25 и переводящий регистр (

0 в режим сдвига. Когда сдвиг завершится, регистр 16 и триггеры приводятся в исходное состояние. Сигнал выдачи маски мож но использовать для начальной установки формирователя 3.

5 Мультиплексор 29 совместно с перек,-|к; чателем 28 обеспечивает возможность и i менения числа тактов формирования времен ной диаграммы. Это позволяет ocyiHcn вить тактирование на наиболее благоприят ной частоте.

0

Генератор тестов работает следуюииш образом.

Генератор 32 генерирует прямоугольные импульсы, которые выдаются на тактовый г выход и поступают на вход делителя 33 частоты. Сигналы с выхода делителя управляют формированием адреса выбираемой ячейки памяти 31 и запускают распределитель 34. После поступления нового адреса на адресные входы памяти 31 распре0 делитель 34 выдает сигнал разрещения выдачи выбранного слова данных. Через время задержки импульсов формируется сигнал пуска блока временных сигналов.

Блок анализа имеет следующие режимы работы:запись эталонов, запись реакции,

5 анализ реакции и продолжение анализа. В режиме записи эталонов осуществляется сброс счетчика 40, установка памяти 38 в режим записи и блокировка узла 39. Элемент И 44 закрыт. С приходом сигнала на вход записи осуществляется запись очеред0 ного слова в память 38. Сигнал записи, пройдя через элемент 45, увеличивает содержимое счетчика 40. В режиме записи реакций осуществляется сброс счетчика 40, установка режима записи памяти 37 и блокировка узла 39. Элемент И 44 закрыт сигналом с выхода дещифратора 41. С приходом сигнала записи осуществляется запись очередной реакции в память 37 и увеличение содержимого счетчика 40.

В режиме анализа обе памяти перевод дятся в режим считывания, узел 39 разблокируется, счетчик 40 переводится в исходное состояние. Затем открывается элемент И 44. С каждым импульсом генератора импульсов производится считывание из памяти информации из одноименных адресов

5 и сравнение кодов. При несравнении -устанавливается в «1 триггер 42 и блокируется элемент И 44. При переполнении счетчика 40 блокируется элемент И 44.

В режиме продолжения анализа сбрасывается триггер 42 и режим анализа продолжается.

Формула изобретения

Устройство для тестового контроля цифровых блоков, содержащее генератор тестов, первый блок переключателей, выходы которого соединены с группой выходов устройства для подключения к входам-выходам контролируемого цифрового блока, блок анализа, формирователь временных сигналов, коммутатор, два элемента задержки, отличающееся тем, что, с целью упрощения устройства и повышения коэффициента использования оборудования, в него введены регистр маски, регистр направления передачи, буферный регистр, блок элементов И, второй блок переключателей, блок элементов И-НЕ причем информационные выходы генератора тестов соединены с информационными входами буферного регистра и регистра маски, выходы коммутации генератора тестов соединены с информационными входами регистра направления передачи, выходы которого и выходы буферного регистра соединены соответственно с управляющими и информационными входами коммутатора, выходы которого соединены с входами первого блока переключателей, выходы которого соединены с первой группой входов блока

8ход ycfnoHoSm

Тактоё&ш мает

вход (uz.l

0

0

5

элементов И, выходы которого соединены с группой информационных входов блока анализа, выход которого является контрольным выходом устройства, выход управления эталонами генератора тестов соединен с входом управления эталонами блока анализа, вход режима которого соединен с выходом режима генератора тестов, тактовый выход которого соединен с тактовыми входами блока анализа и формирователя временных сдвигов, входы синхронизации, управления маской и установки которого соединены соответственно с выходами синхронизации, управления маской и установки генератора тестов, информационные выходы формирователя временных сигналов соединены с входами второго блока переключателей, выходы которого соединены с входами блока элементов И-НЕ, группа выходов которого соединена с управляющими входами буферного регистра, выход синхронизации и выход записи блока элементов И-НЕ соединены соответственно с входом синхронизации регистра направления передачи и входом записи блока анализа, выход записи маски формирователя временных сигналов соединен с входом сброса регистра маски и через первый элемент задержки с управляющим входом блока элементов И-НЕ и входом второго элемента задержки, выход которого соединен с син- хровходом регистра маски.

/(л ЩГ

записи

маски

КбЛ к5л. К5л. КбЛ. . 9,10 11 8 3 12

31

н

Информационные входы

реж1// а Зло

сбро CPU

Конт. Sbix.

Вход fffiip, эгла/юноВ 8mff

0/rfS/io aJ3

Вь/АОд Ci/Hj(pOHL/.3aL4L/U

r.j

ТантоВыи выход

пдс/са

ло

сброса CPU2.3

TaxmoSu/a

O/nffM/faj

Вход pe ffUMO о/л ffJio a 1

| Устройство для контроля синхронных цифровых узлов | 1984 |

|

SU1242964A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для контроля больших интегральных схем памяти | 1984 |

|

SU1179375A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1988-04-07—Публикация

1986-08-01—Подача