ход конца микропрограммы которого соединен с первым входом третьего элемента ИЛИ, второй вход которого соединен с входом окончания выполнения микропрограммы устройства, выходы элементов И первой группы соединены с информационными входами регистра кода операций, выходы которого соединены с первой группой входов формирователя адреса, вторая по К-ю группы входов которого соединены соответственно с выход ми счетчиков группы, выходы формирователя адреса соединены с входами лервого элемента ИЛИ и с первыми входами элементов И первой группы, вторые входы которых соединены с прямым выходом триггера, вход передачи управления устройства соединен со счетными входами счетчиков групп

2. Устройство по П.1, отличающееся, тем, что блок модификации адреса содержит группу элементов И и группу сумматоров по модулю два, причем вторая группа

входов, блока соединена с перЗйми входами элементов И группы, вторые входы которых соединены с первой группой входов блока, а выходы соединены с первыми входами суматоров по модулю два группы, выхода которых соединены с выхода-ми блока, а вторые входы сумматоров ПОмодулю два группы соединены с первой группой входов блока, первая группа, входов блока соединена с выходами блока.

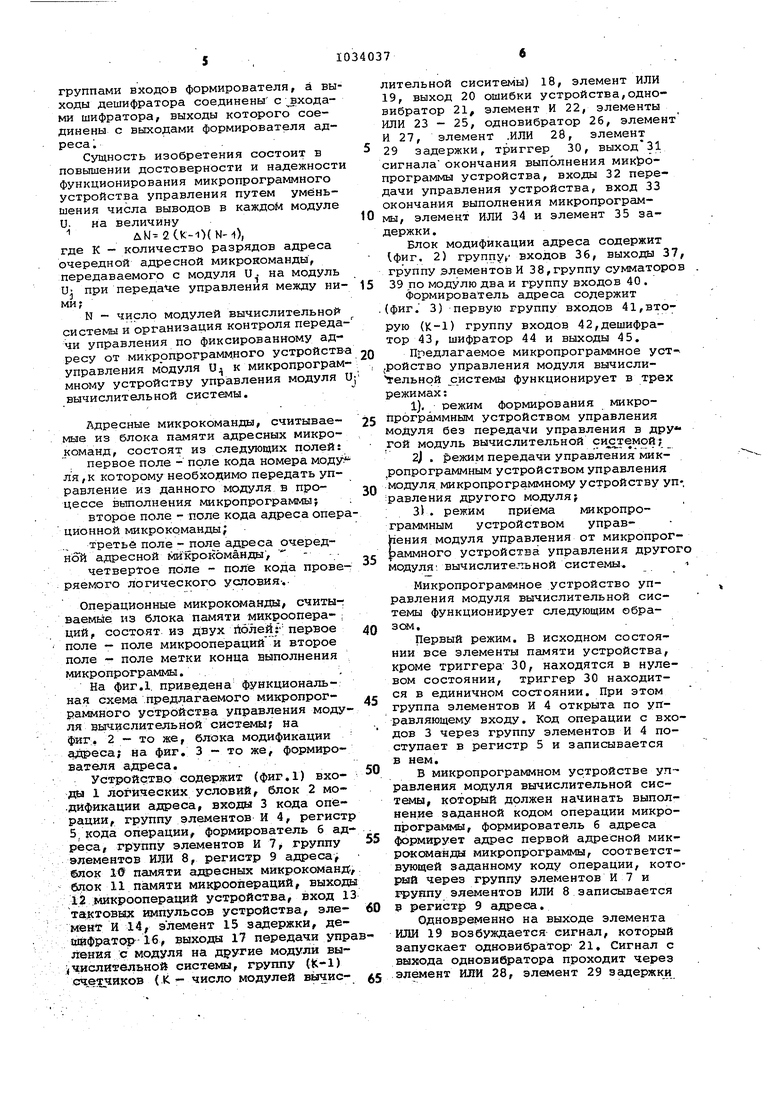

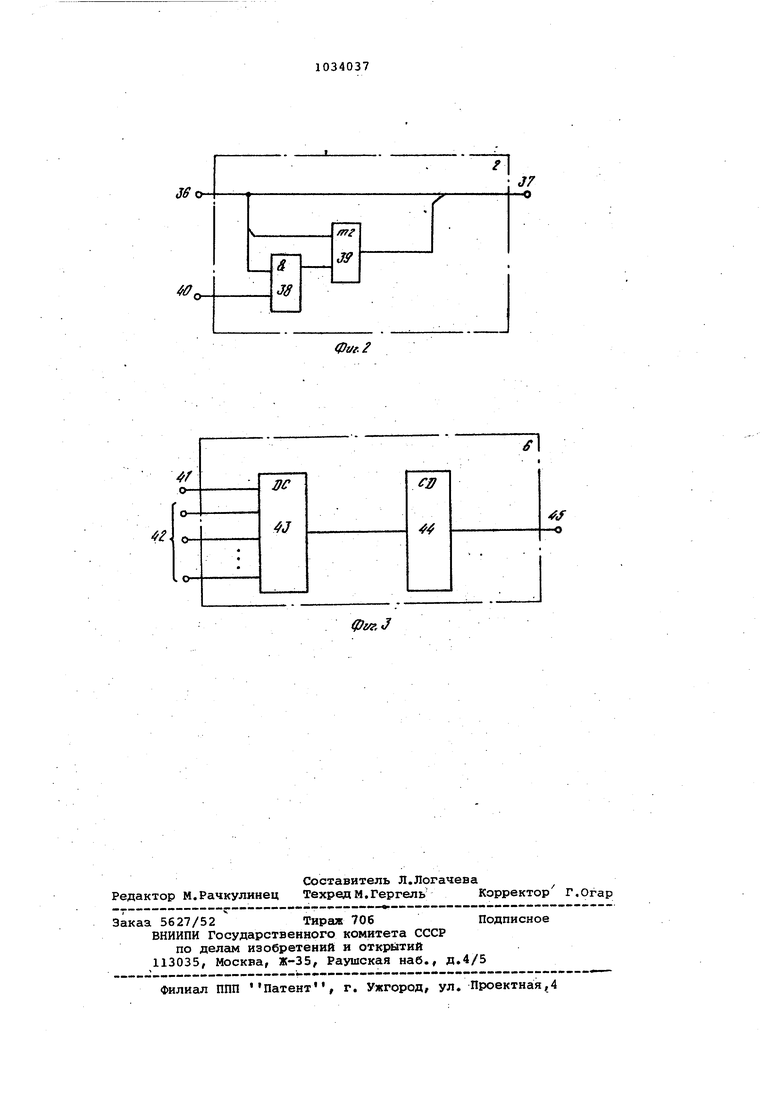

3. Устройство по П.1, о т л ичающееся тем, что формирователь содержит дешифратор и шифратор, причем первая группа входов дешифратора соединена с первой группой входов формирователя, входал второй по К-ю - групп входов дешифратора соединены соответственно с второй ,по .К-ю :j. группами входов формирователя, а вьлходы дешифратора соединены с входами шифратора, выходы которого соединены с выходами формирователя адреса.

| название | год | авторы | номер документа |

|---|---|---|---|

| Микропрограммное устройство управления | 1982 |

|

SU1030801A1 |

| Микропрограммное устройство управления с контролем | 1983 |

|

SU1142832A1 |

| Микропрограммное устройство управления | 1981 |

|

SU968814A1 |

| Управляющая векторная вычислительная система | 1982 |

|

SU1120340A1 |

| Перестраиваемый микропрограммный процессор | 1981 |

|

SU983713A1 |

| Микропрограммное устройство управления | 1983 |

|

SU1115054A1 |

| Микропрограммное устройство управления | 1982 |

|

SU1059573A1 |

| Микропрограммное устройство управления | 1982 |

|

SU1020824A1 |

| Устройство для управления восстановлением микропрограмм при сбоях | 1982 |

|

SU1056193A1 |

| Микропрограммное устройство управления | 1983 |

|

SU1124299A1 |

1.МИКРОПРОГРАММНОЕ УСТРОЙ.СТВО УПРАВЛЕНИЯ МОДУЛЯ ВЬЗЧИСЛИТЕЛЬНОЙ СИСТЕМЫ, содержащее регистр кода операции, регистр адреса, блок памяти адресных микрокоманд, блок памяти микроопераций, блок модификации адреса, дешифратор, первый элемент И, первую и вторую группу элементов И, первый и второй элементы ИЛИ, группу элементов ИЛИ, причем выход поля адреса очередной микрокоманды соединен с первыми входами элементов ИЛИ группы, выходы которых соединены с входами регистра адреса, выходы которого соединены с первой группой входов блока модификации адреса, вторая группа входов которого соединена с входом логических условий устройства, а выходы - с адресными входами блока памятиадресных микрокоманд, выходы поля адреса микроопераций которого соединены с адресными входами блока .памяти микроопераций, а выходы поля номера модуля - с входами дешифрато.ра, выход которого подключен к управляющему входу устройства, группа выходов блока памяти микроопераций ;соединена с выходами микроопераций устройства, выход первого элемента ИЛИ.соединен с первым входом первого элемента И, группа входов передачи управления устройства соединена с входами второго элемента ИЛИ, отличающееся тем. .что, с целью повышения достоверности функционирования, оно дополнительно содержит четыре элемента ИЛИ,два элемента И, два одновибратора,три элемента задержки, формирователь адреса, триггер и группу (К-1) счетчиков (К. - число модулей вычислительной системы), причем входы кода операций устройства соединены с пер выми входами элементов И первой группы, вторые входы которых соединены через первый элемент задержки с выходом третьего элемента ИЛИ,с вы ходом окончания выполнения микро;программы, с входами сброса счет- . чиков группы и регистра кода операций и с первым входом четвертого элемента ИЛИ, второй вход которого (Л соединен с выходом ошибки устройства. и с выходом второго элемента И,ин-. i версный вход которого соединен с выходом первого элемента ИЛИ и через первый одновибратор с первым вхо;дом пятого элемента ИЛИ, второй вход которого соединен с выходом первого элемента И,второй вход которого соединен с другим входом второго CAD (Элемента И и через второй одновибратор с выходом второго элемён- 4 та ИЛИ, выход пятого элемента ИЛИ о через второй элемент задержки сое-, динен с нулевым входом триггера, ..; СО единичный вход которого соединен с выходом четвертого элемента ИЛИ, третий вход которого соединен с выходом шестого элемента ИЛИ,входы которого соединены с выходом поля номера модуля, инверсный выход триггера соединен с первым входом третьего элемента И, второй вход которого соединен с входом тактовых импульсов устройства, а выход - с управляющим входом блока памяти ад ресных микрокоманд и через третий элемент задержки с управляющим входом блока памяти микроопераций, вы

изобретение относится к автомати ке и вычислительной технике и может быть использовано при проектировани вычислительных и управляющих систем, построенных на унифицированных модулях, выполненных в виде БИС..

Известно микропрограммное устройство управления, содержащее блоки памяти микроопераций и адресных микрокоманд, а также счетчик 1у1икрокоманд; 1 .

Однако данное устройство характеризуется низкой ги6кос ь ю управления, обусловленной отсутствием возможности передачи управления с микропрограммного устройства управления одного модуля вычислительной системы на микропрограммное устройство управления другого модуля, Йизкой универсальностьк и низкой степенью унификации, вызванных невозможностью наращивания объема и количества микропрограмм.

Наиболее близким к предлагаемом по технической сущности и достигаемому эффекту является микропрограммное устройство управления, содержа щее регистр, кода операции, регистр адреса, блок модификации адреса, блок памяти адресных микрокоманд, блок, памяти микроопераций, дешифратор, первый и второй элементы .И, первую и вторую группы элементов

И, первый элемент задержки и группу элементов .ИЛИ. .

Структура вычислительной системы (ВС), в состав которой входит это 5 микропрограммное устройство управления, состоит из нескольких идентичных микропрограммных модулей,-каждый из которых может самостоятельно выполнять большинство функций по

0,обработке информации.

Б каждый отдельно взятый момент времени обработки информации работает только один модуль вычислительной системы. После выполнения всех

.Существенными недостатками известного микропрограммного устройства управления модулей указанной вычислительной системы являются малое значение параметра функционального

5 разбиения БИС, на которых выполня ются.микропрограммные устройства управления модулей ВС (параметр функционального разбиения;БИС - это отношение числа элементов в крисQ талле к количеству выводов из него) / низкая достоверность-функционирова,ния системы, обусловленная отсутстви-v &л контроля правильности передачи управления с одного модуля на другой

модуль вычислительной системы, а iтакже большое число внешних связей между модулями, выполненными в виде БИС, обусловленное необходимостью передачи адреса очередной,адресной шкpoкoмaнды с микропрограммного усройства управления модуля на микропрограммное устройство управления другого модуля,

Цель Изобретения - повышение достоверности функционирования микропрограммного устройства управления модуля ВС при выполнении микропрограмм большого объема.

Поставленная цель достигается тем, что в микропрограммное устройство управления модуля вычислительной системы, содержащее регистр кода операции регистр адреса, блок памяти адресных микрокоманд, блок памяти микроопераций, блок модификации адреса, дешифратор, первый и второй элементы ИЛИ, первую и втору группы элементов И, группу элементов ИЛИ, первый элемент И, причем выход поля адреса очередной микрокоманды соединен с первыми входами элементов ИЛИ группы, выходы которы соединены с входами регистра адреса вйходы которого соединены с первой группой входов блока модификации адреса, вторая .группа входов которого соединена с входом логических условий устройства, а выходы - с адресными входами блока памяти адресных микрокоманд, выходы поля адреса микроопераций которого соединены с адресными входами блока памяти микроопераций, а выходы поля номера модуля - с входами дешифратора, выход которого подключен к управляющему входу устройства, группа выходов блока памяти микроопераций соединена с выходами микроопераций устройства, выход первого элемента ИЛИ соединен с первым входом первого элемента И, группа входов передачи управления устройства соединена с входами второго элемента ИЛИ , . дополнительно введены четыре элемента ИЛИ, два элемета И, два одновибратора, три элемен та задержки, формирователь адреса, триггер и группу (К-1) счетчиков (К.- число модулей вычислительной системы),, причем входы кода операций устройства соединены с первыми входами элементов И первой группы, вторые .входы кото:рых соединены чере первый элемент задержки с выходом третьего элемента ИЛИ, с.выходом окончания выполнения микропрограмки, с входами сброса счетчиков группы и регистра кода операций и с первьзм входом четвертого элемента ИЛИ, второй вход которого соединен с выходом ошибки устройства и с выходом второго элемента И, инверсный вход которого соединен с выходом первого элемента ИЛИ и через первый одновибратор с первым входом пятого элемента ИЛИ, второй вход которого соединен с выходом 5 первого элемента И, второй вход которого соединен с другим входом второго элемента И и через второй одновибратор с выходом второго элемента ИЛИ, выход пятого элемента ИЛИ

0 через второй элемент задержки соединен с нулевым входом триггера,единичный вход которого соединен с выходом четвертого элемента ИЛИ, третий вход которого соединен с выходом

5 шестого элемента ИЛИ, входы которого соединены с выходомполя номера модуля,-инверсный выход триггера . соединен с первым входом третьего элемента И, второй вход котороQ го соединен с входом тактовых импульсов устройства, а выход - С управляющим входом блока памяти адресных микрокоманд и через третий элемент задержки с управляющим входом блока памяти микроопераций,выход конца микропрограммы которого г . соединен с первым входом третьего элемента ИЛИ, второй вход которого соединен с входом окончания выполнения микропрограммы устройства, выходы элементов И первой группы соединены с информационными входами р.егистра кода операций, выходы кото-, рого соединены с первой группой входов формирователя адреса, вторая по

5 к-ю группы которого соединены соответственно с выходами счетчиков группы, выходы формирователя адреса соединены с входами первого элемента ИЛИ и с первыми входами элементов

0 И первой группы, вторые входы которых соединены с прямым выходом триггера, вход передачи управления устройства соединен со счетными входами счетчиков группы.

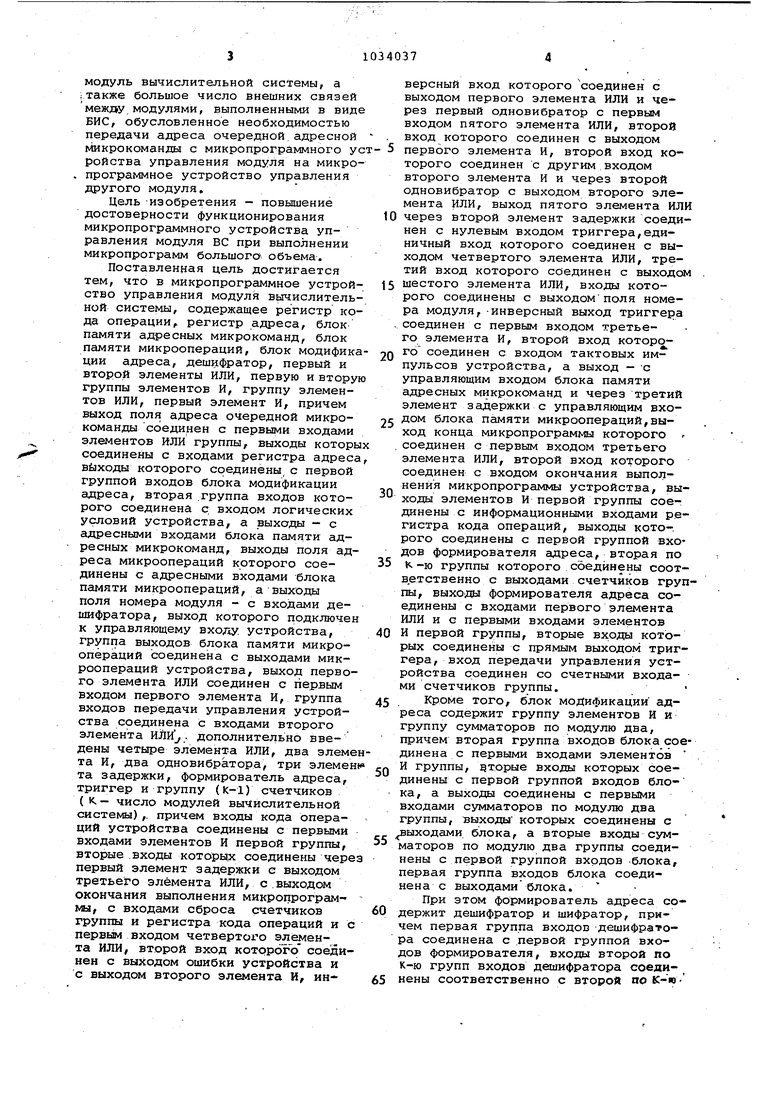

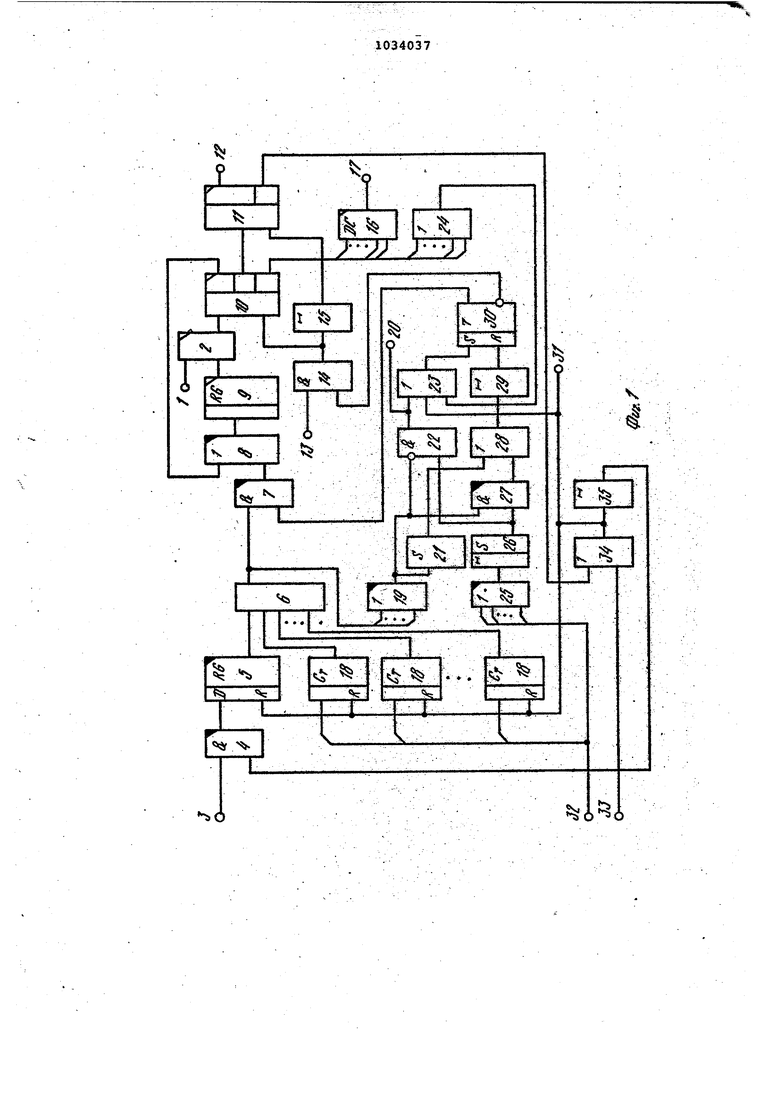

5 Кроме того, блок модификации адреса содержит группу элементов И и группу сумматоров по модулю два, причем вторая группа входов блока соединена с первыми входами элементов И группы, вторые входы которых соединены с первой группой входов блока, а выходы соединены с первыми входами сумматоров по модулю два группы, ВЫХОДЫ которых соединены с выходами блока, а вторые входы сумматоров по модулю два группы соединены с первой группой входов -блока, первая группа входов блока соединена с выходами блока.

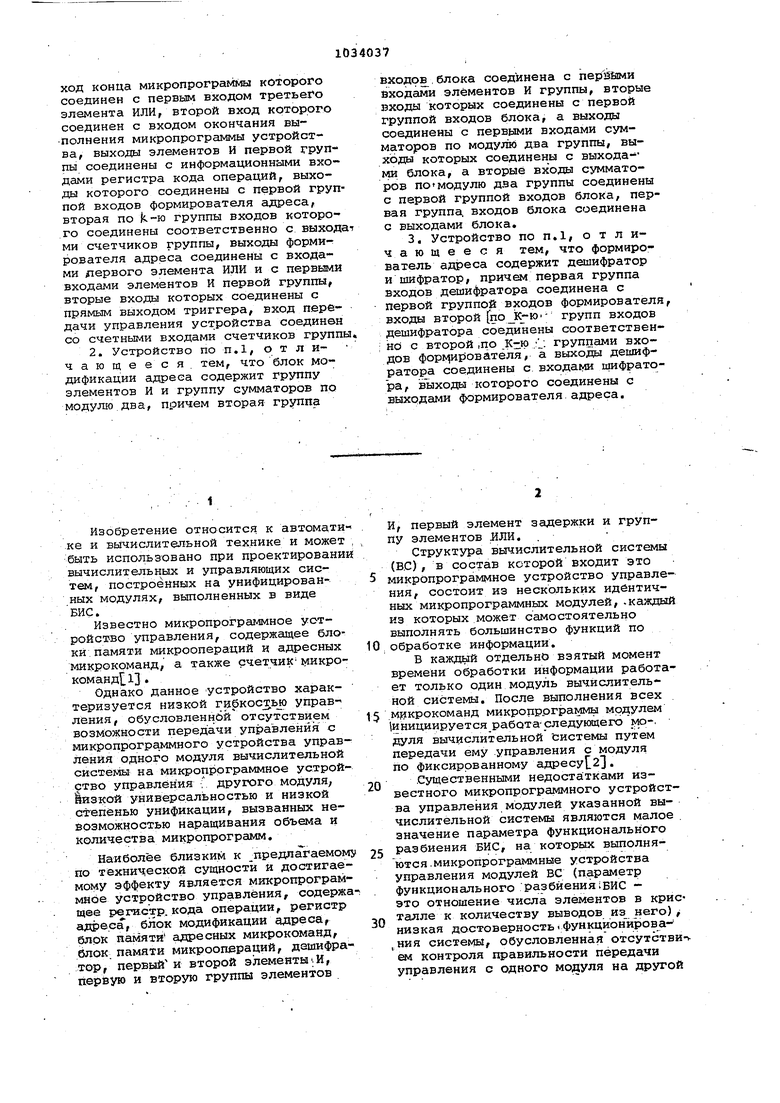

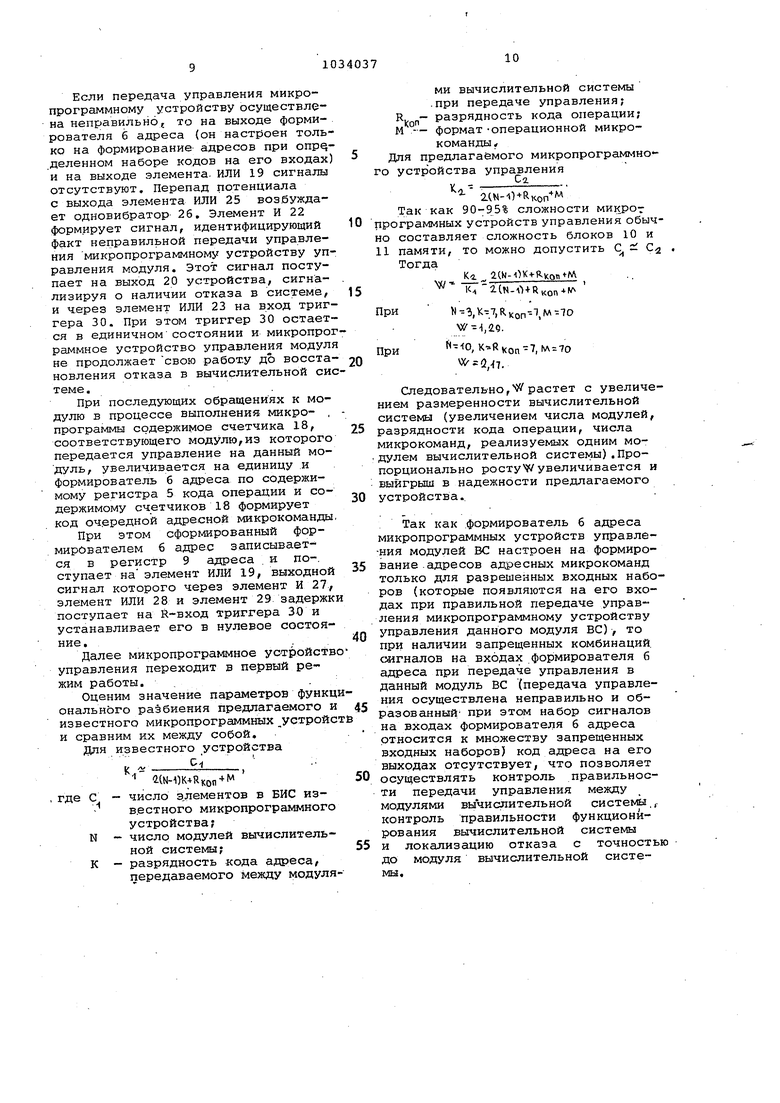

При этом формирователь адреса содержит дешифратор и шифратор, причем первая группа входов дешифратора соединена с .первой группой входов формирователя, входы второй по к-ю групп входов дешифратора соединены соответственно с второй по К-югруппами входов формирователя, а вы ходы дешифратора соединены с Jвxoдaми шифратора, выходы которого соединены с выходами формирователя адресатСущность изобретения состоит в повышении достоверности и надежност функционирования микропрограммного устройства управления путем уменьшения числа выводов в каждом модуле и. на величину лЫ-2С1с-1(Ы1), где К - количество разрядов адреса очередной адресной микрокоманды, передаваемого с модуля U на модуль и при передаче управления между ни ми N - число модулей вычислительной системы и организация контроля переда чи управления по фиксированному адресу от микропрограммного устройств управления модуля Uз к микропрограм мному устройству управления модуля вычислительной системы. Адресные микрокоманды, считываемне из блока памяти адресных микрокоманд, состоят из следующих полей: первое поле - поле кода номера модУ ля,к которому необходимо передать управление из данного модуля в процессе выполнения микропрограммы; второе поле - поле кода адреса опер ционной микрокоманды; третье поле - поле адреса очереднШ адресной микрокоманды, - - четвертое поле - поле кода прове ряемого логического условия-.Операционные микроксманды, считыг ваемые из блока памяти микроопера- ; ций, состоят из двух йолей/ первое поле - поле микрооперадий и второе поле - поле метки конца выполнения микропрограммы. На фиг.1. приведена функциональная схема предлагаемого микропрограммного устройства управления моду ля вычислительной системы; на фиг, 2 - то же, блока модификации адреса; на фиг. 3 - то же, формирователя адреса. . Устройство содержит (фиг.1) входы 1 логических условий, блок 2 мо.дйфикации адреса, входы 3 кода операции, группу элементов И 4, регист 5/кода операции, формирователь б ад реса, группу элементов И 7, группу элементов ИЛИ 8, регистр 9 адреса ©лок W памяти адресных микрокоманд блок 11 па.мяти микроопераций, выход 12 микроопераций устройства, вход 1 та.ктовыз адлпульсов устройства, элемент И 14, элемент 15 задержки, деадафратор -16, выходы 17 передачи упр ления :с модуля на модули вы числительной системы, группу (Х-1) счетчиков (К- число модулей вычислительной сиситемы) 18, элемент ИЛИ 19, выход 20 ошибки устройства,одновибратор 21, элемент И 22, элементы ИЛИ 23 - 25, одновибратор 26, элемент И 27, элемент .ИЛИ 2Й, элемент 29 задержки, триггер 30, выход31 сигнала окончания выполнения мик зопрограммы устройства, входы 32 передачи управления устройства, вход 33 окончания выполнения микропрограммы, элемент ИЛИ 34 и элемент 35 задержки . Блок модификации адреса содержит 1ФИГ. 2) группу входов 36, выходы 37, группу элементов И 38,группу сумматоров 39 по модулю два и группу входов 40 . Формирователь адреса содержит (фиг. 3) первую группу входов 41,вторую (К-1) группу входов 42,дешифратор 43, шифратор 44 и выходы 45. Предлагаемое микропрограммное уст .ройство управления модуля вычислительной с истемы функционирует в трех режимах: 1. режим формирования микропрограммным устройством управления модуля без передачи управления в дру гой модуль вычислительной системой; 2j . режим передачи управления микропрограммным устройством управления модуля микропрограммному устройству уп:равления другого модуля; 3). режим приема микропрограммным устройством управИения модуля управления от микропрограммного устройства управления другого модуля; вычислительной системы. Микропрограммное устройство управления модуля вычислительной системы функционирует следующим образал, Первый режим. В исходном состоянии все элементы памяти устройства, кроме триггера 30, находятся в нулевом состоянии, триггер 30 находится в единичном состоянии. При этом группа элементов И 4 открыта по управляющему входу. Код операции с входов 3 через группу элементов И 4 поступает в регистр 5 и записывается в нем. В микропрограммном устройстве управления модуля вычислительной системы, который должен начинать выполнение заданной кодом операции микропрограммы, формирователь 6 адреса формирует адрес первой адресной микрокоманды микропрограммы, соответствующей заданному коду операции, который через группу элементов И 7 и группу элементов ИЛИ 8 записывается 5 регистр 9 адреса. Одновременно на выходе элемента ИЛИ 19 возбуждается сигнал, который запускает одновибратор 21. Сигнал с выхода одновибратора проходит через .элемент ИЛИ 28, элемент 29 задержки

и поступает на вход триггера 30.При этом триггер 30 переходит в нулевое состояние. Группа элементов и 7 эа крывается, а элемент И 14 открывается. Очередной тактовый импульс с входа 13 устройства через элемент И 14 поступает на элемент i5 задержки и на управляющий вход блока 10 памяти. При этом из блока 10 памяти по адресу, поступающему ,на его адресный вход с блока 2 модификации адреса, считывается адресная микрокоманда/ Сигналы с группы выходов блока Ю памяти поступают на дешифратор 16 и элемент ИЛИ 24 (эти сигналы отличны от нуля только при считывании микрокоманды передачи управления).

Сигналы с второй группы выходов поступают на адресные входы блока 11 памяти. Сигналы с третьей группы выходов поступают через группу элементов ИЛИ 8 в регистр 9.

Тактовый импульс, задержанный элементом 15 задержки на время, равное времени обращения к блоку JO памяти, поступает на управляющий вход блока 11 памяти. При этом с блока 11 памяти по адресу, поступающему с второ группы выходов блока 10 памяти, считывается операционная микрокоманда и поступает на выходы, 12 MHKpcfoneраций устройства. При поступлении очередного тактового импульса на вход 13 устройства по адресу очередр ной с1дресной мийрокома нды, хранящемуся в регистре 9 адреса и модифицируемому в блоке 2 модификации адреса логическими условиями, поступающими на группу входов 1 устройства, считывается очередная адресная и операционная макрокоманда по указанному алгоритму.Далее устройство фукк. ционирует аналогично. .

При работе микропрограммного устройства управления модуля в первом . ; режиме работы в первом по- ле считываемьах адресных Микрокоманд записывается нулевой код. Поэтому дешифратор 16 и элемент ИЛИ 24 в этом режиме работы не участвуют

. , При считывании последней операционной команды микропрограммы на выходе блока 11 памяти появляется сигнал окончания ее выполнения. Этот сигнал через элемент ИЛИ 34 поступает на выход 31 устройства, входы счетчиков 18 и регистра 5 кода операции, и устанавливает их в нулевое состояние. Сигнал с выхода элемента ИЛИ 34 при этом также поступает на элемент 35 задержки и через элемент ИЛИ 23 на вход триггера. 30 и устанавливает его в единичное состояние. При этом сигнал на втором входе элоиента |И 14 исчезает, а на управляющем вхоДе группы элементов И 7 появляется,

Сигнал, задержанный элементом 35 задержки на время,равное максимальному времени обнуления счетчиков

регистра 5 и изменения состояния трйггера 30, поступает йа управляющий вход группы элементов И 4.

Очерёдной код операций с группы входов 3 поступает в регистр 5 кода операции. Далее устройство функционирует аналогично указанному алгоритму..

Второй режим функционирования.- , При считывании адресной микрокоманду из блока 10 памяти -содержимое первого поля через первую группу .выходов поступает на дешифратор 16 и элемент ИЛИ 24. При этом на выходе дешифратора, соответствукяцем модулю (к которому необходимо передать управление из данного модуля) появляется сигнал н поступает на соответствующий выход 17 устройства.

Сигнал с выхода элемента ИЛИ 24 (с группы выходов блока 10 считывается ненулевой код) поступает через элемент ИЛИ 23 на входы триггера 30 и устанавливает его в единичное состояние. При Э.ТОМ тактовьге импульсы через И 14 не проходят к микропрограммное устройство управления модуля прекращает фоЕялирование микроопераций..

Третий режим функционирования. Сигнал с К-го. выхода группы выходов 1 микропрогра1 ного устройства управления модуля поступает, на группы входов 32 микропрограммного устройства управления модуля. При этом содержимое соответствующего модулю счетчика 18 увеличивается на единицу {сигнал поступает на его счетный вход). Если переход к. моДулю произведен правильно, то .по со-, держимому счетчиков.18 и по коду операции с выходов регистра 5 кода операции формирователь 6 адреса формирует адрес очередной-адресной микрокоманда выполненной микррпрограм;мы, который через группу элементов И 7 и группу элементов ИЛИ 8 поступает в .рег.стр 9 адреса.

Одновременно код адреса (ненулевой .с выхода формирователя б адреса поступает на элемент ИЛИ 19. Сигнгш с выхода элемента ИЛИ 19 возбуждает одновибратор 21, выходной сигнсШ

которого поступает через элемент ИЛИ 28 и элемент 29 задержки на вход триггера 30 и устанавливает его в нулевое состояние. При этом тактовые импульсы с входа 13 устройства поступают через элемент И 14 на.управляющий вход блока 10 памяти и на элемент 15 задержки. Далее микропрограммное устройства уп авления модуля функционирует аналогично функционированию в первом режиме работы. Если передача управления микропрограммному устройству осуществлена нeпpaвильн6 то на выходе формирователя 6 адреса (он настроен толь ко на формирование адресов при опр .деленном наборе кодов на его входах и на выходе элемента. ИЛИ 19 сигналы отсутствуют. Перепад потенциала с выхода элемента ИЛИ 25 возбуждает одновибратор 26. Элемент И 22 формирует сигнал, идентифицирующий факт неправильной передачи управления микропрограммному устройству уп равления модуля. Этот сигнал поступает на выход 20 устройства, сигнализируя о наличии отказа в системе, и через элемент ИЛИ 23 на вход триг гера 30, При этом триггер 30 остает ся в единичномсостоянии и микропрог раммное устройство управления модул не продолжает свою работу до восста новления отказа в вычислительной си теме. При последующих обращениях к модулю в процессе выполнения микро- , программы содержимое счетчика 18, соответствующего модулю,из которого передается управление на данный модуль, увеличивается на единицу .и формирователь б адреса по содержимому регистра 5 кода операции и содержимому счетчиков 18 формирует код очередной адресной микрокоманды При этом сформированный формирователем б адрес записывается в регистр 9 адреса . и по-, ступает на элемент ИЛИ 19, выходной сигнал которого через элемент И 27, элемент ИЛИ 28 и элемент 29 задержк поступает на R-вход триггера 30 и устанавливает его в нулевое состояние,, Далее микропрограммное устройств управления переходит в первый режим работы, ,. Оценим значение параметров функц онального разбиения предлагаемого и известного микропрограммных устройс и сравним их между собой, Для известного устройства S-i К.- - 2;(N-1)K+RKon где С - число э.лементов в БИС изв.естного микропрограммного устройства N - число модулей вычислительной системы; К - разрядность кода адреса, передаваемого между модулями вычислительной системы .при передаче управления RI - разрядность кода операции; М -- формат -операционной микрокомандыДля предлагаемого микропрограммного устройства управления V -. . KM-D+RKOP M Так как 90-95% сложности микрог программных устройств управления обычно составляет сложность блоков 10 и 11 памяти, то можно допустить С - C/j . JCi mjOK+RKoiHVA чЧ1у X /. k . - KI 2(N-AHR ,, W-1,20. -10, ,-7, гл 70 1,41. Следовательно,W растет с увеличением размеренности вычислительной системы (увеличением числа модулей, разрядности кода операции, числа микрокоманд, реализуемых одним модулем вычислительной системы),Пропорционально ростуWувеличивается и выигрыш в надежности предлагаемого устройства. Так как формирователь 6 адреса микропрограммных устройств управле-ния модулей ВС настроен на формирование -адресов адресных микрокоманд только для разрешенных входных наборов (которые появляются на его входах при правильной передаче управления микропрограммному устройству управления данного модуля ВС), то при наличии запрещенных комбинаций, сигналов на входах формирователя б адреса при передаче управления в данный модуль ВС (передача управления осуществлена неправильно и образованный при этом набор сигналов на входах формирователя б адреса относится к множеству запрещенных входных наборов) код адреса на его выходах отсутствует, что позволяет осуществлять контроль правильности передачи управления между модулями вычислительной системы,,, контроль правильности функционирования вычислительной системы и локализацию отказа с точностью до модуля вычислительной системы.

J O/77/ Jff

&

,

J8

J7

Фг/г,

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Микропрограммное устройство управления | 1976 |

|

SU596947A1 |

Авторы

Даты

1983-08-07—Публикация

1982-01-21—Подача