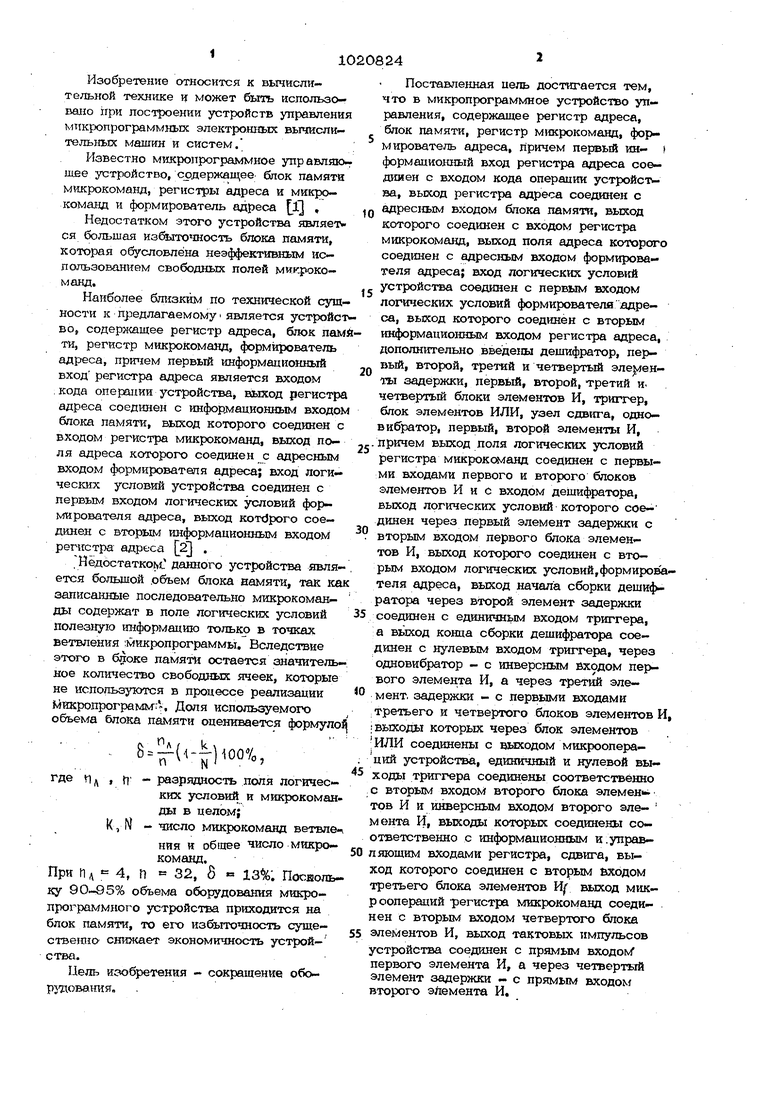

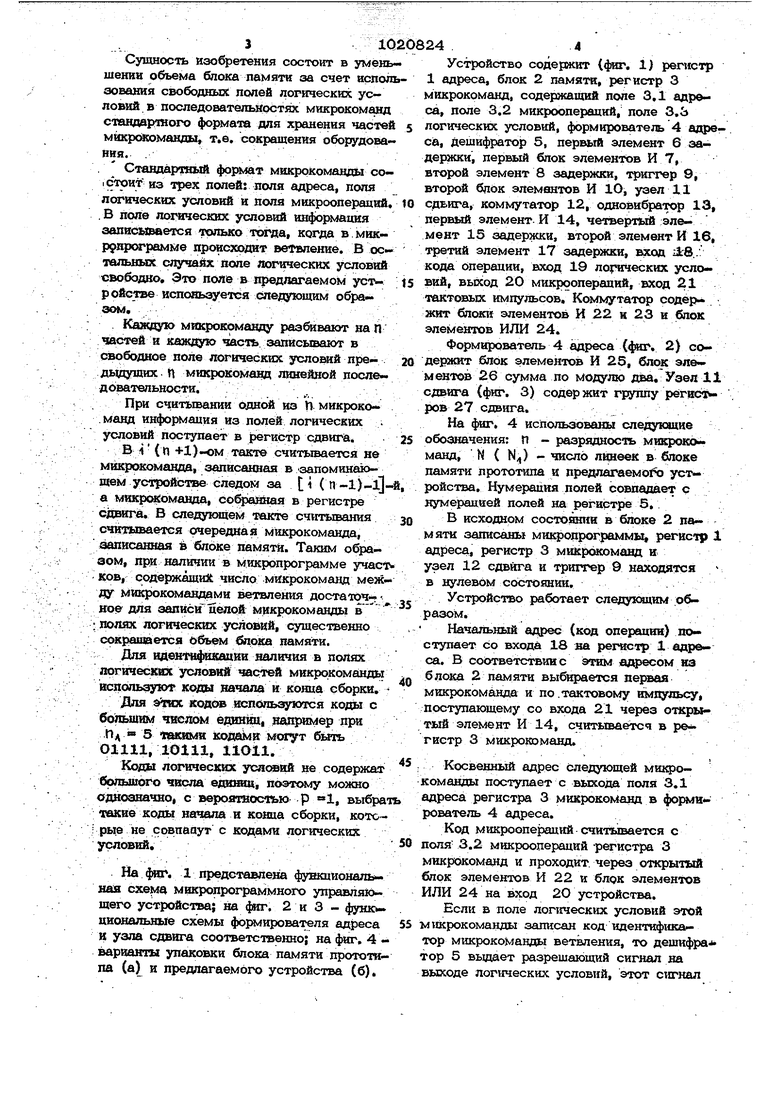

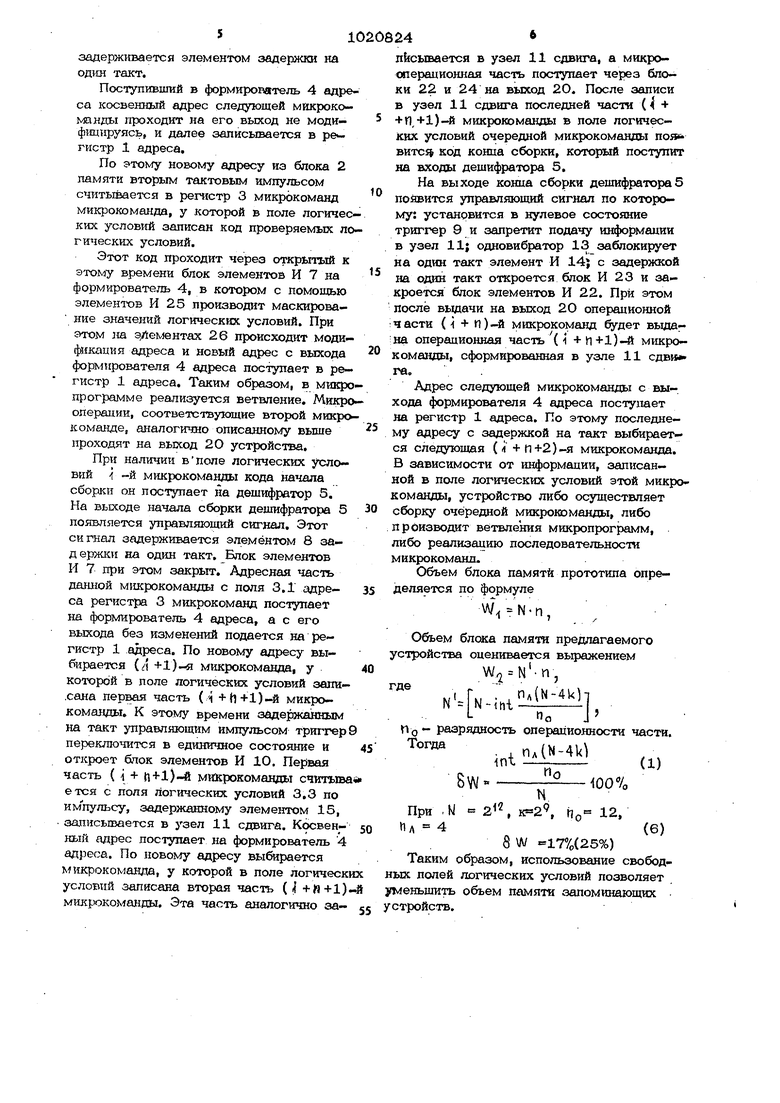

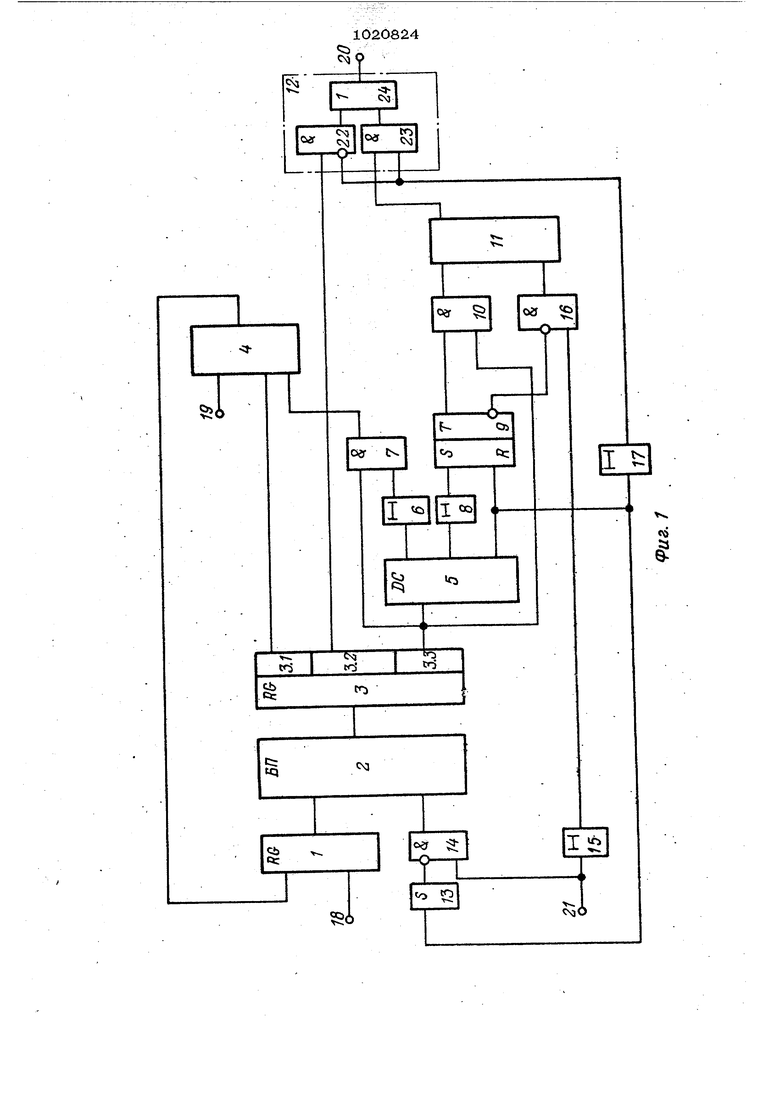

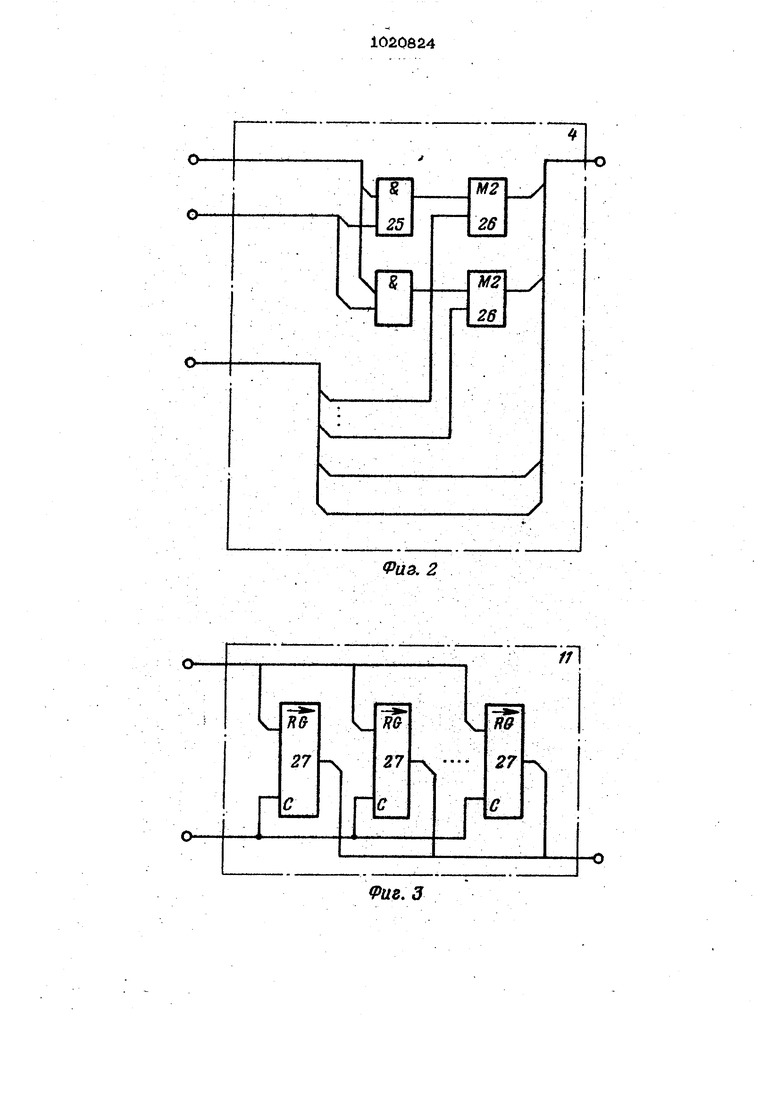

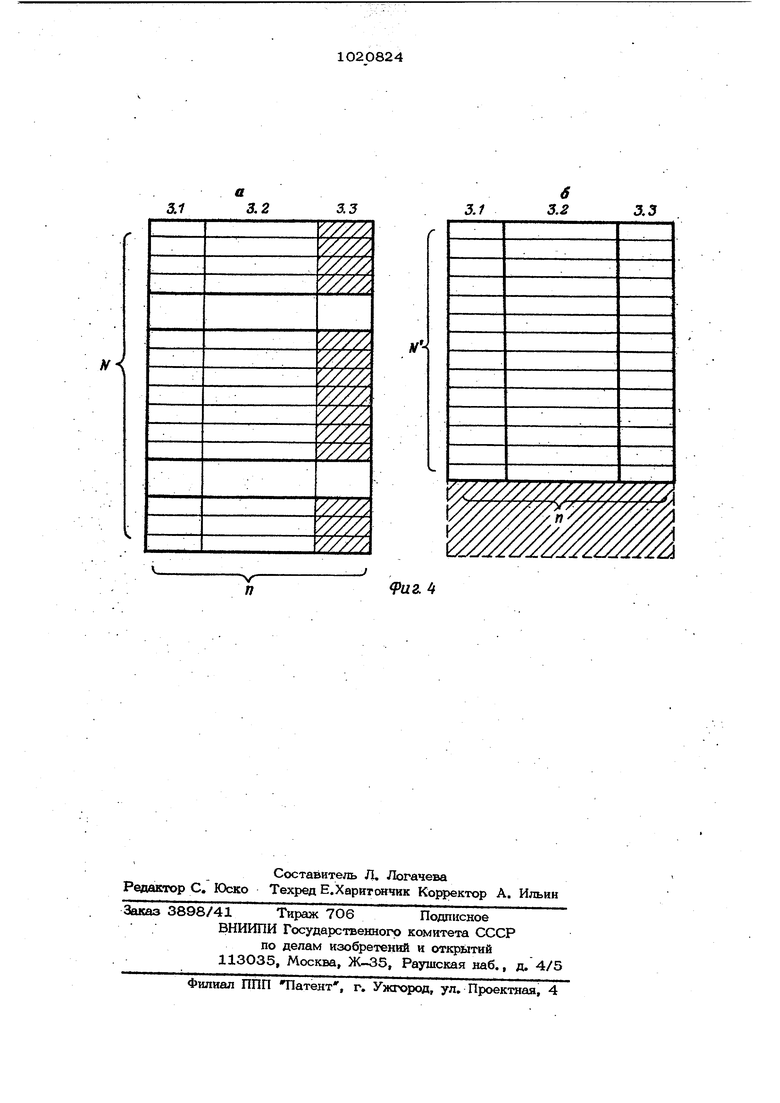

Изобретение относится к вычислительной технике и может быть использо- вшю при построении устройств управления микропрограммных электро-нных вычислите льных машин и систем. Известно микропрограммное управляю шее устройство, содержащее блок памяти микрокоманд, регистры адреса и микрюкоманд и формирователь адреса 1 , Недостатком этого устройства являет ся большая избыточность блока памяти, которая обусловлена неэффективным испольэованием свободных полей ми фокоманд. Наиболее близким по технической сушности к предлагаемому является устройст- во, содержащее регистр адреса, блок памйти, регистр микрокоманд, формирователь адреса, прш1ем первый информационный вход регистра адреса является входом .кода операции устройства, выход регистра адреса соединен с инфор }ационным входом блока памяти, выход которого соединен с входом регистра микрокоманд, выход поля адреса которого соединен с адресным входом формирователя адреса; вход логических условий устройства соединен с первым входом логических условий формирователя адреса, выход KOTdporo соединен с вторым информационным входом 9 регкстра адреса 2j . , Недостаткоьс данного устройства явля-, ется большой объем блока иамяти, так как эаписаияые последовательно микрокомадды содержат в поле логических условий35 полезную информацию только в точках ветвления микропрограммы. Вследствие этого в оке памяти остается значитель-: ное количество свободных ячеек, которые не использзтотся в процессе реализации 0 Ййкропрограммт-, Доля используемого объема блока памяти оценивается формуло1( . fr л/ 0 (1--- lOOVo J. где ti, ,JT - разрядность поля погических условий и микрокоман. ды в целом ., К, N - нисло микрокоманд ветвле. ния н общее число микрокоманд. п«,г и л h QO А ., 106/- При П д - 4, П « 32 6 « 13%. Посйольку 90-435% объема оборудования микропрограммного устройства приходится на блок памяти, то его избыточность суще-.. стеешш снижает экономичность устройства. Цель изобретения - сокращение обор -дования. . 45 Поставленная иель достигается тем, что в микропрограммное устройство уп- равления, содержащее регистр адреса, блок памяти, регистр микрокоманд, формирователь адреса, причем первый ин- формациокный вход регистра адреса соедниен с входом кода операции устройств ва, выход регистра адреса соединен с адресным входом блока памяти, выход которого соединен с входом регистра микрокоманд, выход поля адреса которого соединен с адресным входом формирователя адреса; вход логических условий устройства соединен с первым входом логических условий формирователеадреса, выход которого соединен с вторым информационным входом регистра адреса, дополнительно введены дещифратор, первый, второй, третий и четвертый эле енты задержки, первый, второй, третий и. четвертый блоки элементов И, триггер, блок элементов ИЛИ, узел сдвига, одновибратор, первый, второй элементы И, причем выход поля логических условий регистра микрокоманд соединен с первыми входами первого и второго блоков элементов И и с входом дешифратора, выход логических условий которого соединен через первый элемент задержки с вторым входом первого блока элементов И, выход которого соединен с вторым входом логических условий,формирователя адреса, выход начала сборки дешифратора через второй элемент задержки соединен с единичньхм входом триггера, а ВЬЕСОД конца сборки дешифратора соединен с нулевым входом триггера, через одновибратор - с инверсным входом первого элемента И, а через третий , задержки - с первыми входами третьего и четвертого блоков элементов И, ; выходы которых через блок элементов ИЛИ соединены с выходом микроопераций устройства, единичный и нулевой выходы триггера соединены соответственно элемен инверсным входом второго эле- мента И, выходы которых соединены сотгответственно с информационным и.управ„яющим входами регистра, сдвига, вы- f г t ОД которого соединен с вторым входом его блока элементов И( выход микроопераций регистра микрокоманд соеди- . вторым входом четвертого блока элементов И, выход тактовых импульсов устройства соединен с прямым входокГ первого элемента И, а через четвертый элемент задержки - с прямым вxoдo f второго элемента И. 31Q Сущность изобретения состоит в уменьшении объема блока памяти за счет ислоль аоваиия свободных полей логических условий в последователькост$к микрокоманд стандардаого формата для хранения частей мйкрокоманды, т.е. сокращения оборудоваСтандартньШ форшт микрокома нды со|Стрит из трех полей: поля адреса, поля логических условий и поля микроопераций. .В поле лог11 1ескюс условий информация записывается только -тогда, когда в.микР9Пр(Жрвмме происходит вефвление. В остальных случайх воле лсяшческих условий свободно. Это поле в предлагаемом yciv. ройстве используется следующим обра ЗОМ, - - . .. , / . Каждую мшсрокрманду разбивают на П частей и каждро часть, записывают в свободное поле логических услошй предьздуших П микрокоманд линейной последо)вательности. При считьгаании одной из П микроко.манд информация из полей логических . условий поступает в регистр сдвига. В i (п +1)-ом такте считывается не микрокоманда, записанная в запоминак .. шем усоройстве следом за ti ( П-1) микро|Соманда, со% а1П1ая в регистре сдвига, В следующем такте сч ггывания считывается очередная микрокоманда, зопЕИСанная fe блоке памяти. Таким образом, при наличии в микропрограмме участч ков, содержаши С число микрокоманд между микрокомандами ветвления достаточ- КО& для записицелой микрокоманды полях логических условий, существенно сокращается объем блока памяти. Для иден1114Я1Каиии наличия в полях логических условий частей микрокомандьг используют ксмш начала и Komia сборки. Для кодов {кгпбпьззгются коды с большим числом e nHiffl, надфимер при Пд 5 inai№MK ьтогут быть О1111, Iblll, 11О11. Ксд;|1 логических усжжвий не содержат бсавлюго числа едшжо, поэтому можно однозначно, с вероятнос«,ю р 1, выбрат овкие коды начала и ко1ша сборки, котс- i ръю не се)впааут с кодами логических условий. На фйГ. 1 представлена функциональная схема микропрограммного управляющего устройства; на фисг. 2 и 3 - фушоциональные схемы формирователя ад;реса И узла сдвига соответственно; на фиг. 4варианты упаковки блока памяти прототипа (а) и предлагаемого устройства (б). 244 Устройство соде{здсит (фиг, 1) регистр 1 адреса, блок 2 памяти, регистр 3 икрокоманд, содержащий поле 3.1 адреса, поле 3.2 микроопераций, поле 3,3 логических условий, формирователь 4 адреса, деши4фатор 5, первый элемент 6 эадержки, первый блок элементов И 7, второй элемент 8 задержки, триггер 9, второй бдок элементов И Ю, узел 11 сдвига, коммутатор 12, одновибра-гор 13, первый элемент. И 14, чет вертей элемент 15 задержки, второй элемент И 16, третий элемент 17 задерзкки, вход liS.. кода операции, вход 19 логических уелоВИЙ, вьЬсод 20 микроопераций, вход 21 тактовых импульсов. Коммутатор содержит 6noKtf элементов И 22 и 23 и блок элементов ИЛИ 24. Формирователь 4 адреса (фиг. 2) содержит блок элементов И 25, блок эле- ментоза 26 сумма по модулю два. Узел 11 сдвига (фиг. 3) содержит группу рег10кй ров 27 сдвига. На фиг. 4 использованы следукадие обозначения: П - разрядность микроко- манд, N ( N) -число лцнеек в блоке памяти прототипа и предлагаемо х устройства. Нумерация полей совпадает с нумерацией полей на регистре 5. В исходном состоянии в блоке 2 памяти записаны MmqponporpaMMb регистр 1 адреса, регистр 3 микрокоманд и узел 12 сдвига и триггер 9 находятся в нулевом соистоянии.Устройство работает следукяцим .о&разом. Начальный адрес (код операции) поступает со входа 18 на регистр 1 адреса. В соответствии с этам а цюсом из блока 2 памяти выбирается первая микрокоманда и по .тактовому всмпульсу, поступающему со входа 21 через открытый элемент И 14, считьюваетсч в регистр 3 микрокоманд. Косвенный адрес Следующей микрокоманды поступает с выхода поля 3.1 адреса регистра 3 микрокоманд в формирователь 4 адреса. Код микроопе|раций считывается с поля 3.2 микроопераций -регистра 3 микрокоманд и проходит, через открытый блок элементов И 22 и блок элементов ИЛИ 24 на вход 2О устройства. Если в поле логических условий этой микрокоманды записан код идентификатор микрокоманды ветвления, то дешифра тор 5 выдает разрешающий сигнал на выходе логических условий, этот сигнал задерживается элементом задержки на такт, Псх;тупивший в формирователь 4 адре са косвенный адрес следующей микрокоманды проходит на его выход не модифицируясь, и далее записывается в ре гистр 1 адреса. По этому новому адресу из блока 2 памяти вторым тактовым импульсом считывается в регистр 3 микрокоманд микрокоманда, у которой в поле логичес ких условий записан код проверяемых ло гических условий. Этот код проходит через открытый к этому времени блок элементов И 7 на формирователь 4, в котором с помощью элементов И 25 производит маскирова кие значений логических условий. При этом на э/1:ементах 26 происходит модификация адреса и новый адрес с выхода формирователя 4 адреса поступает в регистр 1 адреса. Таким образом, в микро программе реализуется ветвление. Микро операции, соответствующие второй микро комшаде, аналогично описанному выше проходят на выход 2 О устройства, При наличии вполе логических условий -( й микрокоманды кода начала сборки он поступает на дешифратор 5, На выходе начала сборки дешифратора 5 появляется управляющий сигнал. Этот сигнал задерживается элементом 8 зад ержки на один такт. Блок элементов И 7 при этом закрыт. Адресная часть дащюй микрокоманды с поля 3,1 адреса регистра 3 микрокоманд поступает на формирователь 4 адреса, а с его выхода без изменений подается на регистр 1 адреса. По новому адресу выбирается ( +1)-я микрокоманда, у которой в поле логических условий запи- .сана первая часть (-i +И+1)-й микрокоманды. К этому времени задержа)«ным на такт управляющим импульсом триггер переключится в единичное состояние и откроет блок элементов И 10. Первая часть ( i + ц+1)-й микрокоманды считыв ется с поля логических условий 3,3 по импульсу, задержанному элементом 15, записывается в узел 11 сдвига. Косвенный адрес поступает на формирователь 4 адреса. По новому адресу выбирается микрокоманда, у которой в поле логическ условий записана вторая часть (i( +й+1) мик{.)окоманды. Эта часть аналогично за124 пЬсьтается в узел 11 сдвига, а микрооперационная часть поступает через блоки 22 и 24 на выход 20, После записи в узел 11 сдвига последней части (4 + щ,+1)-й микрокоманды в поле логических условий очередной микрокоманды пода витс5| код конца сборки, который поступит на входы дешифратора 5, На выходе конца сборки дешифратора5 поразится управляющий сигнал по которому: установится в нулевое состояние триггер 9 и запретит подачу информации в узел 11; одновибратор 13 заблокирует на один такт элемент И 14J с задержкой на один такт откроется блок И 23 и закроется блок элементов И 22, При этом после вьщачи на выход 20 операционной части (i + П)-й микрокоманд будет выдаг на операционная часть (i +Ц+1)-41 микрокоманды, сформированная в узле 11 , Адрес следующей микрокоманды с выхода формирователя 4 адреса постухгает на регистр 1 адреса. По этому последнему адресу с задержкой на такт выбирается следующая ( + п+2)-я микрокоманда, В зависимости от информации, записанной в поле логических условий этой микрокоманды, устройство либо осуществляет сборку очередной микрокоманды, либо производит вб твления микропрограмм, либо реализацию последовательности микрокоманд. Объем блока памяти прототипа определяется по формуле .n,/ Объем блока памяти предлагаемого устройства оценивается вьфажением W,2 N -п, I Г,, 7 . nA( N-ini , LПоJ По - разрядность операционности части. Пл(Н-4И При .N 2 к«2, fio 12, Ил 4 8 W «17%(25%) Таким образом, использование свободных полей логических условий позволяет уг еньшить объем памяти запоминающих стройств.

Е

Ciff

Ю

СчЗ

| название | год | авторы | номер документа |

|---|---|---|---|

| Микропрограммное устройство управления | 1982 |

|

SU1151960A1 |

| Устройство микропрограммного управления | 1988 |

|

SU1667070A1 |

| Микропрограммное устройство управления | 1982 |

|

SU1030801A1 |

| Устройство микропрограммного управления | 1982 |

|

SU1086431A1 |

| Микропрограммное устройство управления модуля вычислительной системы | 1982 |

|

SU1034037A1 |

| Устройство для управления восстановлением микропрограмм при сбоях | 1982 |

|

SU1056193A1 |

| Микропрограммное устройство управления | 1981 |

|

SU968814A1 |

| Микропрограммное устройство управления | 1981 |

|

SU1005049A1 |

| Микропрограммное устройство управления | 1983 |

|

SU1130864A1 |

| Микропрограммное устройство управления | 1983 |

|

SU1109751A1 |

МИКРОПРОГРАММНОЕ УСТРОЙСТВО УПРАВЛЕНИЯ, содержащее регистр адреса, блок памяти, регистр микрокоманд, формирователь адреса, причем первый информационный вход регистра адреса соединен с входом кода операции устройства, выход регистра ащэеса соединен с адресным вход блока памяти, выход которого соейинен с входом регистра микрокоманд, выход поля адреса которого соединен с адресшлм входом формирователя адреса, вход логических ус- ; ловий устройства соединён с первьпу входом Логических условий формирователя адреса выход которого соединен с вторым информационным входом регистра адреса, отличающееся тем, что, с целью сокращения оборудования, оно дополнительно содеркит дешифратор, первый, второй, третий и четвертый элементы задержки, первый, второй, третий и четвертый бпок и элементов И, триггер, блок элементов ИЛИ, узел сдвига, сдновибратор. перш 1й и второй элементы И, причем выход поля Логических условий регистра микрокоманд соединен с первыми входами первого и второго блока элементов И и с входом дешифратора, ьыход логических условий которого соединен через лервый элемент задержки с вторым входом первого блока элементов И, ваыосод которогю соединен с вторым вход логических условий .формирователя 5 адреса, выход начала сборки деши4 тбра через второй элемент задержки соединен с единичным входом триггера, а выход ксшха сборки дешифратора соединен с нулевь1М ш:одом триггера, через одновифатор - с инверсным входом первого элемента И, а че. рез третий элемент задержки - с первыW ми входами третьего и четвертого блоков элементов И, выходы которых через блок элементов ИЛИ соеданены с выходом микроопераций устройства, единичный и нулевой выходы триггера соеди:Нены соответственно с вторым входом . второго блока элементов И и инверсньпл входом второго элемента И, выходы во1 fopax. соединены соответственно с инфоро мационным и управляющим входами ре00 гисгр савига, f ВЕЕЕХОД которого соединен с втор1ым входом третьего блока элемен« тов И, выход микроопераций регистра. МЕКрокаманд соединен с вторым входом четвертого блока элементов И, всыход тактовых импульсов устройства соединен с прямым входом первого элемента И, а через четвертый элемент задержки - с прямым входом второго элемента И.

- csj I tr5 I KjI

Cb

cc

O

огг

03

b-C3s

cser tv

ct;

О

I

ICO

CV

Й

|i

N S:

ЕШ

cxjO

S 25

т

26

т

26

Фав.2

ие.З

3,1

6

3,2

лг

/7

9иг. 4(

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Микропрограммное устройство управления | 1979 |

|

SU857995A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Под ред | |||

| В | |||

| Н | |||

| Мдлиновского | |||

| К., Техника); 1979, с | |||

| (поототил). | |||

Авторы

Даты

1983-05-30—Публикация

1982-02-09—Подача