Изобретение относится к вычисли,тельной технике.

Известен .параллельный аналого-цифрозой преобразователь (АЦП) содержащий разностные компараторы, представляющие собой сдвоенный обычный ком- 5 паратрр ДЗ

Объем оборудования в известном АЦП сокращен за счет того, что выходные цепи являются общими для каждой пары компараторов, т.е. сокраще- Ю но число логических элементов кодирующей схемы,.-

Наиболее близким к предлагаемому по технической сущности является параллель ный АЦП содержащий группы 15 компараторов, элементы памяти, источник тока смещения, выход которого подключен к пе рвому выводу резистивного делителя, а первая группа компараторов содержит компараторов, .20 где К- число разрядов, кодируемое компараторами первой группы, первые входы которых соединены с шиной преобразуемого сигнала, .выходы соединены попарно, кроме первого, первые входы 25 компараторов второй группы соединены с шиной стро:бирующего сигнала, вторые входы - с шинами рлорных нап.ряжений, а .соединенные попарно выходы подключены к управляющим входам элементов памяти второй группы, тактовые входы элементов памяти соединены вместе Г З}.

: Недостаток этого АЦП состоит в невысоком разрешении, т.е. невысока efo статическая точность. При числе двоичных разрядов вьЕле 7-8 объем 35 оборудования значительно возрастает, что затрудняет дальнейшее увеличение числа разрядов, т.е. .уведаичение разрешения, при реализации п %образоватёля на современной элементной базе. 40 : Цель изобретения - повышение точ- . ности. ...

Поставленная цель достигается тем/ что в .параллельный.АЦП,содержащий группы компараторов, элементы памяти,45 ИСТОЧН1Ш тока смещения, выход которого подключен к первому вводу резистивного делителя, а первая группа компараторов содержит компараторов, где к - число разрядов, кодируе- д мое компараторами первой группы, первые входы которых соединены с шиной преобразуемого сигнала, выходы соединены попарно, кроме первого, первые входы компараторов второй груп- . пы соединены с шиной стробирующего

сигнала, вторые входы - с шинами .

опорных напряжений, а соединенные попарно выходы подключены к управляю- щим входам элементов памяти второй

группы, т актовые входы элементов памя- ;„60 ти соединены вместе,введены блок сравнения кодов, элементы задержки, реп. гистр, дополнительные элементы памяти и компараторы, причем вторая rpvnnna компараторов выполнена на 1 компа- 5

раторах, где р - число разрядов. кодируемое компараторами второй ; руп пы разрядность преобразователя, входы первого и второго дополнительных компараторов подключены соответственно к шинам опорных напряжений и шине стробирующего сигнала, выход первого дополнительного компаратора подключен к тактовому входу регистра, выходы которого подключены к разрядным шинам, а. управлркяцие вхо подключены к выходам элементов памят тактовые входы которых соединены с входом блока сравнения кодов, первые вкоды которого подключены к выходам компараторов первой группы и через элементы задержки - к вторым входам блока сравнения кодов и управляющим входам элементов памяти первой группы, второй вывод резистивного делителя подключен к шине стробирукщего сигнала, выход второго дополнительного компаратО1 а подключен к управляющему входу дополнительного, элемента памяти, первый вход третьего дрполнительного компаратора соединён, с гцервым выводом резистивного делителя второй вход третьего дополнительного; компаратора соединен с шиной преобразуемого сигнала, а выход - к выходу первого компаратора первой группы.

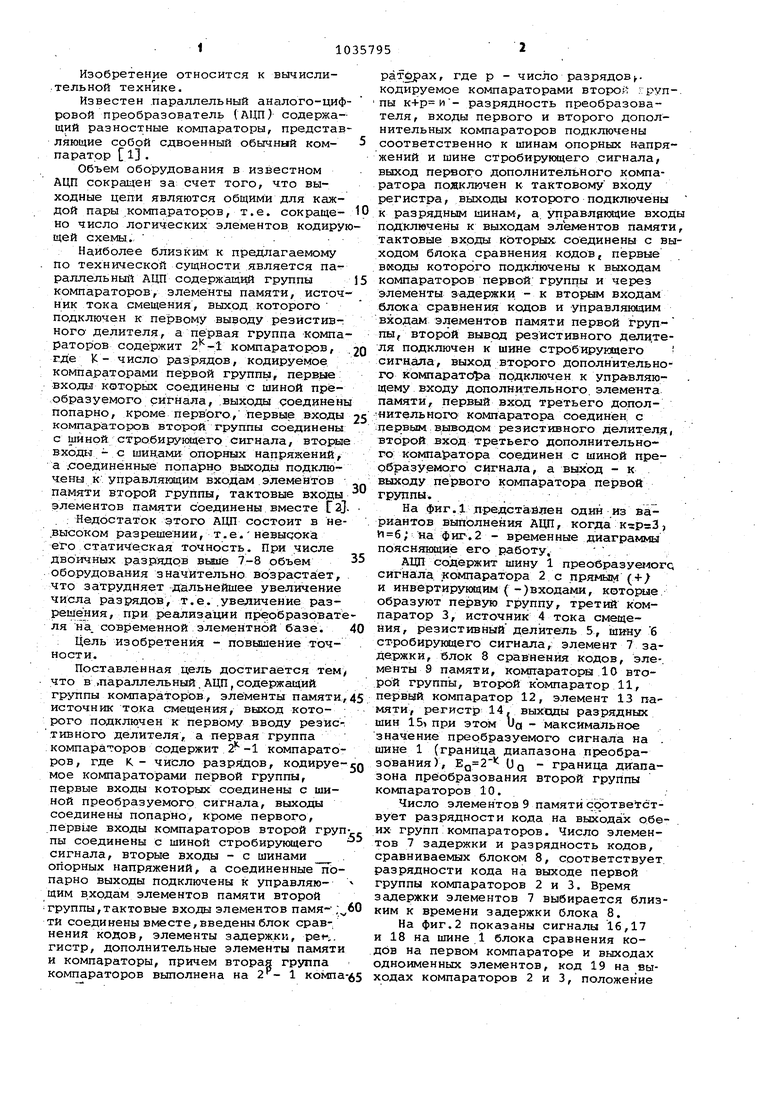

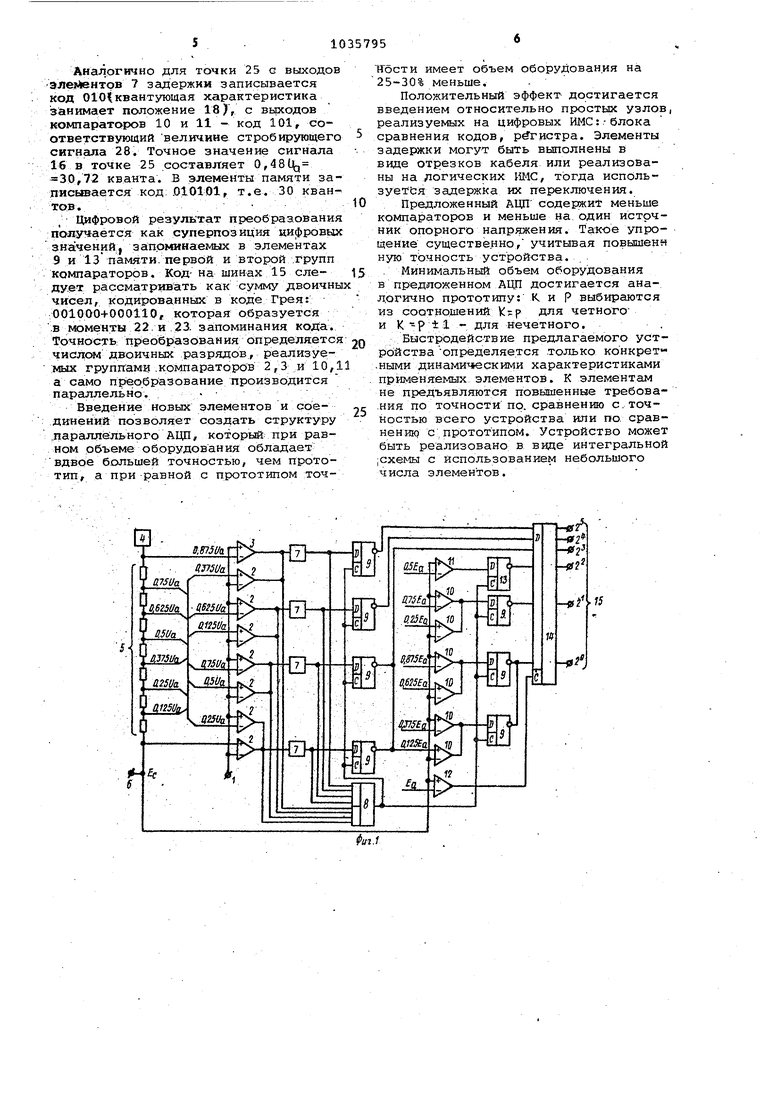

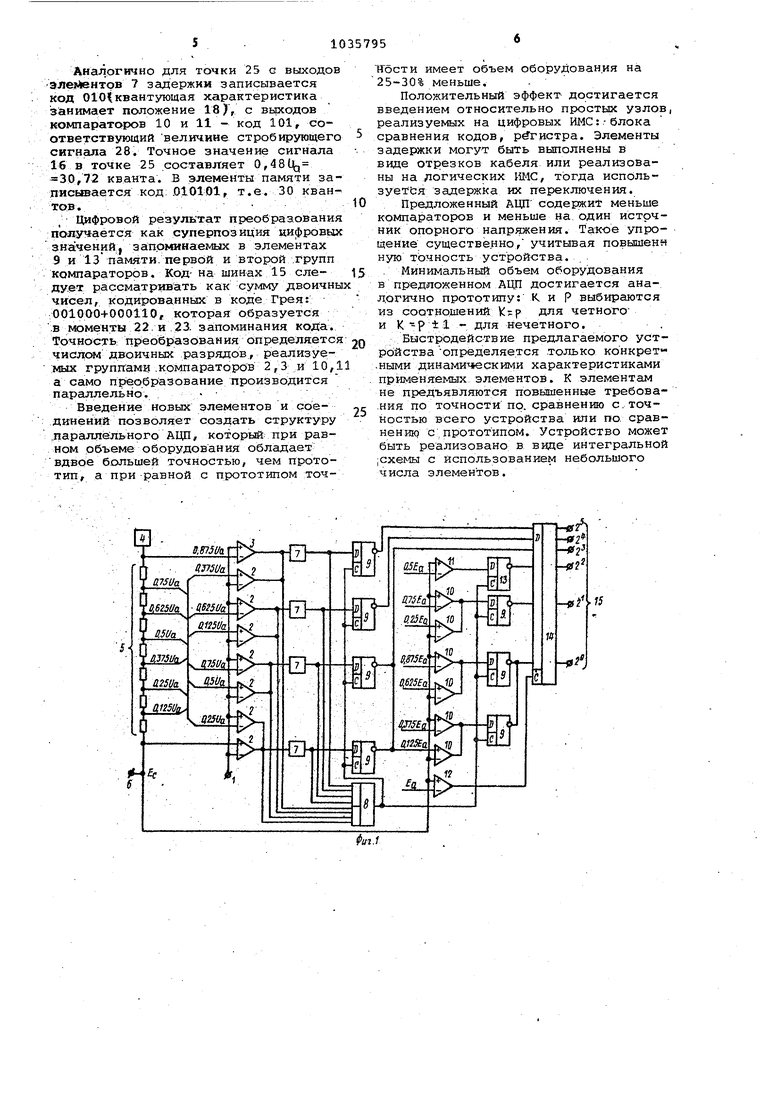

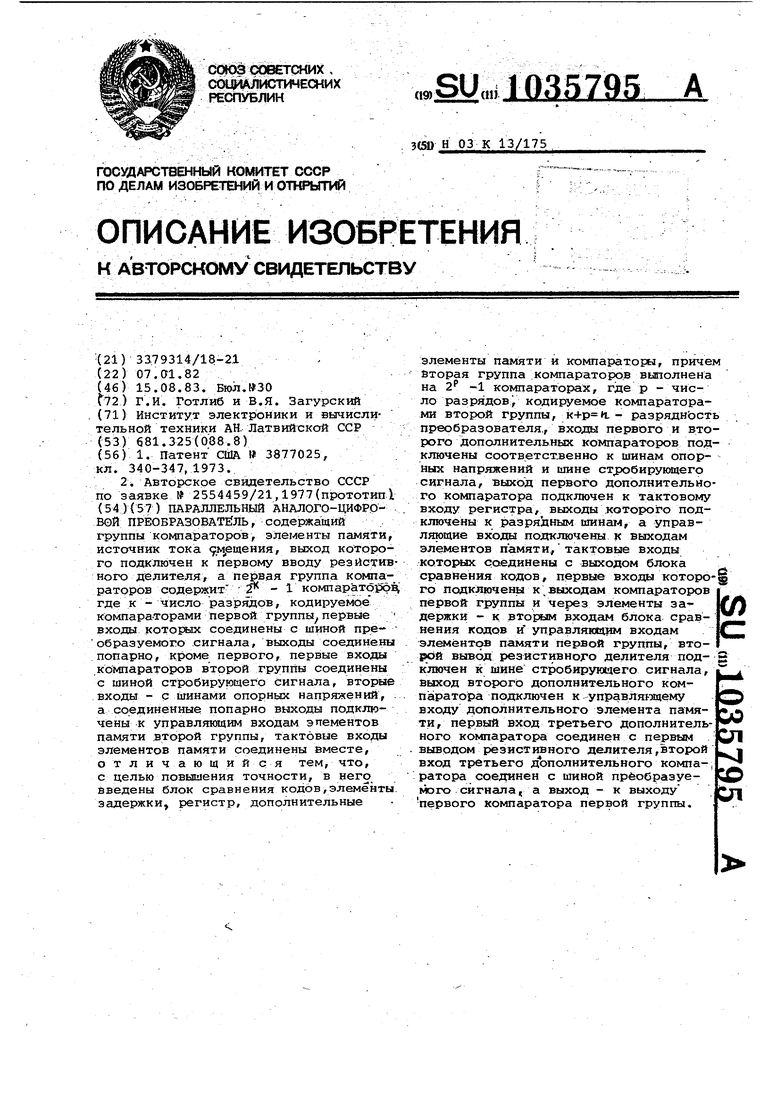

На фиг.1 .пpeдcтatijпfeн один из вариантов выполнения АЦП, когда , на фиг.2 - временные диаграммы поясняющие его работу, . .

АДП содержит шину 1 преобразуе14ог сигнала, котлтаратора 2с прямым ( + 7 и инвертирующим {-)входами, которые, образуют первую группу, третий компаратор 3, источник 4 тока смещения, резистивныйделитель 5, шину б стробирумдего сигнала, элемент 7 задержки, блок 8 сравнения кодов, эле-, менты 9 памяти, компараторы 10 второй группы, второй компаратор 11, первый компаратор 12, элемент 13 памяти, регистр 14. выходы разрядных шин 15 при этом Ufl - максимальное значение преобразуемого сигнала на . шине 1 (граница диапазона преобразования), UG граница диапазона преобразования второй группы компараторов 10.

Число элементов 9 памяти соотвегствует разрядности кода на выходах обеих групп:компараторов. Число элементов 7 задержки и разрядность кодов, сравниваемых блоком 8, соответствует разрядности кода на выходе первой группы компараторов 2 и 3. Время задержки элементов 7 выбирается близким к времени задержки блока 8.

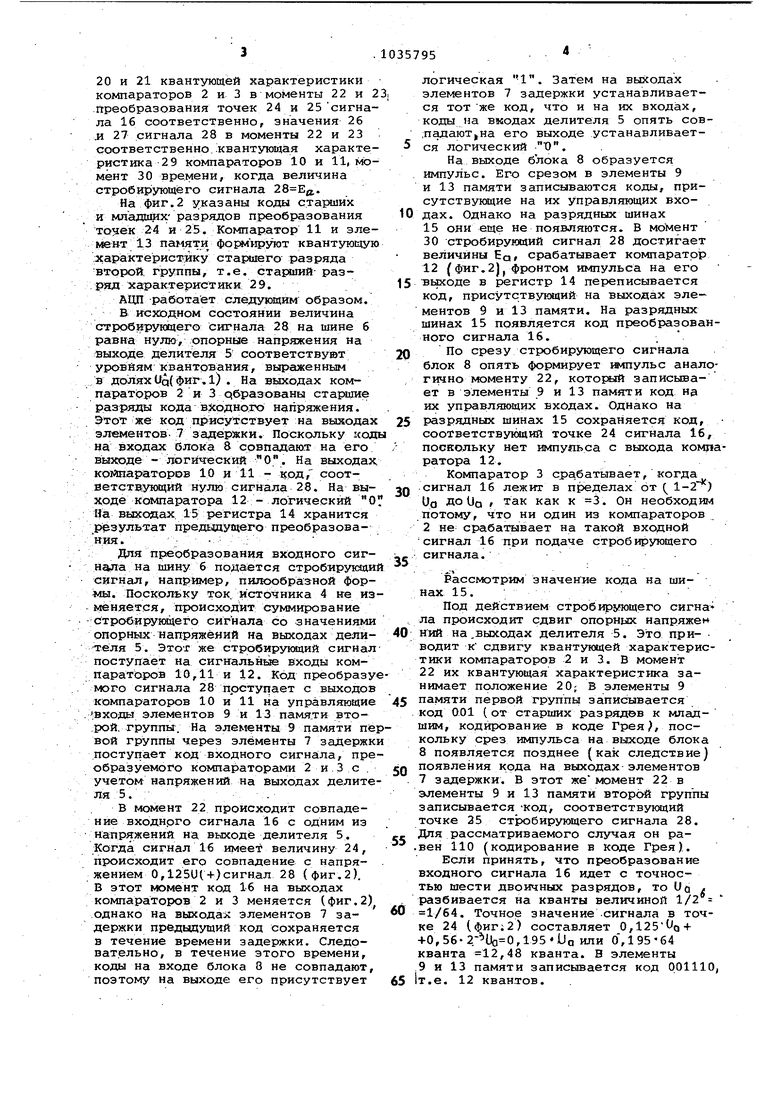

На фиг.2 показаны сигналы 1б,17 и 18 на шине 1 блока сравнения кодОв на первом компараторе и выходах одноименных элементов, код 19 на выходах компараторов 2 и 3, положение

20 и 21 квантующей характеристики компараторов 2 и 3 в моменты 22 и 23j -Ггреобразования точек 24 и 25сигнала 16 соответственно, значения 26 л 27 сигнала 28 в моменты 22 и 23 соответственно..квантующая характеристика 29 компараторов 10 и 11, момент 30 времени, когда величина стробирующёго сигнала ..

На фиг.2 указаны коды старших и младших- разрядов преобразования 24 и 25. Компаратор 11 и элемент 13 фо рмируют квантующую характеристгику старшего разряда второй группы, т.е. старший разряд характеристики 29.

АЦП работает следующим образом. В исходном состоянии величина стробирующего сигнала 28 на шине б равна нулю, опорные напряжения на выходе делителя 5 соответствуют уровням квантования, выраженным в доляхис|( фиг, l) . На выходах ком даратрров 2 и 3 рбразованы стаЕядие разряды кода входно.го напряжения. Этот же код присутствует на выходах элементов. 7 задержки. Поскольку коды на входах Ьлока 8 совпадают на его вызооде - логический О. На выходах. ко1йпараторов 10 и 11 - , соответств:ующнй нулю сигнала 28. На выходе компаратора 12 - логический О На выходах. 15 регистра 14 хранится р зультат предьщуа го преобразован;ия. - -- . .:

Для преобразования входного сигнала на шину б подается стробиружадий сигнал, например, пилообразной формы. Поскольку ток/источника 4 не изменяется, происходит суммирование

строб;Иру Ш1его сигнала со значениями опорных напряжений на выходах дели-теля 5. Этот же стробирующий сигналпоступает на сигнальные входы компараторов 10,11 и 12. Код преобразуемого сигнала 28 прступает с выходов компараторов 10 и 11 на управляющие

.входь элементов 9 и 13 памяти второй, группы. На элементы 9 памяти первой группы через элементы 7 задержки .поступает код входного сигна1ла, преобразуемого компараторами 2 и 3 с . учетом напряжений на выходах делителя 5. :. В момент 22 происходит совпадение входнрго сигнала 1б с одним из напряжений на выходе делителя 5. Когда сигнал 16 имеет величину 24, происходит его совпадение с напряжением О, 125U(+) сигнал 28 (фиг.2). В этот момент код 16 на выходах компараторов 2 и 3 меняется (фиг.2) .однако на выходах элементов 7 задержки предыдущий код сохраняется в течение времени задержки. Следовательно, в течение этого времени, кодда на входе блока 8 не совпадают, поэтому на выходе его присутствует

логическая 1. Затем на выходах элементов 7 задержки устанавливается тот же код, что и на их входах, коды на вкодах делителя 5 опять сов,падают,на его выходе устанавливается логический Т).

На выходе блока 8 образуется импульс. Его срезом в элементы 9 и 13 памяти записываются коды, присутствукнцие на их управляющих входах. Однако на разрядных шинах

15 они еще не появляются. В момент 30 стробирующий сигнал 28 достигает величины EQ срабатывает компаратрр 12 (фиг.2), фронтом импульса на его

15 выходе в регистр 14 переписывается код, присутствующий на выходах элементов 9 и 13 памяти. На разрядных шинах 15 прявляется код преобразованного сигнала 16.

2Q По срезу стробирующего сигнала

блок 8 опять формирует Ш1пульс аналогично моменту 22, который записывает в элементы 9 и 13 памяти код нэ их управляющих входах. Однако на

25 разрядных шинах 15 сохраняется код, соответствукяаий точке 24 сигнала 16, поскольку нет импульса с выхода компаратора 12.

Компаратор 3 срабатывает, когда

Q сигнал 16 лежит в пределах от Q 1-2) Uo ДО JQ , так как к 3. Он необходш. потому, что ни один из компараторов 2 не срабатывает на такой входной сигнал 16 при подаче стробирующего

с сигнала.

Рассмотрим значение кода на шинах 15.

Под действием стробирующего сигна . ла происходит сдвиг опорных напряжен 0 НИИ на.выходах делителя 5. Это при- водит к сдвигу квантующей характеристики компараторов 2 и 3. В момент 22 их квантующая характеристика занимает положение 20; В элементы 9 5 памяти первой группы записывается

код 001 ( от старших разрядов к младшим, кодирование в коде Грея, поскольку срез импульса на выходе блока

8появляется позднее (как следствие) П появления кода на выходах элементов

. 7 задержки. В этот жемомент 22 в элементы 9 и 13 памяти второй группы записывается -код, соответствующий точке 25 стробирующего сигнала 28. Для рассматриваемого случая он ра.вен 110 (кодирование в коде Грея).

Если принять, что преобразование входного сигнала 16 идет с точностью шести двоичных разрядов, то UQ . , разбивается на кванты величиной 1/2 0 1/64. Точное значение .сигнала в точке 24 (фиг;2) составляет 0,125% + +0,56-2.,195Ua или О, 195-64 кванта 12,48 кванта. В элементы

9и 13 памяти записывается код 001110, 5 1т.е. 12 квантов. Аналогично для точки 25 с выходов 7 задержки записывается код 010(квантующая характеристика занимает положение 18), с вьрсодов компараторов 10 и 11 - код 101, соответствующий величине стробирующего сигнала 28. Точное значение сигнала 16 в точке 25 составляет 0,48Ц-, 30,72 кванта. В элементы памяти записывается код: .010101, т.е. 30 квантов.. - . . . Цифровой результат преобразования получается как суперпоз иция «игровых значений, запоминаемых в элементах 9 и 13памяти, первой и ВТОЕХЗЙ .групп компараторов. Код- на шинах 15 следует рассматривать как сумму двоичны чисел, кодированных в коде Грея: 001000-1-000110, которая образуется .в моменты 22. и 23. запоминания кода. Точность преобразования определяетс чисдс 4 двоичных разрядов, реализуе ;мых группами .компараторов 2,3 и 10, а само преобразование производится параллельно. ; Введение новых элементов и соединений позволяет структуру параллельного АЦП, который при равном объеме оборудования обладает вдвое большей точностью, чем прототип, а при равной с прототипом точТбсти имеет объем оборудования на 25-30% меньше. Положительный эффект достигается введением относительно простых узлов, реализуемых на цифровых ИМС:.-блока сравнения кодов/ регистра. Элементы задержки могут быть выполнены в виде отрезков кабеля или реализованы на логических Ш-1С, тогда используетЬя задержка их переключения. Предложенный АЦП содержит меньше компараторов и меньше на один источник опорного напряжения. Такое упрощение сущее т в ё.н но/ учитывая повышенн ную точность устройства. . . . Минимальный объем оборудования в предложенном АЦП достигается аналогично прототипу: К и Р выбираются ИЗ соотношенийМСхр для четного и К -р ±1 - для нечетного. Быстродействие предлагаемого устрсэйства определяется .только конкрет,ными динамическими характеристиками применяемых, элементов. К элементам не предъявляются повышенные требова,ния по точности по. сравнению с. точностью всего устройства или по. сравнению с . прототипом. Устройство может быть реализовано в виде интегральной ;схемы с использованием небольшого числа злементов.

| название | год | авторы | номер документа |

|---|---|---|---|

| Параллельный аналого-цифровой преобразователь | 1978 |

|

SU769731A1 |

| Параллельный аналого-цифровой преобразователь | 1977 |

|

SU934574A1 |

| Аналого-цифровой преобразователь | 1980 |

|

SU884127A1 |

| Аналого-цифровой преобразователь | 1986 |

|

SU1464289A1 |

| АНАЛОГО-ЦИФРОВОЙ ПРЕОБРАЗОВАТЕЛЬ ПОРАЗРЯДНОГО СРАВНЕНИЯ | 1991 |

|

RU2020749C1 |

| Параллельный аналого-цифровой преобразователь | 1982 |

|

SU1019623A1 |

| Многоканальный аналого-цифровой преобразователь | 1980 |

|

SU993468A1 |

| Параллельно-последовательный аналого-цифровой преобразователь | 1983 |

|

SU1211881A1 |

| Устройство для регистрации информации | 1989 |

|

SU1698895A1 |

| Программируемый аналого-цифровой преобразователь | 1987 |

|

SU1732469A1 |

ПАРАЛЛЕЛЬНЫЙ АНАЛОГО-ЦИФРр- . ВОЙ ПРЕОБРАЗОВАТЕЛЬ, содержащий группы компараторов, элементы памяти, источник тока (м щенкя, выход которого подключен к первому вводу резйстивного делителя, а первая группа коьшараторов содержит ; - 1 компараторрв где к - число разрядов, кодируемое компараторами первой группы первые входы которых соединены с шиной пре- образуемого сигнала, выходы соединены попарно, кроме первого, первые входы кЬмпараторов второй группы соединены с шиной стробирующего сигнала, вторые входы - с шинами опорных напряжений, . . а соединенные попарно выходы подключены к управляющим входам эпементов памяти .второй группы, тактовые входы элементов памяти соединены вместе, о т л и ч а ю щ и и с я тем, что, с целью повышения точности, в него введены блок сравнения кодов,элементы, задержки регистр, дополнительные элементы памяти и компараторы, причем Вторая группа .компараторо.в выполнена на 2 -1 колтараторах, где р - число разрядов, кодируемое компараторами второй группы, - разрядность преобразователя., входы первого и второго дополнительных компараторов подключены соответственно к шинам опорных напряжений и шине cт юбиpyющeгo сигнала, выход первого дополнительного компаратора подключен к тактовому входу регистра, выходы .которого подключены к разрядным шинам, а управляющие вхохш подключены к выходам элементов памяти, тактовые входы которых соединены с выходом блока сравнения кодов, первые входы которого подключены к,выходам компараторов первой группы и через элементы задержки - к вторым входам блока сравнения кодов и управляющим входам элементов памяти Первой группы, второй вывод резистивного делителя подк лючеи к шине стробкруквдего сигнала, выход второго дополнительного компаратора подключен к yпpaвля эщeмy входу дотолнительного элемента памя:о :л г ти, первый вход третьего дополнительного компаратора соединен с первым выводом резистивного делителя,второй вход третьего дополнительного компа-, ратора соединен с шиной преобразуемого сигнала, а выход - к выходу :д первого компаратора первой группы. I

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Патент США 3877025, кл | |||

| Способ отопления гретым воздухом | 1922 |

|

SU340A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

Авторы

Даты

1983-08-15—Публикация

1982-01-07—Подача