(54) П РЛЛЛЕЛЬНЬГЙ АНАЛОГО-ЦИФРОВОЙ ПРЕОБРАЗОВАТЕЛЬ

| название | год | авторы | номер документа |

|---|---|---|---|

| Параллельный аналого-цифровой преобразователь | 1982 |

|

SU1035795A1 |

| Параллельный аналого-цифровой преобразователь | 1978 |

|

SU769731A1 |

| Аналого-цифровой преобразователь последовательного приближения | 1981 |

|

SU1018228A1 |

| Аналого-цифровой преобразователь считывания | 1977 |

|

SU702514A1 |

| Параллельный аналого-цифровой преобразователь | 1980 |

|

SU869026A1 |

| Преобразователь напряжения в код | 1977 |

|

SU728222A1 |

| Аналого-цифровой преобразователь | 1978 |

|

SU767965A1 |

| ИНТЕГРИРУЮЩИЙ АНАЛОГО-ЦИФРОВОЙ ПРЕОБРАЗОВАТЕЛЬ | 1991 |

|

RU2012131C1 |

| Аналого-цифровой преобразователь | 1979 |

|

SU839046A1 |

| Аналого-цифровой преобразователь | 1986 |

|

SU1464289A1 |

I

Изобретение относится к вычислительной технике.

Известен парал;кльный аналого-цифровой преобразователь, содержащий пара; лельно включенные анализаторы уровня, выполненные на дифференциальных каскадах, и элементы ИЛИ, аналоговый сигнал поступает на входы параллельно включенных анализаторов уровня, причем каждый из них образует на своем выходе логический сигнал, значение которого определяется настройкой данного анализатора уро вня и величиной преобразуемого напряжения, выходные сигналы анализаторов преобразуются в обычный двоичный код либо в код Грея fl.

Недостатком устройства является ог раничение по точности, поскольку при увеличении числа цвоичных разрядов, т.е. увеличение точности, число дифференциальных каскадов пропорционально (), где И- число разрядов.

По этой причине число разрядов не более 2-3, что ограничивает точность преобразователя.

Известен парал/ельный аналого-цифровой преобразователь, содержащий в случае И разрядов И групп компараторов и элементов памяти, причем общее число компараторе в этом случае составляет (), а элементов памяти 2, выходы компараторов подсоединены к управляк 10щим входам элементов памяти, тактовые входы которых подсоединены к источнику стробирующего сигнала, а выходы подсоединены к разрядным шинам 2J.

ts

Однако устройство имеет низкую точность преобразования.

Цель изобретения - увеличение точности преобразовайия при упрощении з гройства.

20

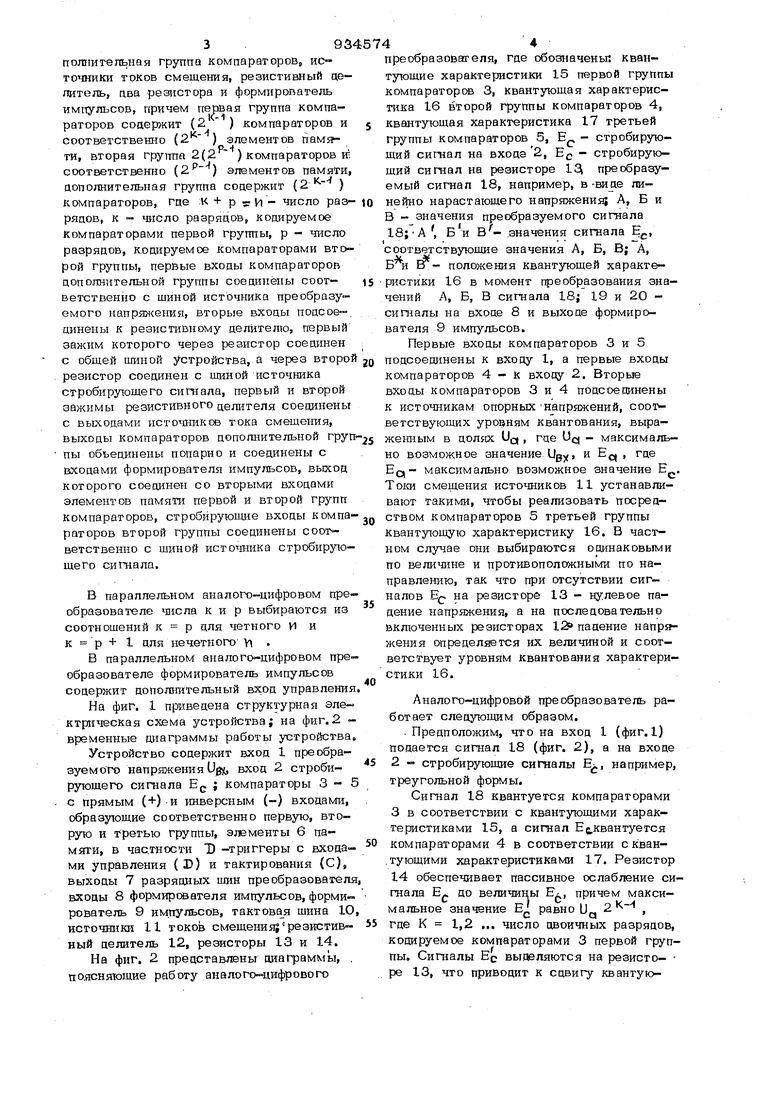

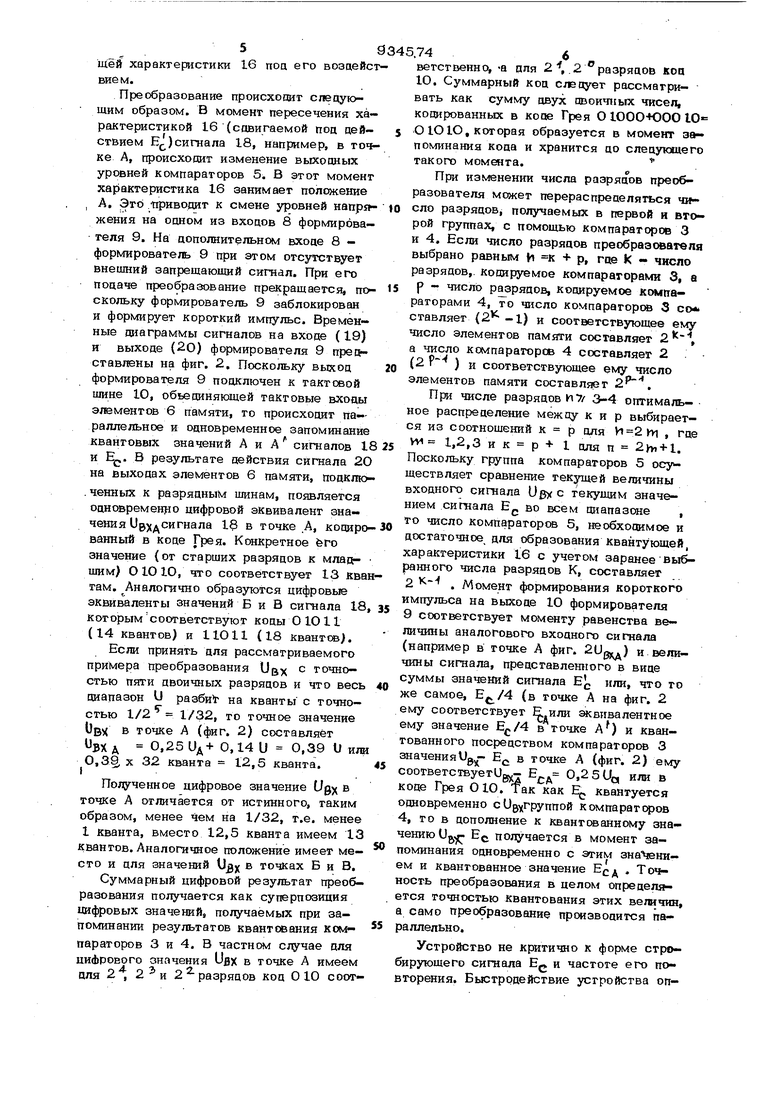

Указанная цель достигается тем, что в параллельный аналого-цифровой преобразователь, содержащий две группы компараторов, элементы памяти, введены дополнигепьиая группа компарагоров, исгошики токов смещения, резистивный целитель, пва резн-стора и формирователь импульсов, причем первая группа компарагоров соцержит (2 ) компараторов и соответственно ( ) элементов naMsfти, вторая группа 2(2 ) компараторов и соответственно () элементов памяти, дополнительная группа соцержит (2 ) компараторов, гце :К + р - ц - число разряцов, к - число разрядов, кодируемое Компараторами первой группы, р - число разрядов, кодируемое компараторами второй группы, первые входы компараторов дополнительной группы соединены соот- ветственно с шиной источника преобразуемого напр5И{е1шя, вторые входы поасое цинены к резистивному целителю, первый зажим которого через резистор соединен с общей шиной Устройства,.а через второй резистор соединен с щиной источника стробирующего сигнала, первый и второй зажимы резистивного целителя соединены с выходами исто шиксв тока смещения, выходы компараторов дополнительной груп пы объединены попарно и соединены с входами формирователя импулгэсов, выход Которого соединен со вторыми входами элементов памяти первой и второй групп Компараторов, стробирующие входы компараторов второй группы соединены соот- ветственно с щиной источника сгробирующего сигнала. В параллельном аналого-цифровом преобразователе шcлa Кир выбираются из соотнощений к р цля четного и и к р + 1 для нечетного . В параллельном аналого-цифровом преобразователе формирователь импульсов содержит дополнительный вход управления На фиг. I приведена структурная электрическая схема устройства J на фиг. 2 временные диаграммы работы устройства Устройство соцержит вход 1 преобразуемого напряжения U0), вход 2 стробирующего сигнала Е | компараторы 3 5 с прямым (+)-и 1шверсным (-) входами, образующие соответственно первую, вторую и т ретью группы, элементы 6 памяти, в частности Т) -триггеры с входами управления {D) и тактирования (С), выходы 7 разрядных шин преобразователя входы 8 формиршателя импульсов, формирователь 9 импульсов, тактовая шина 10 источники II токов смещения|резистивный делитель 12, резисторы 13 и 14. На фиг. 2 представлены диаграммы, . по.ясняющие работу аналого-цифрового преобразователя, где обозначеньк квантующие характеристики 15 первой группы компараторов 3, квантующая характеристика 16 второй группы компараторов 4, квантующая характеристика 17 третьей группы компараторов 5, Е-, - стробирующий сигнал на входе 2, Е - стробирующий сигнал на резисторе 12 преобразуемый сигнал 18, например, в-вице линейно нарастающего напряжения; А, Б и В - значения преобразуемого сигнала 18;А , Б и .значения сигнала Е, соответствующие значения А, Б, В; А, Б и положения квантующей характе- ристики 16 в момент преобр азования значений А, Б, В сигнала 18; 19 и 20 сигналы на входе 8 и выходе формирователя 9 импульсов. Первые входы компараторов 3 и 5 подсоединены к входу 1, а первые входы компараторов 4 - к входу 2. Вторые входы компараторов 3 и 4 подсоецинены к источникам опорныхнапряжений, соответствующих уровням квантования, выраженным в цолях UQ , где Uq - максимально возможное значение Ugy, и Ej, , гце EQ- максимально возможное значение Е . Токи смещения источников 11 устанавливают такими, чтобы реализовать посредством компараторов 5 третьей группы Квантующую характеристику 16. В частном случае они выбираются одинаковыми по величине и противоположными по направлению, так что при отсутствии сигналов Е на резисторе 13 - нулевое пацение напряжения, а на последовательно включенных резисторах I2l падение напр жения опрецеляется их величиной и соответствует уровням квантования характеристики 16. Аналого-цифровой преобразователь работает слецующим образом. .Предположим, что на вход 1 (фиг. 1) подается сигнал 18 (фиг. 2), а на входе 2- стробирующие сигналы Е, например, треугольной формы. Сигнал 18 квантуется компараторами 3в соответствии с квантующими характеристиками 15, а сигнал Е квантуется компараторами 4 в соответствии с кван- .тующими характеристиками 17. Резистор 14 обеспечивает пассивное ослабление сигнала Е до величины Е, причем максимальное значение Е равно U , гце К 1,2 ... число двоичных разрядов. Кодируемое компараторами 3 первой группы. Сигналы ЕС выделяются на резисто- ре 13, что приводит к сдвигу квантую5дщей характеристики 16 под его воздейсг QfiQM. Пре образование происхоонг слеаук щим образом. В момент пересечения характеристикой 16 (совигаемой под действием Е()сигнала 18, например, в точке А, происходит изменение выходных уровней компараторов 5, В этот момент характеристика 16 занимает положение А. Это ириводат к смене уровней Hanps жения на одном из входов 8 формирова- теля 9. На дополнительном входе 8 формироватеш, 9 при этом отсутствует внешний запрещающий сигнал. При его подаче преобразование прек ращается, nt скольку формирователь 9 заблокирован и формирует короткий импульс. Временные диаграммы сигналов на входе (19) и выходе (2О) формирователя 9 npetjставлены на фиг. 2, Поскольку выход формирователя 9 подключен к тактовой ишне 10, объединяющей тактовые входы зла ментов 6 памяти, то происходит па-раллельное и одновременное запоминание квантоввгх значений А и А сигналов 18 и R,. В результате действия сигнала 2О на выходах элементов 6 памяти, поцклк . ченных к разрядным шинам, появляется одновременро цифровой эквивалент значения и хдсигнала 18 в точке .А, кодированный в коде Грея. Конкретное fero значение (от старших разрядов к младшим) О 1О Ш, что соответствует 13 ква там. Аналогично образуются цифровые „ ;, , эквиваленты значений Б и В сигнала 18 которым соответствуют коды О 10 11 (14 квантов) и ИО11 (18 квантсв). Если принять для рассматриваемого примера преобразования UBX точностью пяти двоичных разрядов и что весь диапазон U разбив на кванты с точностью 1/2 1/32, то точное значение UBX в точке А (фиг. 2) составляет UBX д 0,25 ид+ 0,14 и 0,39 U или 0,39, X 32 кванта 12,5 кванта. Подученное цифровое значение Ugx в точке А отличается от истинного, таким образом, менее чем на 1/32, т.е. менее 1 кванта, вместо 12,5 кванта имеем 13 квантов. Аналогичное положение имеет место и для значений Ujx точках Б и В. Суммарный цифровой результат преобразования получается как суперпозиция цифровых значений, получаемых при запоминании результатов квантования компараторов 3 и 4. В частном случае для циЛрового значения UflX в точке А имеем для 2 2 разрядов код 010 соот.746 вегстоенно, -а для 2, .2 разряцов коц Суммарный коц с/коует россмагривать как сумму двух овоишых чисел, кодированных в коое Грея О ШОО-ЮОО 10 О ЮЮ, которая образуется в момент запоминания кода и хранится до следующего такого момента. При изменении числа разрядов преобразователя может перераспределяться чиело разрядов, получаемых в первой и вгорой группах, с помощью компараторов 3 и число разрядов преобрааоватепя выбрано равным И к + р, гце К - число разрядов,, кодируемое компарагорами 3, а р - число разрядов, кодируемое компараторами 4, то число компараторе 3 со ставляет (2 -I) и соответствующее ему число элементов памяти составляет , а число компараторев 4 составляет 2 ( ) и соответствующее ему число элементов памяти составляет , При числе разрядов 3-4 оптимальное распределение между к и р выбирается из соотношений к р для , где W1 1,2,3 ик р+1шшп 2уу, + 1, Поскольку группа компараторов 5 осу ществляет сравнение текущей величины входного сигнала U0x с текущим значением сигнала Е, во всем диапазоне , то число компараторов 5, необходимое и достаточное для образования квантующей, характеристики 16 с учетом заранее выбранного числа разрядов К, составляет 2 . Момент формирования короткого „,гг,г,т,оо „о ь , in А импульса на выходе 1О формирователя Q „..,„. ..„.Т :,.„.:.„ ™ 9 соответствует моменту равенства величины аналогового входного сигнала (например в точке А фиг. 21)) и ведичины сигнала, представленного в виде суммы значений сигнала Ej, или, что то же самое, (в точке А на фиг. 2 ему соответствует .или асвивалентное ему значение в точке А ) и квантованного посредством компараторов 3 значенияи - Е в точке А (фиг. 2) ему cooTBeTCTByeTUg j 0,25Uoi или в коде Грея О 10. так как Е квантуется одновременно си угруппой компаратфов 4, то в дополнение к квантсжаНному значению U ЕС получается в момент запоминания одновременно с этим ем и квантованное значение . Точность преобразования в целом oпpeдeЛJ ется точностью квантования этих величин, а само преобразование производится параллельно. Устройство не критично к форме стробирующего сигнала Е и частоте его повторения. Быстродействие устройства оп79рецеляются только конкретными динамическими характерисгиками применяемых элементов. К элементам не предъявляют повышенных требований по точности по сравнению с точностью всего устройства Компараторы 4 могут иметь хуцшую чувствительность, нежели остальные, поскольку они участвуют в преобразовании сигнала , амплитуда которого может быть равна (Ja или выбрана большей. ройство может быть реализовано в виде интегральной схемы с использованием небольшого числа элементов. Формула изобретения I. Параллельный аналого-цифровой преобразователь, содержащий две группы компараторов, сигнальнью входы компараторов первой группы подсоединены соответственно к шине источника преобразуемого напряжения, входы компараторов обеих групп подсоединены к шинам источников опорных напряжений, вь ходы компараторов обеих групп, кроме первого компаратора первой группы, объе динены попарно и соединены с управл5гюпшми входами элементов памяти, кроме первого выход первого компаратора пе- вой группы соеданен с управляющим входом элемента памяти, выходы элементов памяти подсоединены к разрядным шинам о т лш чающийся тем, что, с целью псеышения точности при упрощении устройства, введены дополнительная гругр па .компараторов и источники токов смещения, резистивный делитель, два рез№стора, формирователь импульсов, причем первая группа компараторов содержит ( ) компараторов и соответственно (2 ) элементов памяти, вторая груп748па 2 (2 ) компараторов и соответственно (2 ) элементов, памяти, допотьнительная группа содержит (2 ) компараторов, где к + р И- число paBpjrдов, к - число разрядов, кодируемое компараторами первой группы, р - число ра&РЯДОВ, кодируемое. компараторами второй группы, первые входы компараторов дополнительной группы соединены соответственно с шиной источника преобразуемого напряжения, вторые входы подсоединены к резистивному делителю, первый зажим которого через резонатор соединен с общей шиной устройства, а через второй резистор соединен с шиной источника стробирующего сигнала, первый и второй зажимы резистивного делителя соединены с выходами источников тока смещения, выходы компараторов дополнительной группы объединены попарно и соединены с входами формирователя, импульсш, выход Которого соединен со вторыми входами элементов памяти первой и второй групп компараторов, стробирующие входы Компараторов второй группы соединены соответственно с шиной источника стробирующего сигнала. 2.Преобразователь по п. 1, о т личающийся тем, что числа к и р выбирают из соотношений к s р для четного п и к -i р + 1 для нечетного vi. 3.Преобразователь по п. 1, о т Личающийся тем, что формирователь импульсов содержит дополнительный вход управления. Источники информации, принятые во внимание при экспертизе 1.Патент США М 3806915, кл. 340-247, 1972. 2.Патент США №3829853, кп, 340-247, 1972 (прототип).

Фиг.1

Авторы

Даты

1982-06-07—Публикация

1977-12-13—Подача