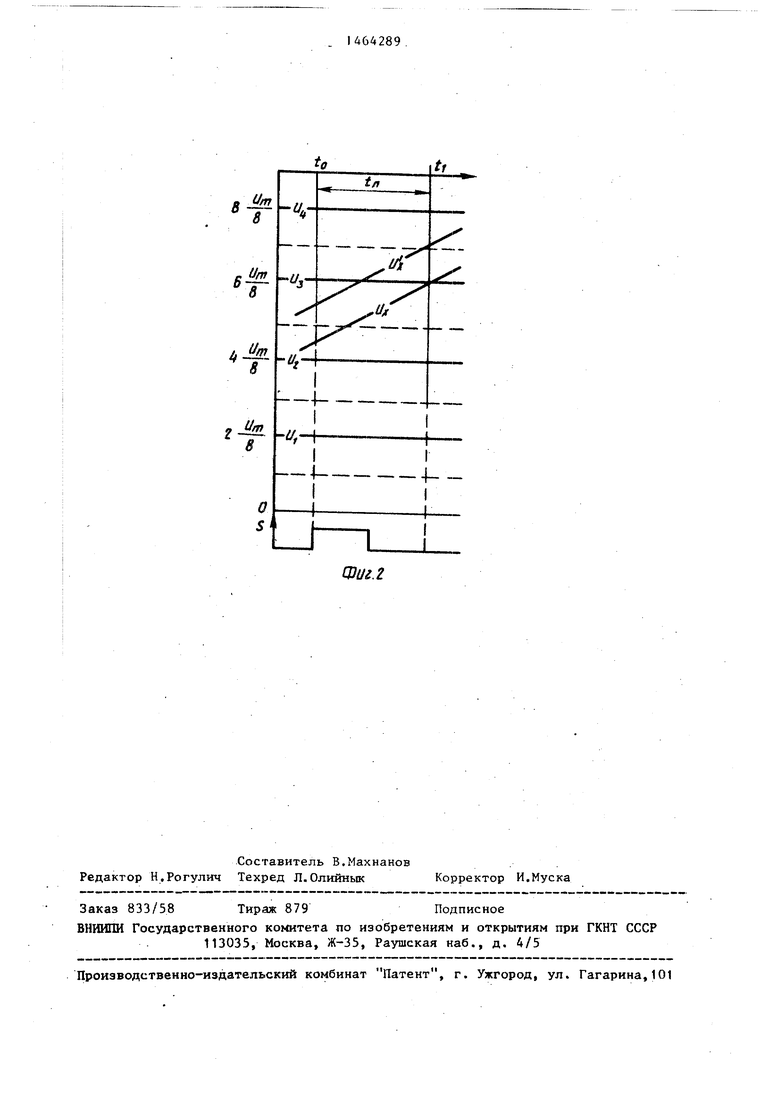

рых входах компараторов 3, входящих в состав трехразрядного устройства, сигнал и х на выходе сумматора 8, сигналы Ut f-U на выходе делителя 1, величина и опорлого напряжения, величина t времени преобразования и сигнал S на входах синхронизации регистров 5 и 6,

Устройство работает следующим образом.

На выходах делителя 1 формируется шкала опорных напряжений с квантом , где 2 - число резисторов делителя 1. С этой шкалой сравнивается сигнал U)(, поступающий на вторые входы компараторов 3 через элемент 7 задержки, обеспечивакйций такую же задержку сигнала U, как аналоговый сумматор 8, с помощью которого и масштабного усилителя входной сигнал сдвигается на величину полкванта

опорной шкапы, С выхода аналоV2

гового сумматора 8 сигнал I) , равньй и,-1)/2 поступлет на вторые входы компараторов 4. Сравнение сигнала и со шкалой делителя 1 эквивалентно сравнению сигнала 1Ь со шкалой опорных напряжений, сдвинутой на пол - кванта Цп/2 относительно шкалы делителя 1 ,

Таким образом, в устройстве обеспечивается сравнение сигнала U с уровнями напряжений четных квантов

2 , ,...,2 -и„/2

р 1

и

с уровнями напряжений нечетных кван- , 3Uj2 -,...,() /2 , В момент to передним фронтом сигнала S, поступающего на входы синхронизации регистров 5 и 6, результаты сравнения сигнала Uу со шкалой четных квантов запоминаются в регистре 5 и преобразуются приоритетным шифратором 10 к моменту t в оценку Р старших разрядов сигнала UxCto), а результаты сравнений сигнала и со шкалой нечетных квантов запоминаются в регистре 6 и поступаю на информационные входы мультиплексора 11, на адресные входы которого поступает код с выходов шифратора 10 В соответствии с этим кодом из всех результатов сравнений, записанных в регистр 6 в момент t, на выход мультиплексора поступает один результат сравнения сигнала UxCt) с уровнем ближайшего опорного напряжения, которое отличается от сигнала ) на величину, меньшую, чем т.е. на выходе мультиплексора формируется

значение младшего разряда Р+1-разрядного эквивалента сигнала U,(tp).

На временных диаграммах (фиг.2) показаны сигналы трехразрядного устройства, содержащего четыре компаратора 3 и четыре компаратора Д. В момент te в регистре 5 запоминается унитарный код двойки, так как сигнал

0 (tp) Uj , а в регистре 6 - унитарный код двойки, так как сигнал Uj Ui(t6) УЗ.

К моменту t , код регистра 5 преобразуется приоритетным шифратором 10

5 в двоичный код двойки, который поступает на старшие выходные шины устройства и адресные входы мультиплексора 11. В соответствии с этим кодом на выход мультиплексора 11 поступает

Q равный нулю результат сравнения сигнала U;,(te) с опорным уровнем U. Таким образом, к моменту t, на выходах устройства формируется код 100i- -4,„, что соответствует сигналу 4U|n/

5 /8 U,(t,) .

В предлагаемом устройстве, содержащем делитель из 2 резисторов, обеспечивается формирование P fl-разрядной оценки входного сигнала U.

Q Причем, поскольку средние входные

токи I

5X1

И I

вхг.

5

компараторов 3 и 4 равны по величине, но противоположны по направлению, то величина дифференциальной нелинейности от входных токов равна

2 /Ip-R-f2 -lp- R)/2,

где- Мр I

Iflx-I

-61№

0

BXi

-средний входной ток компараторов 3j

-средний входной ток компараторов 4.

Таким образом, устройство имеет в два раза лучшую разрешающую способность и в 1цк,/1р раз меньшую диффе- 5 ренциальную-нелинейность одновременно.

Формула изобретения

Аналого-цифровой преобразователь, содержащий резистивный делитель нап0 ряжения, первый и второй входы ког- торого подключены соответственно к общей шине и вшне опорного напряжения, а выходы соединены с первыми входами первой группы п-каска ных

5 стробирукщих компараторов, вторые входы которых объединены и подключены к выходу аналогового сумматора, первый вход которого является шиной входного сигнала, а второй вход соединен с выходом источника смещения, а стробирующие входы первой группы п-каскадных стробирующих компараторов подключены к шине стробирующего сигнала, приоритетный шифратор, о т - личающийся тем, что, с целью повышения быстродействий и точности, в него введена вторая груп- па п-каскадных стробирующих компара- торов, мультиплексор и элемент задержки, через которые шина входного сигнала соединена с первыми входами

стробирующих компараторов вьшолнены на транзисторах противоположной проводимости, стробирукщие входы втЬрой группы п-каскадных стробирующих компараторов соединены смпиной стррби- рующего сигнала, выходы через приори тетный шифратор соединены с управля- ющим входом мультиплексора и являются выходной шиной старших разрядов, информационные входы мультиплексора соединены с соответствующими выходам первой группы п-каскадных строЙ рую- щих компараторов, а выход является

второй группы стробирующих компараторов, вторые входы которых объединены gвыходной шиной младшего разряда, при с соответствующими входами первойэтом источник смещения выполнен на группы п-каскаднь х.стробирующихмасштабирующем усилителе, вход кото- компараторов, причем входные каскадырого подключен к шине опорного нап- первой и второй групп п-каскадныхряжения.

стробирующих компараторов вьшолнены на транзисторах противоположной проводимости, стробирукщие входы втЬрой группы п-каскадных стробирующих компараторов соединены смпиной стррби- рующего сигнала, выходы через приоритетный шифратор соединены с управля- ющим входом мультиплексора и являются выходной шиной старших разрядов, информационные входы мультиплексора соединены с соответствующими выходами первой группы п-каскадных строЙ рую- щих компараторов, а выход является

выходной шиной младшего разряда, при этом источник смещения выполнен на масштабирующем усилителе, вход кото- рого подключен к шине опорного нап- ряжения.

| название | год | авторы | номер документа |

|---|---|---|---|

| Двухтактный аналого-цифровой преобразователь | 1985 |

|

SU1336236A1 |

| Аналого-цифровой преобразователь | 1985 |

|

SU1336237A1 |

| Параллельный аналого-цифровой преобразователь | 1986 |

|

SU1332533A1 |

| Аналого-цифровой преобразователь | 1986 |

|

SU1325696A1 |

| Многоканальный аналого-цифровой преобразователь | 1985 |

|

SU1339890A1 |

| Параллельный аналого-цифровой преобразователь | 1982 |

|

SU1035795A1 |

| Параллельно-последовательный аналого-цифровой преобразователь | 1983 |

|

SU1211881A1 |

| Аналого-цифровой преобразователь | 1987 |

|

SU1494218A2 |

| Программируемый аналого-цифровой преобразователь | 1987 |

|

SU1732469A1 |

| Аналого-цифровой преобразователь | 1983 |

|

SU1181144A1 |

Изобретение относится к измерительной технике и может использоваться для аналого-цифрового преобразования широкополосных динамических сигналов. Целью изобретения является повышение быстродействия и точности, Устройство содержит резистивный делитель напряжения из 2 резисторов, первый и второй входы которого соединены с общей шиной и шиной опорного напряжения, а выходы - с первыми входами двух групп компараторов, Измеряемьй сигнал Ux поступает через элемент Изобретение относится к измерительной технике и предназначено для аналого-цифрового преобразования широкополосных динамических сигналов. Цель изобретения - повышение быстродействия и точности, На фиг,1 изображено предлагаемое устройство; на фиг.2 - временные диаграммы. Устройство содержит резистивный делитель 1 напряжения, шину 2 опорного напряжения, две группы компарато задержки на вторые входы одной из групп компараторов и сравнивается со шкалой опорных напряжений делителя, с которой также сравнивается с помощью компараторов другой группы выходной сигнал и аналогового сумматора, на один вход которого поступает измеряемый сигнал, а на другой вход - сигнал с выхода масштабного усилителя, равный половине кванта шкалы делителя. В момент t, по синхросигналу S результаты сравнений сигнала со-; шкалой делителя запоминаются в первом регистре и поступают на информационные входы мультиплексора, а результаты сравнения сигнала Ux со шкалой делителя запоминаются во втором регистре и к моменту t, преобразуются приоритетньш шифратором в двоичный код Р старших разрядов оценки сигнала V f (t), в соответствии с которым на выходах мультиплексора выделяется значение младшего разряда оценки сигнала U(to), и, таким образом, формируется Р+1-разрядная оценка, измеряемого сигнала, 2 нл. ров 3 и 4 с регистрами 5 и 6 на выходе (стробирующих компараторов), элем мент 7 задержки, аналоговый сумматор 8, источник 9 смещения, выполненный на масштабирующем усилителе, приори- тетньй шифратор 10 и мультиплексор 11 Входные каскады первой и второй групп компараторов выполнены соответственно на транзисторах противоположной проводимости. На временных диаграммах (фиг,2) показаны измеряемый сигнал U на втоа Л Ф NP 00

8

8

Urn 8

% 8

г

- 8

О 5

Фиг. г

| Титце У, и др | |||

| Полупроводниковая схемотехника, 1982, с | |||

| Прибор для вычерчивания конических сечений | 1922 |

|

SU457A1 |

| 1991 |

|

RU2004150C1 | |

Авторы

Даты

1989-03-07—Публикация

1986-11-04—Подача