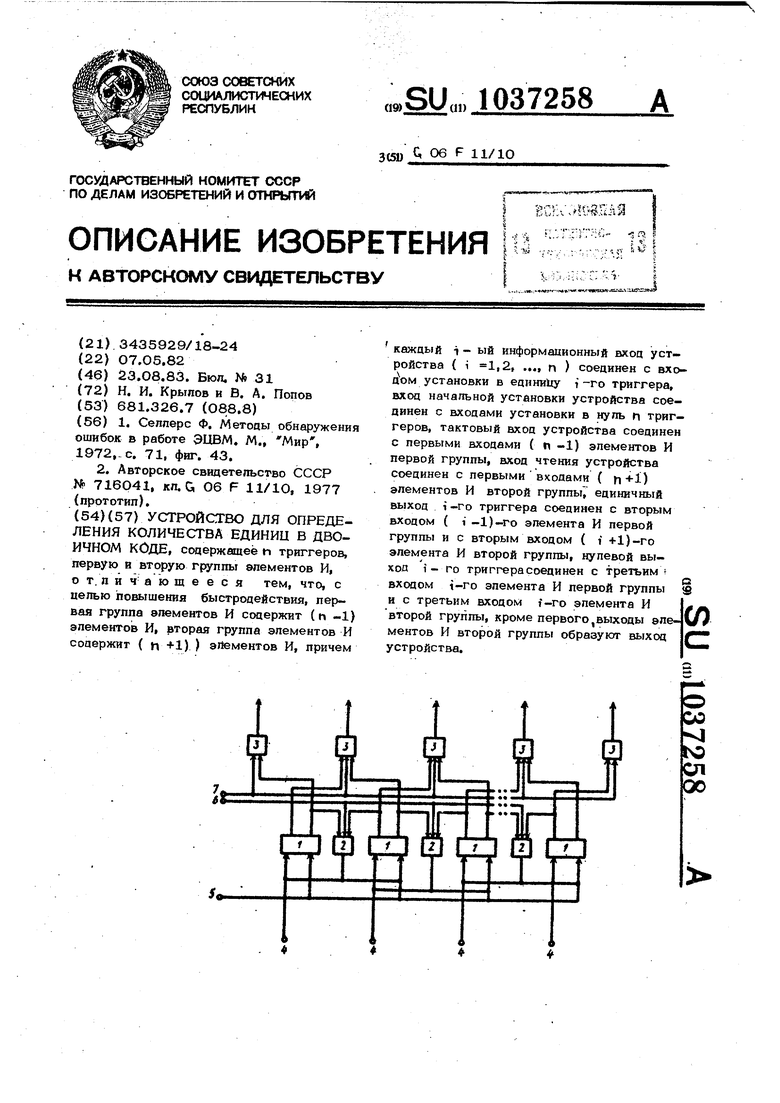

{ Изобретение относится к вычиспвтепь ной технике и может быть применено в устройствах контроля дискретных эпементов. Известно устройство для определения . четности двоичного чиспа, содержшцее триггер и элементы И и ИЛИ дпя каждого из п разрядов 11 3 . Недостатками этого устройства яв пяется сложность и ограниченные функциональные возможности, не поавопяищие указывать точное число значащих разрядов, . числа. Наибопее близким к изобретению по технической сущности является устройство для определения количества единиц в двоичном числе, содержащее триггер и элементы И и ИЛИ для каждого из разрядов, счетчик, трехвходоёой элемент И, элемент И-НЕ я выходной элемент И, причем единичный выход триггера i -го разряда подключен к первому входу элемента ИЛИ i -го разряда ( i 1,2,,.., h ) выход которого соединен с первыми входами первого и второго элементов И ( i+1)-го разряда, вторые входы которых соответственно являются входами уст ройства прямого и инверсного сигналов ( i .+ 1)-го разряд числа, а выходы под ключещ соответственно к информацконному входу триггера ( i +1)-го разряда и второму входу элемента ИЛИ ( i )го разряда, выход элемента ИЛИ п -го разряда соединен с первыми входами элемента И-НЕ и выходного элемента И, вторые входы которых подключены к первому входу трехвходового элемента И, соединенного вторым и третьим входами соответственно с выходом элемента И-НЕ и входом тактовых импульсов устройства, а первым входом - с первыми входами первого и второго элементов И первого разряда и управляющим входом устройства, выход трехвходового элемента И подключен к входу счетчика и синхрониаи- 45 рующим входам триггеров, счетчика и выходного элемента ИЗьляются соответственно информационным и управляющим выходами устройства f 2 . Недостаток), известного устройства 50 в низком быстродействии. Целью изобретения является повышение быстродействия. Поставленная цепь достигается тем, НТО в устройстве цпя определения копи- 55 чества единиц в двончном коде, содержащем п триггеров, первую и вторую группы элементов И, первая группа эпементов И содержит ( -П -1) элементов И, вторая группа элементов И содержит( h +1) элементов И, причем каждый i -ый информационный вход устройства ( i 1(2, . . . , п ) соединен с входом установки в единицу i -го триггера, вхоц начальной установки устройства соединен с входами установки в ноль п триггеров, тактовый вход устройства соединен с пер- выми входами ( п -1) элементов И первой группы, вход чтения устройства соединен с первыми входами ( h +1) элементов И второй группы, единичный выход j -го триггера соединен со вторым входом ( i -1)-го элемента И первой группы и с вторым входом ( i + 1)-го элемента И второй группы, нулевой выход i -го триггера соединен с третьим входом i -го элемента И первой группы и с третьим входом i-ro элемента И второй группы,кроме первого, выхоаы элементов И второй группы образуют выход устройства. На чертеже показана блок-схема предлагаемого устройства. Устройство содержит триггеры 1, первую 2 и вторую 3 группы элементов И, информационные входы 4 устройства, вход 5 начальной установки устройства. тактовый 6 устройства, вход 7 чтения, выходы устройства, Устройство работает спедукадим образом. В исходном состоянии все триггеры находятся в нулевом состоянии. На входы 4 подается прямой код анализируемого двоичного числа. Пусть на входы 4 устройства поступает семиразрядный код двоичного числа О100110. После записи кода в триггеры 1 на вход 6 подается управляющий единичный сигнал, длительность которого определяется временем переходных процессов в устройстве. На выходах первого и четвертого элементов И 2 появляются единичные сигналы, которые устанавливают первые и четвертые триггеры 1 в единичное состояние, а вторые и пятые в нулевое состояние. После переброса триггеров 1 в указанные состояния на выходах 3-го. и 5-го элементов И 2 появляются единичные сигналы, которые устанавливают третий и ПЯТЫЙ триггеры 1 в единичное состояние, а четвертый и шестой - в нулевое состояние. Новое состояние триггеров 1 приведет к появ-. пению на выходах второго и четвертого э; 1ементов И 2 единичных сигналов, которые устанавливают второй и четвертый триггеры 1 в единичное состояние, а третий и пятый - в нулевое состояние. После avvTf) появляется на выходе третье го элемента И 2 единичный сигнал, который устанавливает третий триггер 1 в еаиничное состояние, а четвертый в ну,левое состояние. На этом переходные проиесры в устройстве заканчиваются. На вход 7 подается сигнал -для выдачи результата. Только на выходе четвертого элемента И 3 появляется единичный сигнал, так как на его все три входа подаются единичные сигналы: с единичного выхода третьего триггера 1, с управляющего входа Тис нулевого выхода четвертого триггера 1. Появление единичного сигнала на выхо де четвертого элемента И 3 означает, что в анализируемом двоичном коде - три единицы. В общем сдучае, если в анапиаируемом двоичном коде т, то сигнал появится на ( In +1)-ом выходе. При поступления на вход 5 импульса сброса уст1084 ройство возвращается в исходное состояние. Таким образом, предлагаемое устройство обеспечивает подсчет количества зна-, чащих разрядов двоичного кода за время, равное длительности переходных процессов в устройстве {параллельнопоследовательное переключение триггеров значительно меньше времени, аатрачива емого известным устройством, в котором подсчет количества единиц в двоичном коде осуществляется за число тактов рав ное числу единиц. Использование известного ycipojtcTaa в системах контроля и управления для выработки различных управляющих сигн&. лов в зависимости от количества единиц . в анализируемом двоичном коде предполагает обязательное наличие дешифратора. Применение предлагаемого устройства в аналогичных ситемах исключает необходимость использования дешифратора, так как результат анализа двоичного кода представляется уже в аешифрованном виде.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для сравнения числа единиц в двоичных кодах | 1983 |

|

SU1121669A1 |

| Устройство для преобразования двоичного кода по модулю К | 1987 |

|

SU1587641A1 |

| Устройство для определения количества единиц в двоичном числе | 1988 |

|

SU1547072A2 |

| Преобразователь двоичного кода в число-импульсный код | 1980 |

|

SU943704A1 |

| Устройство для контроля параллельного двоичного кода на четность | 1982 |

|

SU1056199A1 |

| Устройство для определения количества единиц в двоичном коде | 1986 |

|

SU1309029A1 |

| Устройство для преобразования двоичного кода в код по модулю К | 1987 |

|

SU1492479A1 |

| Устройство для контроля параллельного двоичного кода на четность | 1981 |

|

SU999057A1 |

| Устройство для преобразования двоичного кода по модулю К | 1987 |

|

SU1587642A1 |

| Устройство для контроля экспоненциальных процессов | 1987 |

|

SU1500997A1 |

УСТРОЙСТВО ДЛЯ ОПРЕДЕЛЕНИЯ КОЛИЧЕСТВА ЕДИНИЦ В ДВОИЧНОМ КОДЕ, содержащее ti триггеров, первую и вторую группы апементов И, от. пинающееся тем, что, с цепью повышения быстродействия, первая группа элементов И содержит (h -1) эпементо1в И, вторая группа элементов И содержит ( h +1) ) элементов И, причем каждый i - ый информационный вход устройства ( 1 1,2, ..., п ) соединен с входом установки в едини11у i-го триггера, вход начальной установки устройства соединен с входами установки в нуль п триггеров, тактовый вход устройства соединен с первыми входами ( и -1) элементов И первой группы, вход чтения устройства соединен с первыми входами ( элементов И второй группы единичный выход i-ro триггера соединен с вторым входом ( 1 -1)-го элемента И первой группы и с вторым входом ( 1 +1)-го элемента И второй группы, нулевой выход i-ro триггера соединен с третьимi входом t-ro элемента И первой группы и с третьим входом -го элемента И (Л второй группы, кроме первого,выходы элементов И второй группы образуют выход С устройства.

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Селперс Ф | |||

| Методы обнаружения ошибок в работе ЭЦВМ, М., Мир, 1972,-с | |||

| Контрольный стрелочный замок | 1920 |

|

SU71A1 |

| Зубчатое колесо со сменным зубчатым ободом | 1922 |

|

SU43A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Устройство для определения количества едениц в двоичном числе | 1977 |

|

SU716041A1 |

Авторы

Даты

1983-08-23—Публикация

1982-05-07—Подача