;о to vj

3- 1

Изобретение относится к автоматике и вьмислительной технике и может быть испппьзовано в системах передач и переработки информации.

Цель изобретения - повышение быстродействия устройства.

На фиг. 1 приведена блок-схема устройства; на фиг. 2 и 3 - варианты выполнения блока управления; на

фиг. 4 и 5 - варианты выполнения узла подсчета единиц по модулю К.

Устройство содержит (фиг. 1) генератор 1 тактовых импульсов, преобразователь 2 параллельного кода в последовательности импульсов, триггер 3, счетчик 4 по модулю К, узлы 5 подсчета единиц по модулю К, группу 6 элементов ИЛИ, первый и второй элементы ИЛИ 7, 8, элемент И 9 и блок 10 управления. На фиг. 1 обозначены также входы 11, информационные выходы 12 и контрольный выход 13

Преобразователь 2 имеет Р групп информационных входов и Р информа- ционных выходов.

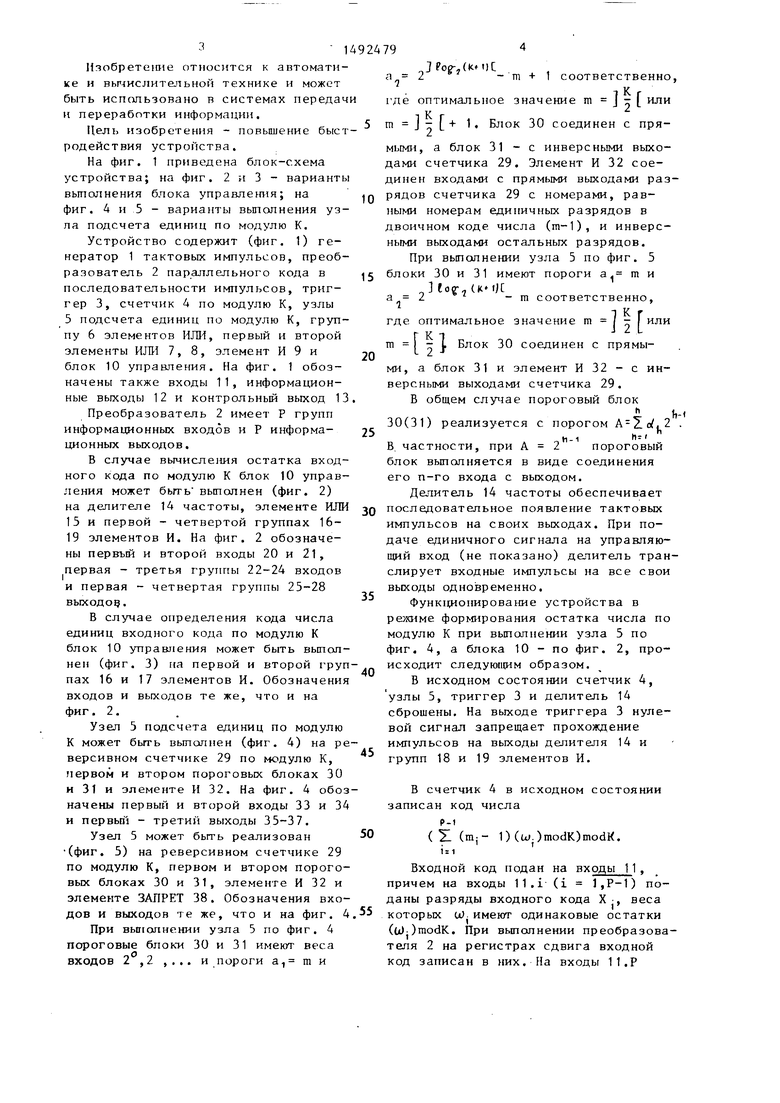

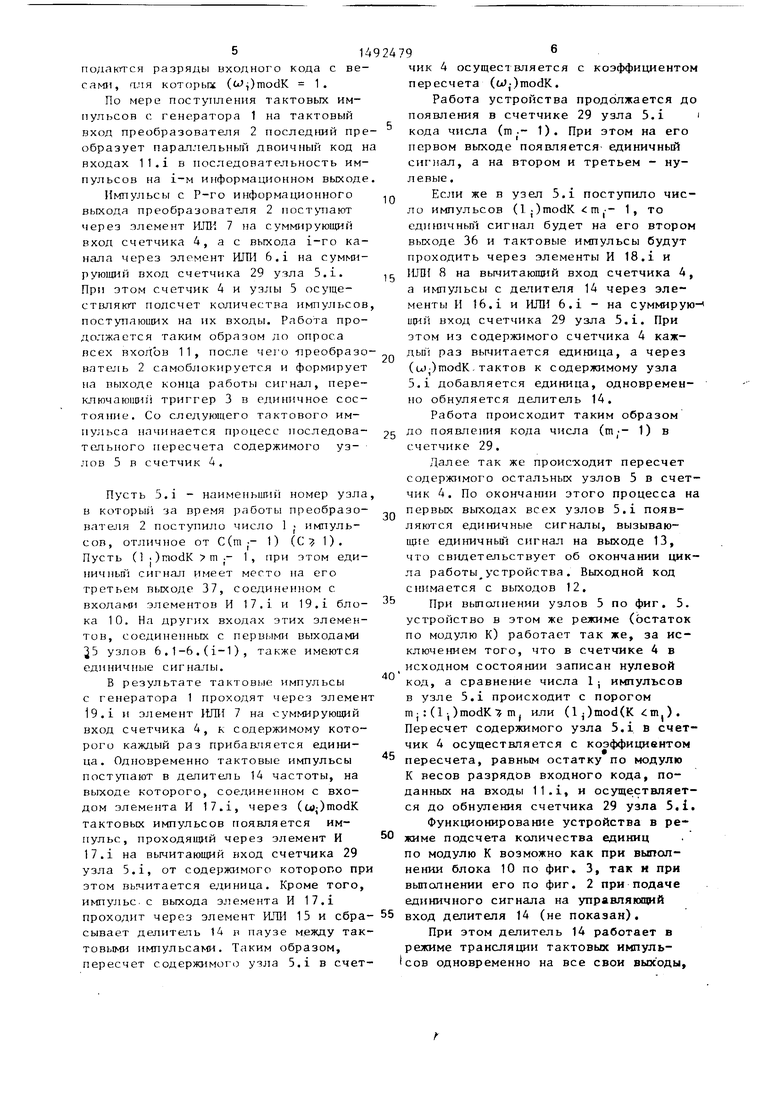

В случае вычисления остатка входного кода по модулю К блок 10 управления может быть выполнен (фиг. 2) на делителе 14 частоты, элементе ИЛИ 15 и первой - четвертой группах 16- 19 элементов И. На фиг. 2 обозначены первый и второй входы 20 и 21, первая - третья rpyintbi 22-24 входов и первая - четвертая группы 25-28 выходец.

В случае определения кода числа единиц входного кода по модулю К блок 10 управления может быть выполнен (фиг. 3) на первой и второй группах 16 и 17 элементов И. Обозначения входов и выходов те же, что и на фиг. 2.

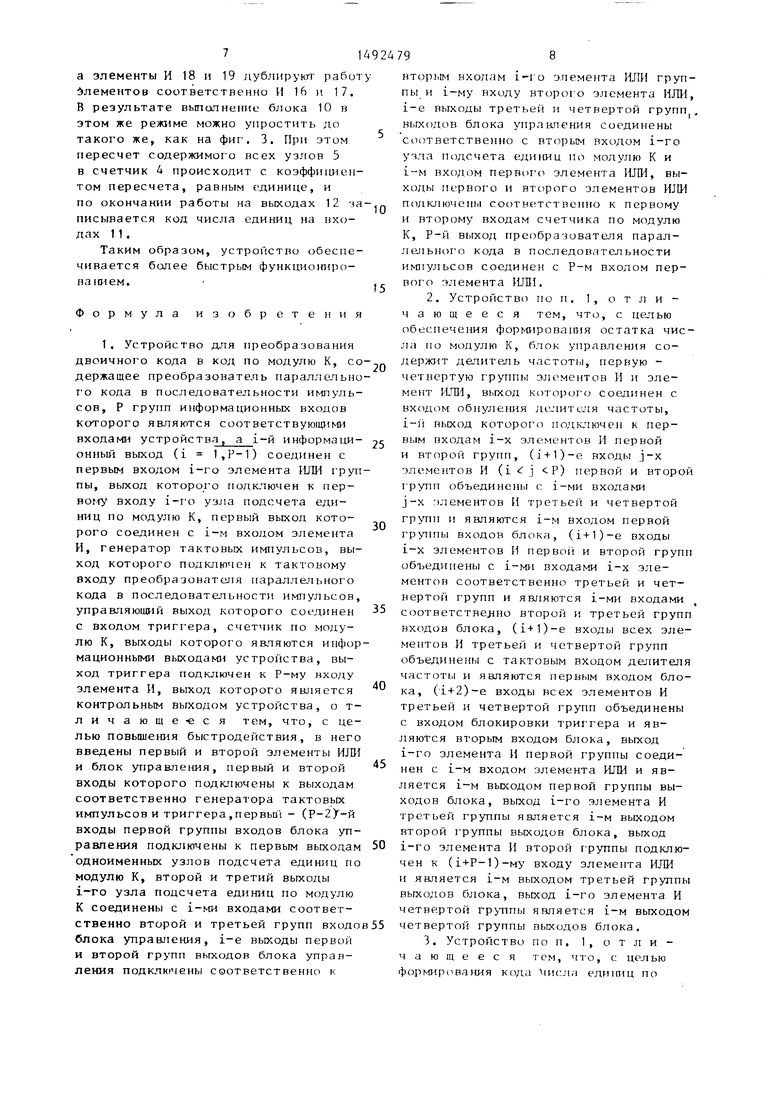

Узел 5 подсчета единиц по модулю К может быть вьтолнен (фиг. 4) на ре

версивном счетчике 29 по 4oдyлю К,

первом и втором пороговых блоках 30 и 31 и элементе И 32. На фиг. 4 обозначены первый и второй входы 33 и 34 и первьп - третий выходы 35-37.

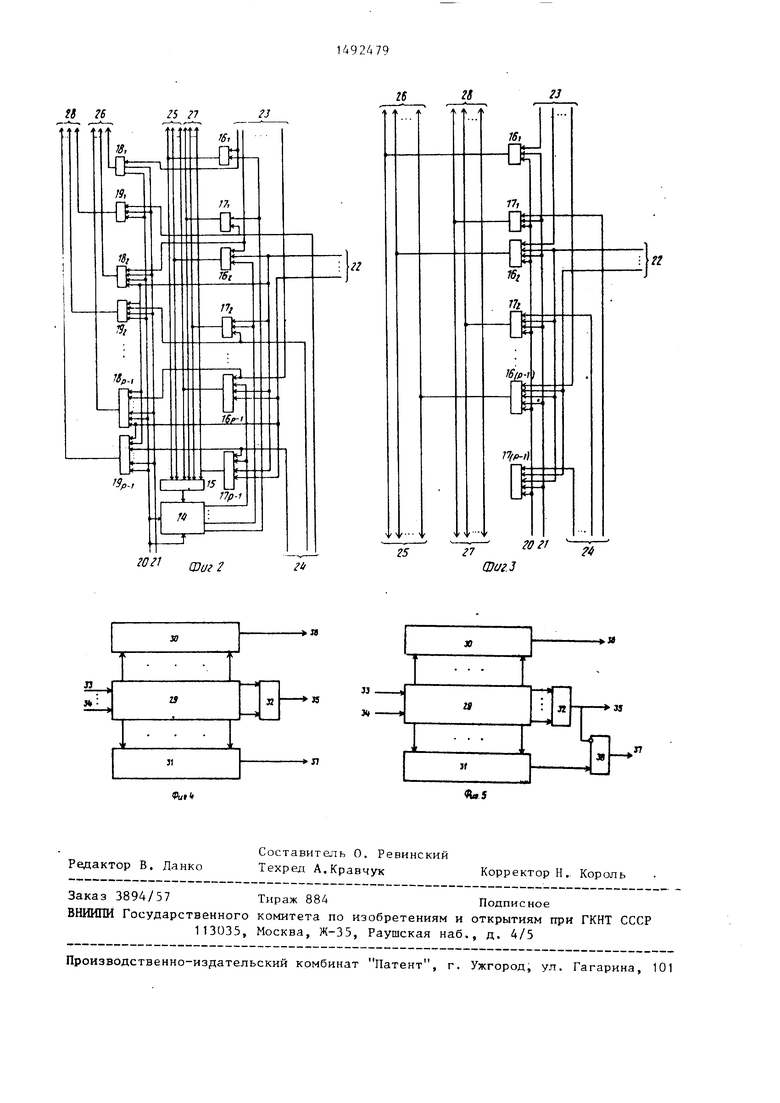

Узел 5 может быть реализован

(фиг. 5) на реверсивном счетчике 29 по модулю К, первом и втором пороговых блоках 30 и 31, элементе И 32 и элементе ЗАПРЕТ 38. Обозначения входов и выходов те же, что и на фиг. 4

При вьпюпнении узла 5 по фиг. 4 пороговые блокх 30 и 31 имеют веса входов 2 ,2 ,... и пороги а m и

794

JPo,(K 4C , а 2 - m + 1 соответственно.

где оптимальное значение m

-

или

к

m

J - + 1, Блок 30 соединен с пря«Q

j П

25

OQ

5

0

5

0

5

мыми, а блок 31 - с инверсными выходами счетчика 29. Элемент И 32 соединен входами с прямыми выходами разрядов счетчика 29 с номерами, рав- 1ыми номерам единичных разрядов в двоичном коде числа (т-1), и инверсными выходами остальных разрядов.

При выполнении узла 5 по фиг. 5 блоки 30 и 31 имеют пороги а m и

eoe-.,(KMK а 2 -т соответственно,

1 К г где оптимальное значение / о f или

К 1-1 L

- Блок 30 соединен с прямыми, а блок 31 и элемент И 32 - с инверсными выходами счетчика 29. В общем случае пороговый блок

h h-( 30(31) реализуется с порогом ,2 .

11-1Иг.

В, частности, при А 2 пороговый блок выполняется в виде соединения его п-го входа с выходом.

Делитель 14 частоты обеспечивает последовательное появление тактовых импульсов на своих выходах. При подаче единичного сигнала на управляющий вход (не показано) делитель транслирует входные импульсы на все свои выходы одновременно.

Функи1ионирование устройства в режиме формирования остатка числа по модулю К при выполнении узла 5 по фиг. 4, а блока 10 - по фиг. 2, происходит следуюпр1м образом.

В исходном состоянии счетчик 4, узлы 5, триггер 3 и делитель 14 сброшены. На выходе триггера 3 нулевой сигнал запрещает прохождение импульсов на выходы делителя 14 и групп 18 и 19 элементов И.

В счетчик 4 в исходном состоянии записан код числа

р-1

(21 (т,-- 1)(w.)modK)modK. in

Входной код подан на входы 11, причем на входы 11.1 (i ,Р-1) поданы разряды входного кода X , веса которых со имеют одинаковые остатки (u)-)niodK. При выполнении преобразователя 2 на регистрах сдвига входной код записан в них. На входы 11.Р

5U

подаются разряды входного кода с весами, аля которых (cJ)modK 1.

По мере поступления тактовых импульсов с генератора 1 на тактовый вход преобразователя 2 последний преобразует параллельный двоичный код н входах 11,1 в последовательность импульсов на i-M информаднонном выходе

Импульсы с Р-го информационного выхода преобразователя 2 через элемент ИЛИ 7 на суммирующий вход счетчика 4, а с выхода i-ro канала через элемент ИЛИ 6,1 на сум№1- рующий вход счетчика 29 узла 5,1. При этом счетчик 4 и узлы 5 осуществляют подсчет количества импульсов поступающих на их входы. Работа продолжается таким образом до опроса всех входов 11, после чего преобразователь 2 самоблокируется и формирует на выходе конца работы сигнал, пере- ключающи триггер 3 в единичное состояние. Со следующего тактового импульса начинается процесс носледова- тельного пересчета содержимого узлов 5 в счетчик 4,

Пусть 5,1 - наименьш й номер узла в KOTopbiii за время работы преобразо- вателя 2 поступило число 1 j импульсов, отличное от C(mj- 1) (С 1), Пусть (1 .)rTiodK m ;- 1 , при этом единичный сигнал имеет место на его третьем выходе 37, соединенном с входами элементов И 17.1 и 19,1 бло- ка 10. На других входах этих элементов, соединенных с первыш выходами 5 узлов 6,1-6,(1-1), также имеются единичные сигналы,

В результате тактовые импульсы с генератора 1 проходят через элемен 19,1 и элемент ИЛИ 7 на суммирующий вход счетчика 4, к содержимому которого каяудый раз прибашшется единица. Одновременно тактовые импульсы поступают в делитель 14 частоты, на выходе которого, соединенном с входом элемента И 17,1, через (u)modK тактовьк импульсов появляется импульс, проходящий через элемент И 17,1 на вычитающий вход счетчика 29 узла 5,1, от содержимого которого при этом вычитается е,циница. Кроме того, импульс, с выхода элемента И 17,1 проходит через элемент ИЛИ 15 и сбра- сывает делитель 14 п паузе между тактовыми импульсами. Таким образом, пересчет содержимого узла 5,1 в счет

5

4

Q 5

,.

5

0

796

чик 4 осуществляется с коэффициентом пересчета (a);)niodK,

Работа устройства продолжается до появления в счетчике 29 узла 5,1i

кода числа (т-- 1), При этом на его первом выходе появляется единичный сигнал, а на втором и третьем - нулевые ,

Если же в узел 5,1 поступило число импульсов (1 ;)modK m |-- 1, то едит1чньп1 сигнал будет на его втором выходе 36 и тактовые импульсы будут проходить через элементы И 18,1 и ИЛИ 8 на вычитающий вход счетчика А, а импульсы с дапителя 14 через элементы И 16,1 и ИЛИ 6,1 - на суммирую- вход счетчика 29 узла 5,1, При этом из содержимого счетчика 4 каж- дьп раз вычитается единица, а через (ui )modK, тактов к содержимому узла 5,1 добавляется единица, одновременно обнуляется делитель 14,

Работа происходит таким образом до появлеш1я кода числа (т-- 1) в счетчике 29,

Далее так же происходит пересчет содержимого остальных узлов 5 в счетчик 4, По окончании этого процесса на первых выходах всех узлов 5,1 появляются единичные сигналы, вызывающие единичньй сигнал на выходе 13, что свидетельствует об окончании цикла работы устройства, Выходной код снимается с выходов 12,

При выполнении узлов 5 по фиг, 5. устройство в этом же режиме (остаток по модулю к) работает так же, за исключением того, что в счетчике 4 в исходном состоянии записан нулевой код, а сравнение числа 1; импульсов в узле 5,1 происходит с порогом m j : (1 -j )modK 7 m или (1 )mod(K cm. ) , Пересчет содержимого узла 5.1 в счетчик 4 осуществляется с коэффициентом пересчета, равньгм остатку по модулю К весов разрядов входного кода, поданных на входы 11,1, и осуществляется до обнуления счетчика 29 узла 5.1, Функционирование устройства в режиме подсчета количества единиц по модулю К возможно как при выполнении блока 10 по фиг, 3, так н при выполнении его по фиг. 2 при подаче единичного сигнала на упранля101ций вход делителя 14 (не показан).

При этом делитель 14 работает в режиме трансляции тактовых импуль- сов одновременно на все свои выходы.

а элементы И 18 н 19 дублируют работ Элементов соответственно И 16 и 17. В результате выполненне блика 10 в этом же режиме можно упростить до такого же, как на фиг, 3. При этом пересчет содержимого всех узлов 5 в счетчик 4 происходит с коэффициентом пересчета, равным единице, и по окончании работы на выходах 12 записывается код числа единиц на входах 1 1 .

Таким образом, устройство обеспечивается более быстрым функцио1шрс)- ванн ем.

Формула изобретения

1. Устройство для преобразования двоичного кода в код по модулю К, со держащее преобразователь параллельного кода в последовательности импульсов, Р групп информационных входов которого являются соответствующими входами устройства, а i-й информацИ- онный выход (i 1,Р-1) соединен с первым входом i-ro элемента ИЛИ группы, выход которого подключен к пер- Bot-iy входу i-1 o узла подсчета единиц по модулю К, первый выход которого соединен с i-м входом элемента И, генератор тактовых импульсов, ход которого подключен к тактовому входу преобразователя параллельного кода в последовательности импульсов, управляющий выход которого соединен с входом триггера, счетчик по модулю К, выходы которого являются информационными выходами устройства, ВЬЕ- ход триггера подключен к Р-му входу элемента И, выход которого является контрольным выходом устройства, о т- личающе-еся тем, что, с целью повышения быстродействия, в него введены первый и второй элементы ИЛИ и блок управления, первый и второй входы которого подключены к выходам соответственно генератора тактовьгх импульсов и триггера ,nepBbui - (Р-2У-Й входы первой группы входов блока управления подключены к первым выходам одноименных узлов подсчета единиц по модулю К, второй и третий выходы i-ro узла подсчета единиц по модулю К соединены с i-ми входами соответственно второй и третьей групп входо блока управления, i-e выходы первой и второй групп выходов блока управления подключены соответственно к

0

5

, 5 5

0

5

0

45

50

вторым входам i -ro элемента ИЛИ группы и i-му второго элемента ИЛИ, i-e выходы третьей и четвертой групп выходов блока управления соединены соответственно с вторым входом i-ro узла подсчета единиц по модулю К и i-M входом первогчч элемента ИЛИ, выходы первого и второго элементов ИЛИ подключены соотве тственно к первому и второму входам счетчика по модулю К, Р-й в1)Гход преобразователя параллельного кода в последовательности и DIyльcoв соединен с Р-м входом первого элемента ИЛИ.

2.Устройство по п. 1, о т л и - чающееся тем, что, с целью обеспечения форш1роваш1я остатка числа по модулю К, блок управления содержит делитель частоты, первую - четвертую группы элементов И и элемент ИЛИ, выход которого сосщинен с входом обнуления де-штсля частоты, i-й вькод которого подключен к первым входам i-x элементов И первой

и второй групп, (i+1)-e входы j-x элементов И (i « j Р) первой и BTopofi групп объединены с i-ми входами j-x элементов И третьей и четвертой и являются i-M входом первой входов блока, (i+1)-e входы i-x элементов И nepBoii и второй групп объединены с i-ми входами i-x элементен соответственно третьей и четвертой групп и являются i-ми входами cooTBeTCTBejiHo второй и третьей групп входов блока, (i-i-l)-e входы всех элементов И третьей и четвертой групп объединены с тактовым входом делителя частоты и являются первым входом блока, (1+2)-е входы всех элементов И третьей и четвертой групп объединены с входом блокировки триггера и являются вторым входом блока, выход i-ro элемента И первой группы соединен с i-M входом элемента ИЛИ и является i-M выходом первой группы выходов блока, выход i-ro элемента И третьей группы является i-M выходом второй группы выходов блока, выход i-ro элемента И второй группы подключен к (i+P-1)-My входу элемента ИЛИ и является i-M выходом третьей группы выходов блока, выход i-ro элемента И четвертой является i-M выходом четвертой группы выходов блока.

3.Устройство по п. 1, о т л и - чающееся тем, что, с целью формир(1вания кода tnicjia единиц по

модулю к, блок управления содержит первую и вторую группы элементов И, первые входы всех элементов И обеих групп объединены и являются первым входом блока, (i+1)-e входы i-x элементов И обеих групп объединены и являются i-M входом первой группы входов блока, (i+1)-e входы i-x элементов И первой и второй групп являются i-ми входами соответственно второй и третьей групп входов блока, (i+2)- входы всех элементов И обеих групп объединены и являются вторым входом блока, выход i-ro элемента И первой группы является i-м выходом первой и второй групп выходов блока, вькод i-ro элемента И второй группы является i-M выходом третьей и четвертой групп выходов блока.

4. Устройство по п. 1, отличающееся тем, что узел подсчета единиц по модулю К содержит пороговые блоки, элемент И и реверсив- ньп счетчик по модулю К, суммирующий и вычитающий входы которого являются соответственно первым и вторым входами узла, прямые выходы разрядов реверсивного счетчика по модулю К с номерами, равными номерам единичных разрядов в двоичном коде числа т-1 (т - величина порога первого порогового блока), подключены к соответствующим входам первого порогового блока и элемента И, выход которого является первым выходом узла, прямые выходы остальных разрядов реверсивного счетчика по К соединены с соответствующими входами первого порогового блока, инверсные выходы разрядов реверсивного счетчика по моду0

5

0

5

0

5

0

лю К с номерами, равньп и номерам нулевых разрядов в двоичном коде числа т-1, подключены к соответствующим входам элемента И и второго порогового блока с величиной порога

Jfoo-Лкмл: 2- m + 1, инверсные вькоды

остальных разрядов реверсивного чика по модулю К соединены с соответствующими входами второго порогового блока, выход которого и выход первого порогового блока являются соответственно вторым и третьим выходами узла.

5. Устройство по п. 1, отличающееся тем, что узел подсчета единиц по модулю К содержит пороговые блоки, элемент И, элемент ЗАПРЕТ и реверсивный счетчик по модулю К, суммирующий и вычитающий входы которого являются соответственно первым и вторым входами узла, прямые выходы разрядов реверсивного счетчика по модулю К соединены с соответствующими входами первого порогового блока с величиной порога га, инверсные выходы разрядов реверсивного счетчика по модулю К подключены к со-, ответствующим входам второго порогового блока с величиной порога

„Jfott-j

2- га ц входам элемента И,

выход которого соединен с запрещающим входом элемента ЗАПРЕТ и является первым выходом узла, выход первого порогового блока является вторым выходом узла, выход второго порогового блока подключен к разрешакяцему входу элемента ЗАПРЕТ, выход которо го является третьим выходом узла.

26ZS23

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для преобразования двоичного кода по модулю К | 1987 |

|

SU1587641A1 |

| Устройство для преобразования двоичного кода по модулю К | 1987 |

|

SU1587642A1 |

| Устройство для подсчета числа единиц двоичного кода по модулю К | 1986 |

|

SU1427574A1 |

| Устройство для контроля количества единиц двоичного кода по модулю К | 1986 |

|

SU1401461A1 |

| Устройство для подсчета числа единиц двоичного кода | 1987 |

|

SU1569995A1 |

| Устройство для контроля двоичного кода по модулю К | 1990 |

|

SU1737736A1 |

| УСТРОЙСТВО ДЛЯ КОНТРОЛЯ ПАРАЛЛЕЛЬНОГО ДВОИЧНОГО КОДА ПО МОДУЛЮ K | 1991 |

|

RU2020760C1 |

| Устройство для обнаружения ошибок в параллельном коде | 1987 |

|

SU1564733A1 |

| Устройство для контроля количества единиц двоичного кода по модулю К | 1986 |

|

SU1401464A2 |

| Преобразователь двоичного кода в последовательность импульсов | 1983 |

|

SU1277115A1 |

Изобретение относится к автоматике и вычислительной технике. Его использование в системах передачи и переработки информации позволяет повысить быстродействие устройства, которое содержит генератор 1 тактовых импульсов, преобразователь 2 параллельного кода в последовательности импульсов, триггер 3, счетчик 4 по модулю К, узлы 5 подсчета единиц по модулю К, группу элементов ИЛИ 6 и элемент И 9. Благодаря введению элементов ИЛИ 7,8 и блока 10 управления в устройстве повышается скорость функционирования. 4 з.п.ф-лы, 5 ил.

( тиг 2

/

за

.Я

л

zs

- Л

25/7 ° 4

Фиг.з

я

и

м

у

J1

| Устройство для подсчета числа единиц двоичного кода по модулю К | 1986 |

|

SU1438006A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Преобразователь кодов | 1985 |

|

SU1285603A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1989-07-07—Публикация

1987-04-22—Подача