Изобретение относится к вычислительной технике и может быть использовано в системах передачи и обработки дискретной информации.

Цель изобретения - пойьшение быстродействия о

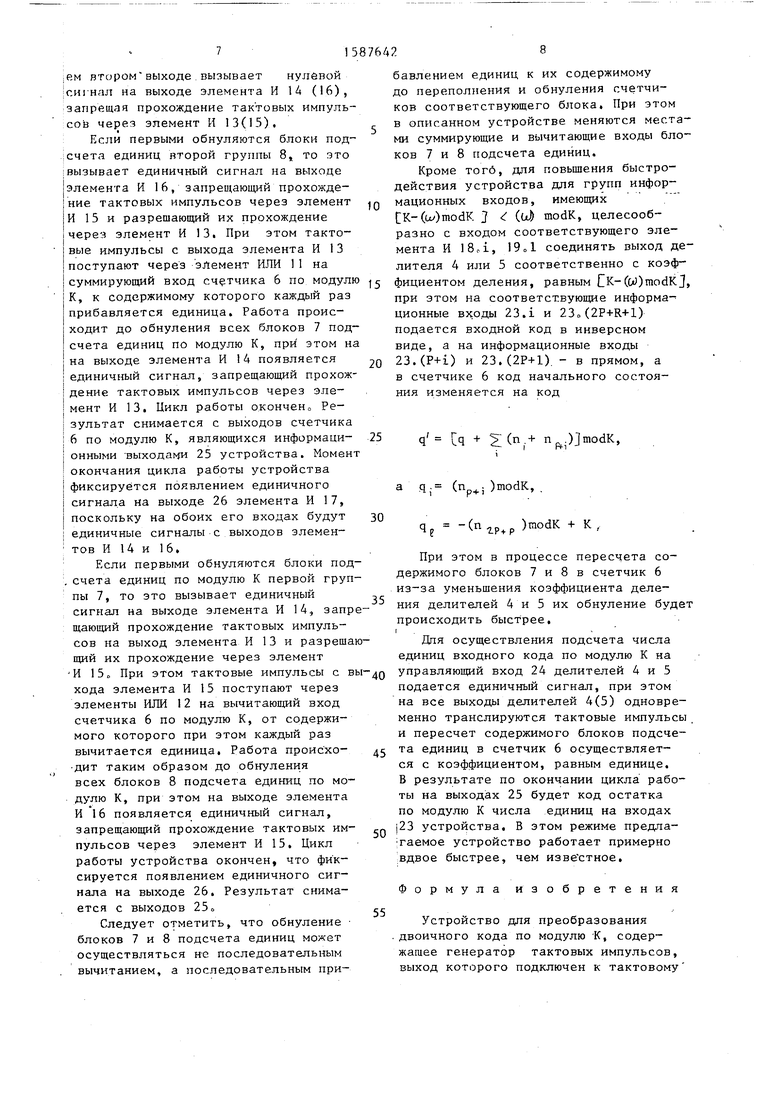

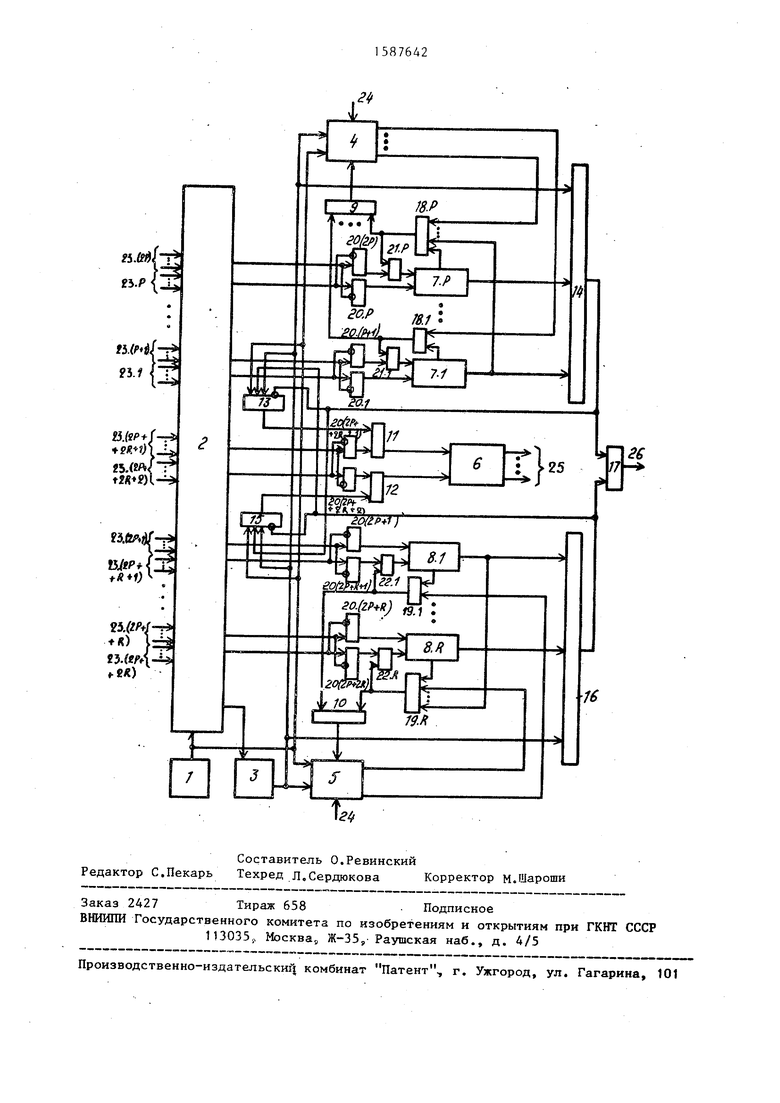

На чертеже приведена функциональная схема устройства.

Устройство содержит генератор 1 тактовых импульсов, многоканальный преобразователь 2 паралелльного кода в последовательности импульсов, триггер 3, первый 4 и второй 5 делители частоты, счетчик 6 по модулю К, первую 7 и вторую 8 группы блоков подсчета единиц по модулю К, первый - четвертый элементы ИЛИ 9-12, первый - пятый элементы И 13 - 17, первую - третью группы элементов И 18 - 20, первую 21 и вторую 22 группы, элементов ИЛИ, информационные входы

23, управляющий вход 24, информационные выходы 25 и выход 26 окончания работ.

Многоканальный преобразователь 2 параллельного кода в последовательность импульсов может быть выполнен как в 2J в виде распределителя импульсов, выходы которого соединены с первыми входами элементов И в С группах (С - число каналов преобразовате- ля 2), вторые входы элементов И каждой группы являются группой входов со- ответствующего канала преобразователя, а выходы соединены с входами элемента ИЛИ, выход которого является выходом канала; преобразователя, тактовый вход распределителя импульсов является тактовым входом преобразователя, а выход последнего разряда рас- пределителя импульсов - выходом конца преобразования.

ел

00

Многоканальный преобразователь параллельного кода в последовательность импульсов может быть выполнен в виде С регистров сдвигаs, соелзянен- ных информационными входами с информационными входами преобразователя, тактовыми входами - с тактовым входом преобразователя, а выходами: перепрямой и инверсный выходы которого я ляются соответственно первым и вторым выходами блока, а суммирующий и вычитающий счетные входы счетчика, являются суммирующим и вычитающим входами блока подсчета единиц по модулю К.В исходном состоянии в счетчик блока записывается код числа

носа с выходами каналов преобразова-|« q. (п) mod К или ,q р(пр) mod К

соответствующей группы 23.(P+i) для

теля, инверсные выходы каждого регистра сдвига соединены с входами своего элемента И, а выходы последних - с входами элемента И, выход которого является выходом корца преобразования,j входы разрешения записи регистров сдвига соединены с входом разращения записи преобразователя.

блоков первой группы 7 или группы 23. (ZP-t-R+l) для блоков второй группы 8 (i 1.Р).

Устройство работает следующим образом,

В исходном состоянии многоканальный преобразователь 2 параллельного кода в последовательность импульсов.

В исходном состоянии многоканаль ный преобразователь 2 параллельного кода в последовательность импульсов

Счетчик 6 по модулю К представляет собой реверсивный счетчик по модулю К 20 триггер 3, счетчик 6 по модулю К, с двумя счетными входами„ Разрядность делители 4 и 5, блоки подсчета еди- счетчика равна t )Co В исходном состоянии в него записан код числа

25 t(

Ч (г.«.„

ниц по модулю к в -группах 7 и 8 сбр шены. При этом в счетчик 6 по модулю К записан код числа

5(P+R)

гСрч-К))

Wjng)mod К,

« ,)

- число входных информационных шин группы 23.(2P- -2R+2);

Пр - число входных информационных шин группы 23Л;

О). - значения остатков весов разрядов входного кода по модулю К, поданных на группу входных информационных

шин 23.1()« При- работе устройства в режиме подсчета количества единиц в счетчик 6 по модулю К записывается код числа

30

35

40

В счетчик блока 7,1 подсчета единиц записан код числа

q. (Пр, ) mod К,

а в счетчик 8.1 блока подсчета единиц - код числа

е ()

На выходе триггера 3 - нулевой сигнал, запрещающий прохождение так вых импульсов на выходе элементов И 13,15 и блокирующий работу делителей 5.

С входами элемента И 18,1 соеди нен выход делителя 4 с коэффициентом деления, равным (w ) modK,где tJ - ве са разрядов входного кода, поданных на группы 23.1 информационных входов, С входами элемента И 9,1 ;соединен выход делителя 5 с коэффициентом деления, равным (w) mod К, где со- веса разрядов входного кода поданных на группы 23.(2Р+1) информационных входов,

WP+R

KP.R.M

np)mod К.

t-1ft

Делитель 4(5) может быть выполнен так же, как в . обеспечивает (в зависимости от сигнала на входе 24 режим подсчета числа единиц и режим формирования остатка

Блок подсчета единиц по модулю К в группах 7 и 8 может быть выполнен, как в .2 , в виде реверсивного двоичного счетчика с двумя счетными входами, прямые выходы разрядов которого соединены с входами элемента ИПИ,

76424

прямой и инверсный выходы которого являются соответственно первым и вторым выходами блока, а суммирующий и вычитающий счетные входы счетчика, являются суммирующим и вычитающим входами блока подсчета единиц по модулю К.В исходном состоянии в счетчик блока записывается код числа

блоков первой группы 7 или группы 23. (ZP-t-R+l) для блоков второй группы 8 (i 1.Р).

Устройство работает следующим образом,

В исходном состоянии многоканальный преобразователь 2 параллельного кода в последовательность импульсов.

триггер 3, счетчик 6 по модулю К, делители 4 и 5, блоки подсчета еди-

триггер 3, счетчик 6 по модулю К, делители 4 и 5, блоки подсчета еди-

ниц по модулю к в -группах 7 и 8 сброшены. При этом в счетчик 6 по модулю К записан код числа

5(P+R)

гСрч-К))

Wjng)mod К,

В счетчик блока 7,1 подсчета единиц записан код числа

q. (Пр, ) mod К,

а в счетчик 8.1 блока подсчета единиц - код числа

е ()

На выходе триггера 3 - нулевой сигнал, запрещающий прохождение тактовых импульсов на выходе элементов И 13,15 и блокирующий работу делителей 5.

С входами элемента И 18,1 соединен выход делителя 4 с коэффициентом деления, равным (w ) modK,где tJ - ве са разрядов входного кода, поданных на группы 23.1 информационных входов, С входами элемента И 9,1 ;соединен выход делителя 5 с коэффициентом деления, равным (w) mod К, где со- веса разрядов входного кода, поданных на группы 23.(2Р+1) информационных входов,

На информационные входы .Р, 23,(2P+R-H) - 23,(2P+2R),23.(2P+2R+1) входной код подан в прямом виде, а на остальные информацийнные входы - в инверсном, либо в прямом, но инвертируется установкой инверторов на входах соответствующих групп входов пре- образ.ователя, либо выполнением входов соответствующих элементов преобразователя инверсными,

При поступлении тактовых импульсов с выхода генератора 1 на тактовый вход многоканального преобразователя 2 последний преобразует количест- )п во единиц входного кода на информационных входах 23.1 - 23.Р, 23.(2Р+ +R+1) - 23.(2P+2R+1) в соответствующее количество импульсов на выходе соответствующего канала преобразователя 15 этом на его первом выходе единичный

зования переключает триггер 3, на в ходе которого появляется единичный сигнал.

Далее происходит процесс последо вательного пересчета содержимого бл ков подсчета единиц каждой из групп 7 и 8 в счетчик 6 по модулю К, прич в обеих группах 7 и 8 процесс пересчета осуществляется одновременно.

Пусть 7.1 (8.1) наименьший номер блока подсчета единиц по модулю К первой (второйj группы, в счетчике которого записан ненулевой код, при

2 и количество нулей входного кода на остальных группах входных информационных шин в соответствующее число импульсов на выходах соответствующего канала преобразователя 2.

Если импульс с выхода многоканального преобразователя 2 поступает на прямой вход только одного из пары элементов И третьей группы 20, то он проходит на выход этого элемента И 20. Если импульсы поступают на прямые входы обоих элементов И 20 в паре, то.импульсы на их выходах не формируются.

Импульсы с выхода элемента И 20-. (2P+2R+1) поступают через элемент ИЛИ 11 на суммирующий вход счетчика 6 по модулю К, к содержимому которого при этом каждый раз прибавляется единица. Импульсы с выхода элемента И 20(2P+2R+2) поступают через элемент ИЛИ 12 на вычитающий вход счетчика 6 по модулю К, от содержимого . которого при этом каждый раз вычитается единица.

Импульсы с выхода элементов И 20.1 или 20.(2Р+1) поступают на суммирующий вход блока 7.1 или 8,1 подсчета единиц по МОДУЛЮ К, к содержимому которого при этом каждый раз прибавляется единица. Импульсы с выхода элемента И 20.(Р+1),или 20,(2P+R+1) поступают через элемент ИЛИ 21.1 или 22.1 на вычитающий вход блока 7.1 или 8Л подсчета единиц по модулю К, от содержимого которого при этом каждый раз вычитается единица. Работа продолжается таким образом до окончания опроса всех информационных входов 23, после чего многоканальный преобразователь 2 самоблокируется и далее сигналов на выходах каналов не формирует, при этом он сигналом с выхода конца преобра20

25

сигнал, поступающий на вход элемент И 18.1 (19.1) на входах которого, с диненных с вторыми выходами биоков 7.1 - 7.(1-1) 8,1 - 8.(1-1), такж имеются единичные сигналы, что разр шает прохождение импульсов с выхода делителя 4 (5) через данный элемент Тактовые импульсы, поступая на такто вый вход делителя 4(5), через (cj)mod импульсов, где и;- веса разрядов вхо ного кода, полученных на группу вход ных информационных шин 23.1, 23.(Р+1 С23.(2Р+1), 23.(2P+R+1) вызывает импульс на выходе делителя 4(5), сое

30 диненном с входом элемента И 18.1(19 который проходит на его выход и через элемент ИЛИ 21,1 (22Л) поступает на вычитающий вход блока 7 (8.1 подсчета единиц по модулю К, от со35 держимого которого при этом каждый раз вычитается единица. Одновременно импульс с выхода элемента И 18.1(19. поступает через элемент ИЛИ 9 (ГО) на вход сброса делителя 4(5), возвра щая его в исходное состояние, таким образом пересчет содержимого блоков 7 и 8 подсчета единиц по модулю К в счетчик 6 по модулю К осуществляется с учетом весов разрядов входного кода. Далее цикл работы повторяется до обнуления блоков 7.1 (8,1),при этом на его первом выходе появляется нулевой сигнал, запрещающий прохож дение импульсов с выхода делителя А(5) на выход элемента И 18.1 (19.1) а на втором выходе - единичный сигнал разрешающий прохождение импульсов на выходы элементов И 18.(1+1) - 18,Р С(19.(1+1) - 19aR.Далее аналогичным образом осуществляется обнуление ос40

45

50

55

тальных блоков 7 и 8 подсчета единиц по модулю К.

Пока хотя бы один ИЗ блоков 7,8 не обнулен, он нулевым сигналом на своI 587642

этом на его первом выходе единичный

зования переключает триггер 3, на выходе которого появляется единичный сигнал.

Далее происходит процесс последовательного пересчета содержимого блв- ков подсчета единиц каждой из групп 7 и 8 в счетчик 6 по модулю К, причем в обеих группах 7 и 8 процесс пересчета осуществляется одновременно.

Пусть 7.1 (8.1) наименьший номер блока подсчета единиц по модулю К первой (второйj группы, в счетчике которого записан ненулевой код, при

20

25

сигнал, поступающий на вход элемента И 18.1 (19.1) на входах которого, соединенных с вторыми выходами биоков 7.1 - 7.(1-1) 8,1 - 8.(1-1), также имеются единичные сигналы, что разрешает прохождение импульсов с выхода делителя 4 (5) через данный элемент И. Тактовые импульсы, поступая на тактовый вход делителя 4(5), через (cj)modK импульсов, где и;- веса разрядов входного кода, полученных на группу входных информационных шин 23.1, 23.(Р+1 С23.(2Р+1), 23.(2P+R+1) вызывает импульс на выходе делителя 4(5), сое30 диненном с входом элемента И 18.1(19.1) который проходит на его выход и через элемент ИЛИ 21,1 (22Л) поступает на вычитающий вход блока 7 (8.1) подсчета единиц по модулю К, от со5 держимого которого при этом каждый раз вычитается единица. Одновременно импульс с выхода элемента И 18.1(19.1) поступает через элемент ИЛИ 9 (ГО) на вход сброса делителя 4(5), возвращая его в исходное состояние, таким образом пересчет содержимого блоков 7 и 8 подсчета единиц по модулю К в счетчик 6 по модулю К осуществляется с учетом весов разрядов входного кода. Далее цикл работы повторяется до обнуления блоков 7.1 (8,1),при этом на его первом выходе появляется нулевой сигнал, запрещающий прохождение импульсов с выхода делителя А(5) на выход элемента И 18.1 (19.1), а на втором выходе - единичный сигнал, разрешающий прохождение импульсов на выходы элементов И 18.(1+1) - 18,Р С(19.(1+1) - 19aR.Далее аналогичным образом осуществляется обнуление ос0

5

0

5

тальных блоков 7 и 8 подсчета единиц по модулю К.

Пока хотя бы один ИЗ блоков 7,8 не обнулен, он нулевым сигналом на своiP.M втором выходе вызывает нулевой ;снгнал на выходе элемента И 14 (16), запрещая прохождение тактовых импульсов через элемент И 13(15),

Если первыми обнуляются блоки под- :счета единиц второй гругты 8, то это Iвызывает единичный сигнал на выходе элемента И 16, запрещающий прохождение тактовых импульсов через элемент И 15 и разрешающий их прохождение через элемент И 13. При этом тактовые импульсы с выхода элемента И 13 поступают через элемент ИЛИ 11 на суммирующий вход счетчика 6 по модул К, к содержимому которого каждый раз прибавляется единица. Работа происходит до обнуления всех блоков 7 подсчета единиц по модулю К, npri этом н на выходе элемента И 14 появляется единичный сигнал, запрещающий прохождение тактовых импульсов через элемент И 13. Цикл работы окончен о Результат снимается с выходов счетчика 6 по модулю К, являющихся информаци- онными -выходами 25 устройства. Момен окончания цикла работы устройства фиксируется появлением единичного сигнала на выходе 26 элемента И 17, поскольку на обоих его входах будут единичные сигналы с выходов элемен- тов И 14 и 16,

Если первыми обнуляются блоки под , счета единиц по модулю К первой груп пы 7, то это вызывает единичный сигнал на выхода элемента И 14., запрщающий прохождение тактовых импульсов на выход элемента И 13 и разрешащий их прохождение через элемент И 15„ При этом тактовые импульсы с В хода элемента И 15 поступают через элементы ИЛИ 12 на вычитающий вход счетчика 6 по модулю К, от содержимого которого при этом каждый раз вычитается единица. Работа происхо- дит таким образом до обнуления всех блоков В подсчета единиц по мо- дулю К, при этом на выходе элемента появляется единичный сигнал, запрещающий прохождение тактовых им- пульсов через элемент И 15. Цикл работы устройства окончен, что фиксируется появлением единичного сигнала на выходе 26. Результат снимается с выходов 25 о

Следует отметить, что обнуление блоков 7 и 8 подсчета единиц может осуществляться не последовательным вычитанием, а последовательным при

бавлением единиц к их содержимому до переполнения и обнуления счетчиков соответствующего блока. При этом в описанном устройстве меняются местами суммирующие и вычитающие входы блоков 7 и 8 подсчета единиц.

Кроме тогб, для повьш1ения быстродействия устройства для групп информационных входов, имеющих {;K-(u)modK 2 ; ((4 modK, целесообразно с входом соответствующего элемента И , 19о1 соединять выход делителя 4 или 5 соответственно с коэффициентом деления, равным ЕК-(Ы)modKJ при этом на соответствующие информационные входы 23.1 и 23o(2P+R+l) подается входной код в инверсном виде, а на информационные входы 23.(Р+г) и 23.(2Р+1). - в прямом, а в счетчике 6 код начального состояния изменяется на код

q q + (n + п )JmodK,

а Я; ( )modK, .

Чр -(гр+р + К

При этом в процессе пересчета содержимого блоков 7 и 8 в счетчик 6 из-за уменьшения коэффициента деления делителей 4 и 5 их обнуление будет

происходить быстрее. I

Дпя осуществления подсчета чис-па

единиц входного кода по модулю К на управляющий вход 24 делителей 4 и 5 подается единичный сигнал, при этом на все выходы делителей 4(5) одновременно транслируются тактовые импульсы , и пересчет содержимого блоков подсчета единиц в счетчик 6 осуществляется с коэффициентом, равным единице. В результате по окончании цикла работы на выходах 25 будет код остатка по модулю К числа единиц на входах |23 устройства. В этом режиме предла- гаемое устройство работает примерно ;вдвое быстрее, чем изве стное.

Формула изобретения

Устройство для преобразования . двоичного кода по модулю К, содержащее генератор тактовых импульсов, выход которого подключен к тактовому

выход i-го элемента ИЛИ первой

входу первого дрлителя частоты, первому прямому входу первого элемента и тактовому входу многоканального преобразователя параллельного кода последовательности импульсов (2Р + + 2R + 2) групп информационных входо которого (Р, R 2)являются одноименными входами устройства, счетчик по модулю К, выходы которого являются и формационными выходами устройства, первая группа блоков подсчета единиц по модулю К, первый выход i-ro блока подсчета единиц по модулю К (i 1,Р) первой группы соединен с первым входом i-ro элемента И первой группы, выход которого подключен к первому входу i-ro элемента ИЛИ первой группы, второй выход i-ro блока подсчета единиц по модулю К соединен с i-M входом второго элемента И и (1+1)-м входом j-ro элемента И (i j Р) первой группы, выход окончания работы многоканального преобразователя параллельного кода в последовательности импульсов подключен к входу триггера, выход которого соединен с вторым прямым входом первого элемента И,(Р+1)-м входом второго элемента И и входом обнуления первог делителя частоты, управляющий вход которого являеФся управляющим входом устройства, выход первого элемента ИЛИ подключен к информационном входу первого делителя частоты, i-й выход которого соединен с (i+l)-M входом i-ro элемента И первой груп

пы,

группы соединен с первым входом i-ro блока подсчета единиц по модулю .К первой группы, выход второго элемента И соединен с инверсным входом первого элемента И, отличающееся тем, что, с целью повышения быстродействия, в устройство вве- дены вторая группа.блоков подсчета- единиц по модулю К, вторая группа элементов ИЛИ, вторая и третья груп- пы элементов И, -третий - пятый эле- менты И, второй - четвертый элементы ИЛИ и второй делитель частоты, управляющий вход которого подключен к управляющему входу устройства, тактовый вход второго делителя частоты объединен с первым прямым входом третьего элемента И и подключен к выходу генератора тактовых импульсов, первый выход 1-го блока подсчета единиц по модулю К (,R) вторсй груп

15

20

25

30

35

40

45

50

55

пы С1. с первым входом 1-го элемент;; И второй группы, выход которого подключен к первому входу 1-го элемента ИЛИ второй группы и 1-му входу второго элемента ИЛИ, выход которого соединен с информационным входом второго делителя частоты, 1-й выход которого подключен к (1+1)-му входу 1-го элемента И второй группы, выход 1-го элемента ИЛИ второй группы подключен к первому входу 1-го блока подсчета единиц по модулю К второй группы, второй выход которого соединен с 1-м входом четвертого элемента И и (1+1)м входом т-го элемента И второй группы (1 т R), вход обнуления второго делителя частоты объединен с вторым прямым входом третьего элемента И и (R+1)-M входом четвертого элемента И и подключен к выходу триггера, третий прямой вход третьего элемента И объединен с первым входом пятого элемента И и подключен к выходу второго элемента И, выход ; четвертого элемента И соединен с третьим прямым входом первого элемента И, инверсным входом третьего элемента И и вторым входом пятого элемента И, выход которого является выходом окончания работы устройства, i-й и CP+i)-й информационные выходь многоканального преобразователя параллельного кода в последовательности импульсов подключены соответственно к прямому входу i-ro и инверсному входу (P+i)-ro элементов И.третьей группы и к инверсному входу i-ro и прямому входу (P+i)-ro элементов И третьей группы, выходы которых соединены с вторыми входами i-x соответственно блока подсчета единиц по модулю К первой группы и элемента ИЖ первой группы, (2Р+1)-й и (2Р+К+1)-й информационные выходы многоканального преобразователя параллельного кода в последовательности импульсов подключены соответственно к прямому входу (2Р+1)-го и инверсному входу (2P+R+l)-ro элементов И третьей группы и к инверсному входу (2Р+1)-го и прямому входу (2P+R+l)-ro элементов И третьей группы, выходы которых соединены с вторыми входами 1-х соответственно блока подсчета единиц по модулю К второй группы и элемента ИЛИ второй группы, (2Р+2Я+1)-й и (2P+2R+2)-й информационные выходы многоканального преобразователя парал-

лельного кода в последовательности импульсов подключены соответственнс к прямому входу (2P+2R+I)-ro и инверсному вхЪду (2P+2R+2)-ro элемен- Tofi И третьей группы и к инверсному входу (2P+2Ri -l )-го и прямому входу (2P+2R- -2)-ro элементов И третьей группы, выходы которых соединены с

первыми входами соответственно третьего и четвертого элементов ИЛИ, выходы первого и третьего элементов И подключены к вторым входам соответственно третьего и четвертого элементов ИЛИ, выходы которых соединены соответственно с суммирующими и вычи- тающими входами счетчика по модулю К.

3///Vf « Ш 3.(

вл)

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для преобразования двоичного кода по модулю К | 1987 |

|

SU1587641A1 |

| Устройство для преобразования двоичного кода в код по модулю К | 1987 |

|

SU1492479A1 |

| Устройство для подсчета числа единиц двоичного кода по модулю К | 1986 |

|

SU1427574A1 |

| Устройство для контроля двоичного кода по модулю К | 1990 |

|

SU1737736A1 |

| Устройство для подсчета числа единиц двоичного кода | 1987 |

|

SU1569995A1 |

| Устройство для подсчета числа единиц двоичного кода по модулю К | 1986 |

|

SU1438006A1 |

| Устройство для контроля количества единиц двоичного кода по модулю К | 1986 |

|

SU1401461A1 |

| Устройство для обнаружения ошибок в параллельном коде | 1987 |

|

SU1564733A1 |

| УСТРОЙСТВО ДЛЯ КОНТРОЛЯ ПАРАЛЛЕЛЬНОГО ДВОИЧНОГО КОДА ПО МОДУЛЮ K | 1991 |

|

RU2020760C1 |

| Пороговое устройство (его варианты) | 1984 |

|

SU1352449A1 |

Изобретение относится к вычислительной технике и при использовании его в системах передачи и обработки дискретной информации позволяет повысить быстродействие. Этот результат достигается благодаря введению в устройство второй группы блоков подсчета единиц по модулю K с соответствующими элементами, второго делителя частоты, а также группы элементов И, в каждой паре которых прямые и инверсные входы включены накрест. Устройство обеспечивает определения остатка входного кода по модулю K и подсчет числа единиц этого кода по модулю K. 1 ил.

| Устройство для преобразования двоичного кода в код по модулю К | 1987 |

|

SU1492479A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1990-08-23—Публикация

1987-12-08—Подача