Изобретение относится к области автоматического диагностирования радиоэлектронной аппаратуры и может быть использовано в системах диагностирования изделий, а также в ЭВМ для проверку функционирования устройств в процессе их работы.

Известно устройство для проверки функционирования БИС, содержащее блок nporpai«5MHoro управления, блок синхронизации, блок формирования, регистры сдвига, элементы И, блок памяти, регистры адреса, регистр цик лов, регистр тактов, регистр синхронизации С13 .

Недостатком данного устройства является значительная сложность, что ограничивает его возможности по использованию в ЭВМ для проверки функционирования узлов в процессе их работы.

Наиболее близким к изобретению по технической сущности является устройство для проверки функционировани многовыкодных цифровых узлов, содержащее генератор тестов,эталонный и проверяемый блоки, блок управления, блоки сравнения, блок пирамидальной свертки по модулю два, сумматор, регистр сдвига, дешифратор испра вьости, дешифратор неисправности и индикатор исправностиС23.

Недостатками известного устройства являются большая сложность и ограниченные возможности по использо.ванию его в ЭВМ для проверки функционирования блоков-в процессе работы так как входными воздействиями для проверяемого блока являются сигналы генератора тестов.

Цель - упрощение.устройства.

Поставленная цель достигается TeM что в устройство для контроля цифровых блоков, содержащее эталонный блок,m элементов сравнения, дешифратор, регистр, причем группа информационных входов проверяемого и эталонного блоков является группой информационных в :одов устройства, m выходов проверяемого блока и первый выход эталонного блока Подключены соответственно к первым и вторым входам m элементов сравнения, введены первая группа из т. элементов И-, вторая группа из 2 элементов И ( )f два счетчика, триггер первый и второй элементы задержки, первый, второй и третий элементы И, .первый и второй элементы ИЛИ, причем выходы m элементов сравнения соеди1нены с первыми входами соответствую.тих m элег.1ентов И первой группы, вто рыб входы КОТОРЫХ связаны с соответсТвующими т выходами дешифратора и m выходами эталонного блока, 6 выходов дешифратора подключены соответственно к Р выходам первого счетчика и к первым входам S эле- .

ментов И второй группы, вторые; входы которых связаны с выходом первого элемента И, первый и второй входы которого соединены соответственно с единичным выходом триггера и выходом первого элемента ИЛИ, нулевой выход триггера соединен с. первыми входами второго и третьего элементов И, второй вход второго элемента И подключен к вы- / ходу второго счетчика и входу второго элемента задержки, выход которого соединен с управляющим входом регистра и первым входом второ го элемента ИЛИ, второй вход которого является входом сброса устройсва и подключен к входам сброса второго счетчика и регистра, выходы регистра являются выходами устройства, выход второго элемента ИЛИ соединен с нулевым входом триггера, единичный вход которого подключен . к выходу первого элемента задержки, вход которого- связан с вторым входом третьего элемента И, выход которого соединен с информационным входом второго счетчика, выходы Р элементов И второй группы связаны с f информационными входами регистра; (е+1)-й вход которого подключен к выходу второго элемента И, выходы m элементов И первой группы соединены с соответствующими входами первого элемента ИЛИ, тактовый вход устройства свяэа.н с входом- первого счетчика.

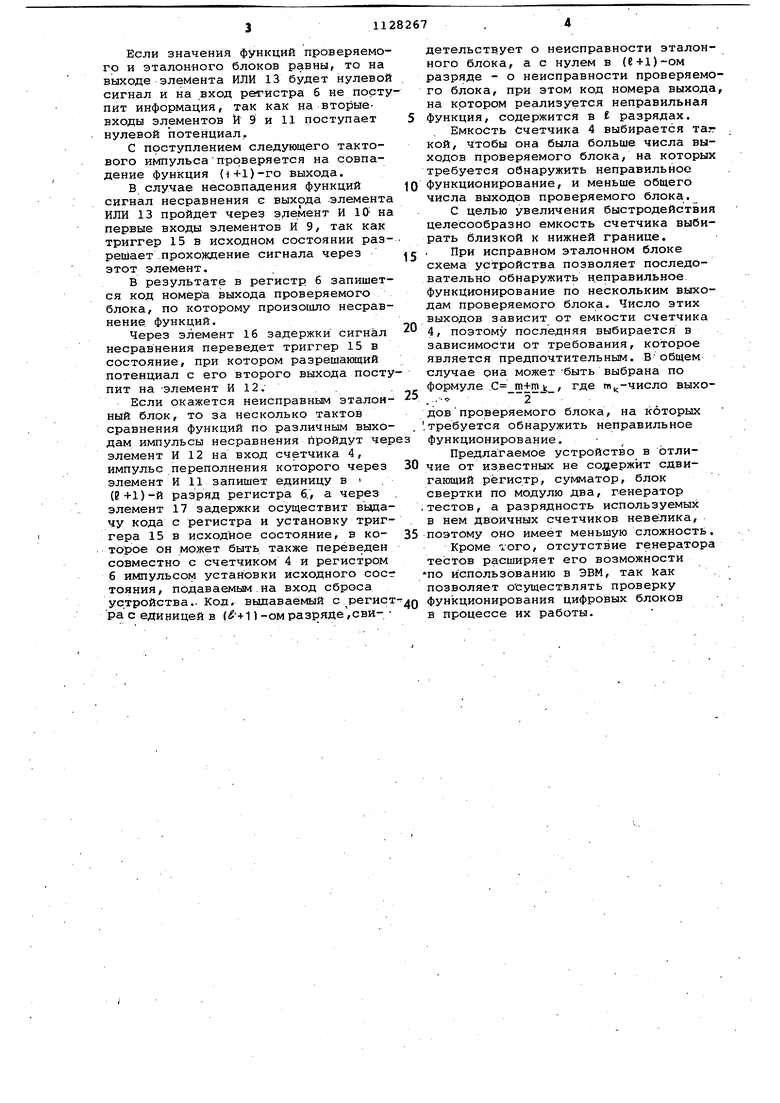

На чертеже представлена функциональная схема предлагаемого устройства.

Устройство содержит проверяемый блок 1, эталонный блок 2, счетчики 3 и 4, дешифратор 5, регистр 6, элементов 7 сравнения, первую группу из m элементов И 8, вторую группу из элементов И 9 ( )/ элементы И 10-12, элементы ИЛИ 13 и 14, Триггер 15 и элементы 16 и 17 задержки.

Многофункциональный эталонный блок 2 реализует последовательно на одном выходе функции каждого выхода проверяемого блока. В простейшем случае многофункциональный эталонны блок может быть выполнен-на основе проверяемого блока с последовательным подключением его выходов на оди общий выход.

Устройство работает следующим образом.

На счетчике .3, число разрядов которого f вырабатывается код номера i-ro выхода проверяемого блока 1,-который поступает на дешифjpaTOp 5. По сигналам дешифратора эталонный блок 2 реализует функцию i-ro выхода проверяемого блока, с которой сравнивается проверяемая функция. Если значения функций проверяемого и эталонного блоков равны, то на выходе элемента ИЛИ 13 будет нулевой сигнал и на вход регистра б не посту пит информация, так как на вторыевходы элементов И 9 и 11 поступает нулевой потенциал. С поступлением следующего тактового импульсапроверяется на совпадение функция (1+1)-го выхода. В случае несовпадения функций сигнал несравнения с выхода элемента ИЛИ 13 пройдет через э-лемент И 10- на первые входы элементов И 9, так как триггер 15 в исходном состоянии разрешает .прохождение сигнала через этот элемент. В результате в регистр. 6 запишется код номера выхода проверяемого блока, по которому произошло несравнение, функций. Через элемент 16 задержки сигнал несравнения переведет триггер 15 в состояние, при котором разрешающий потенциал с его второго выхода посту пит на -элемент И 12. . Если окажется неисправным эталонный блок, то за несколько тактов сравнения функций по различным выходам импульсы несравнения пройдут чер элемент И 12 на вход счетчика 4, импульс переполнения которого через элемент И 11 запишет единицу в (+1)-й разряд регистра 6,, а через элемент 17 задержки осуществит вьвдачу кода с регистра и установку триггера 15 в исходное состояние, в которое он может быть также переведен совместно с счетчиком 4 и регистром 6 импульсом установки исходного сосг тояния, подаваемым.на вход сброса устройства.. Код. выдаваемый с регист ра с единицей в (-И 1 -ом разряде,сви- детельств.ует о неисправности эталонного блока, а с нулем в (8+1)-ом разряде - о неисправности проверяемого блока, при этом код номера выхода, на котором реализуется неправильная функция, содержится в С разрядах. Емкость Счетчика 4 выбирается таг кой, чтобы она была больше числа выходов проверяемого блока, на которых требуется обнаружить неправильное функционирование, и меньше общего числа выходов проверяемого блока. С целью увеличения быстродействия целесообразно емкость счетчика выбирать близкой к нижней границе. При исправном эталонном блоке схема устройства позволяет последовательно обнаружить неправильное функционирование по нескольким выходам проверяемого блока. Число этих выходов зависит от емкости счетчика 4, поэтому последняя выбирается в зависимости от требования, которое является предпочтительным. Вобщем случае она может быть выбрана по формуле С m+m 1; , где т,-число выхо. - 2 довпроверяемого блока, на которых требуется обнаружить неправильное функционирование. Предлагаемое устройство в отличие от известных не содержит сдвигающий регистр, сумматор, блок свертки по модулю два, генератор тестов, а разрядность используемых в нем двоичных счетчиков невелика, поэтому оно имеет меньшую сложность. Кроме voro, отсутствие генератора тестов расширяет его возможности по использованию в ЭВМ, так Как . позволяет осуществлять проверку функционирования цифровых блоков в процессе их работы.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для автоматического поиска дефектов в логических блоках | 1988 |

|

SU1681304A1 |

| Устройство для проверки монтажа | 1987 |

|

SU1509937A1 |

| Устройство для контроля программ | 1983 |

|

SU1149269A1 |

| Устройство для контроля программно-аппаратных средств эвм | 1987 |

|

SU1513454A1 |

| Устройство для контроля логических блоков | 1983 |

|

SU1180904A1 |

| Устройство для обнаружения и локализации неисправностей цифровых блоков | 1982 |

|

SU1067507A1 |

| Устройство для управления реконфигурацией резервированной вычислительной системы | 1991 |

|

SU1837296A1 |

| Устройство для диагностирования логических блоков | 1986 |

|

SU1520518A1 |

| Устройство для поиска дефектов дискретных блоков | 1990 |

|

SU1714610A1 |

| Устройство для контроля и диагностики цифровых блоков | 1985 |

|

SU1278855A1 |

УСТРОЙСТВО ДЛЯ КОНТРОЛЯ ЦИФРОВЫХ БЛОКОВ, содержащее эталонный блок, m элементов сравнения, дешифратор, регистр, причем группа информационных входов проверяемого и эталонного блоков является группой информационных входов устройства; m выходов проверяемого блока и первый выход эталонного блока подключены соответственно к первым и вторым входам m элементов сравнения, отличающееся тем, что, с целью его упрощения, в устройство введены первая группа из «.элементов И, вторая группа из Ч элементов и (е 3 ео hiQ ) , два счетчика, триггер, первый и второй элементы задержки, первый, второй и третий элементы И, первый и второй элементы ИЛИ, причем выходы гп элементов срат нения соединены с первыми входами соответствующих m элементов И первой группы, вторые входы которых связаны с соответствующими m выходамк. дешифратора и т выходами эталонного блока, выходов дешифратора подключены соответственно к Е выходам., первого счетчика и к пер- вым входам I элементов И второй группы, вторые входы которых связа ны;, с выходом первого элемента И, первый и второй входы которого соединены соответственно с единичным выходом триггера и выходом первого элемента ИЛИ, нулевой выход триггера соединен с первыми входами второго и третьего элементов И, второй вход второго элемента И подключен к выходу .торого счетчи-. ка и входу второго элемента задержки, выход которого соединен с управляющим входом регистра и первым входом второго элемента ИЛИ, i второй вход которого является входом сброса устройства и подключен (О С к входам сброса второго счетчика и регистра, выходы регистра являются выходами устройства, выход второго элемента ИЛИ соединен с нулевым входом.триггера, единичный вход которого подключен к выходу первого элемента задержки, вход которого связан с вторым входом третьего элемента И, выход которого соединен с информационным входом второго счетчика, выходы t элементов И второй группы связаны с информационными вхо;.ами регистра (t +1)-й вход которого подключен к .выходу второго элемента И, вы- |. ходы m элементов И первой группы i соединены с соответствующими входами первого элемента ИЛИ, тактовый вход ; устройства связан с входом п.ервого счетчика.

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Устройство для контроля цифровых блоков | 1978 |

|

SU706849A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1984-12-07—Публикация

1983-08-09—Подача