2. Преобразователь по п.1, о тличающийся тем, что формирователь запрещающего сигнала содержит элементы НЕ, И, И-НЕ, ИЛИ-НЕ и элемент задержки, выход которого соединен с первым входом первого эле мента И-НЕ и через первый элемент НЕ - с первым входом второго элемента И-НЕ, выход второго элемента И-НЕ соединен с первым входом элемента ИЛИ-НЕ, выход которого со-, единен с первым входом элемента И, выход элемента И соединен с вы37309

ходом формирователя запрещающего им-. пульса, первый управляющий вход которого подключен к второму входу второго элемента И-НЕ и входам элементов задержки и второго элемента НЕ, выход второго элемента НЕ соединен с вторым входом первого элемента И-НЕ, выход которого соединен с вторым входом элемента ИЛИ-НЕ, второй вход элемента И соединен с вторым управляющим входом формирователя запрещающего импульса.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для сжатия цифровых телевизионных сигналов | 1984 |

|

SU1243159A2 |

| Устройство для сжатия цифрового телевизионного сигнала | 1985 |

|

SU1285626A1 |

| Преобразователь перемещения в код | 1985 |

|

SU1287287A1 |

| Устройство для отладки цифровых систем | 1985 |

|

SU1254492A1 |

| Преобразователь угол-код | 1979 |

|

SU842900A1 |

| Устройство для кодирования телевизионных сигналов | 1986 |

|

SU1356259A1 |

| Устройство для приема сигналов, закодированных с избыточностью | 1988 |

|

SU1605275A2 |

| Преобразователь углового перемещенияВАлА B КОд | 1979 |

|

SU842896A1 |

| Устройство для сжатия цифровых телевизионных сигналов | 1982 |

|

SU1059702A1 |

| Преобразователь кодов | 1985 |

|

SU1259494A1 |

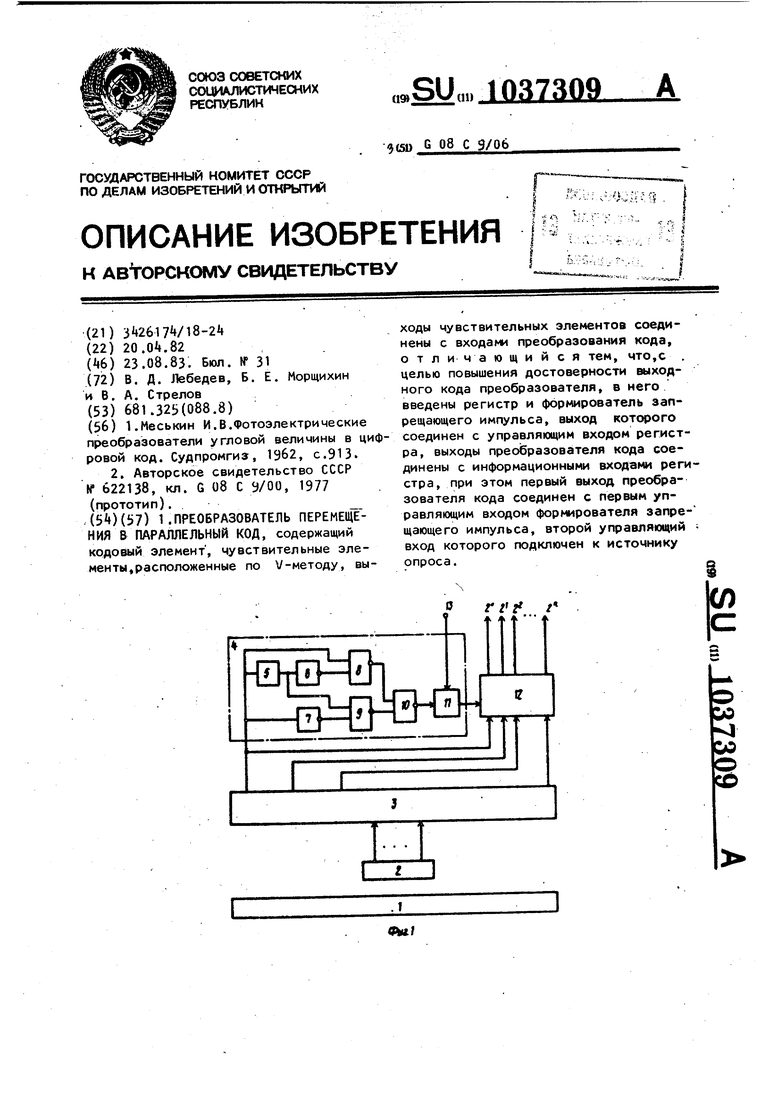

1 .ПРЕОБРАЗОВАТЕЛЬ ПЕРЕМЕЩЕНИЯ В ПАРАЛЛЕЛЬНЫЙ КОД, содержащий кодовый элемент , чувствительные элементы, расположенные по V-методу, выходы чувствительных элементов соединены с входами преобразования кода, отличающийся тем, что,с . целью повышения достоверности выходного кода преобразователя, в него введены регистр и формирователь запрещающего импульса, выход которого соединен с управляющим входом регистра, выходы преобразователя кода соединены с информационными входами регистра, при этом первый выход преобразователя кода соединен с первым управляющим входом формирователя запрещающего импульса, второй управляющий вход которого подключен к источнику опроса. О :л С«9 О со

Изобретение относится к автоматике и вычислительной технике и может быть использовано для связи аналоговых источников информации с цифровыми вычислительными устройствами.

Известен преобразователь перемещения в параллельный код, содержащий кодовый элемент, связанный с объектог перемещения, неподвижно укрепленные чувствительные элементы и преобразователь кодов lj .

Недостигком данного преобразователя является недостаточно высокая достоверность соответствия считываемото кода угловому положению вала вслер ствие .сравнительно большого времени преобразования двоично-сдвинутого кода в лрифметический.

Наиболее близким к изобретению по технической сущности является преобразователь перемещения в параллельный код, содержащий п-разрядный кодовый элемент, чувствительный элемент для первого разряда и по два чувствительных элемента на каждый последующий разряд кодового элемента. Выходы чувствительных элементов всех разрядов подключены к входам преобразователя кода zj .

Недостатком известного преобразователя является недостаточно высокая достоверность выходного кода, так как возможна ситуация считывания ложного кода во время переходных процессов преобразования двоично-сдгзинутого кода в арифмб ический .

Целью изобретения является повышение достоверности выходного кода.

Поставленная цель достигается тем что в преобразователь перемещения в параллельный код, содержащий кодовый элемент, чувствительные элементы, расположенные по V-методу, выходы чувствительных элементов соединены с входами преобразования кода, введены регистр и формирователь запрещающего импульса, выход которого соединен с управляющим входом регистра, выходы преобразователя кода соединены с информационными входами регистра, при этом первый выход преобразователя кода соединен с первым управляющим входом формирователя запрещающего импульса, второй управляющий вход которого подключен к источнику опроса.

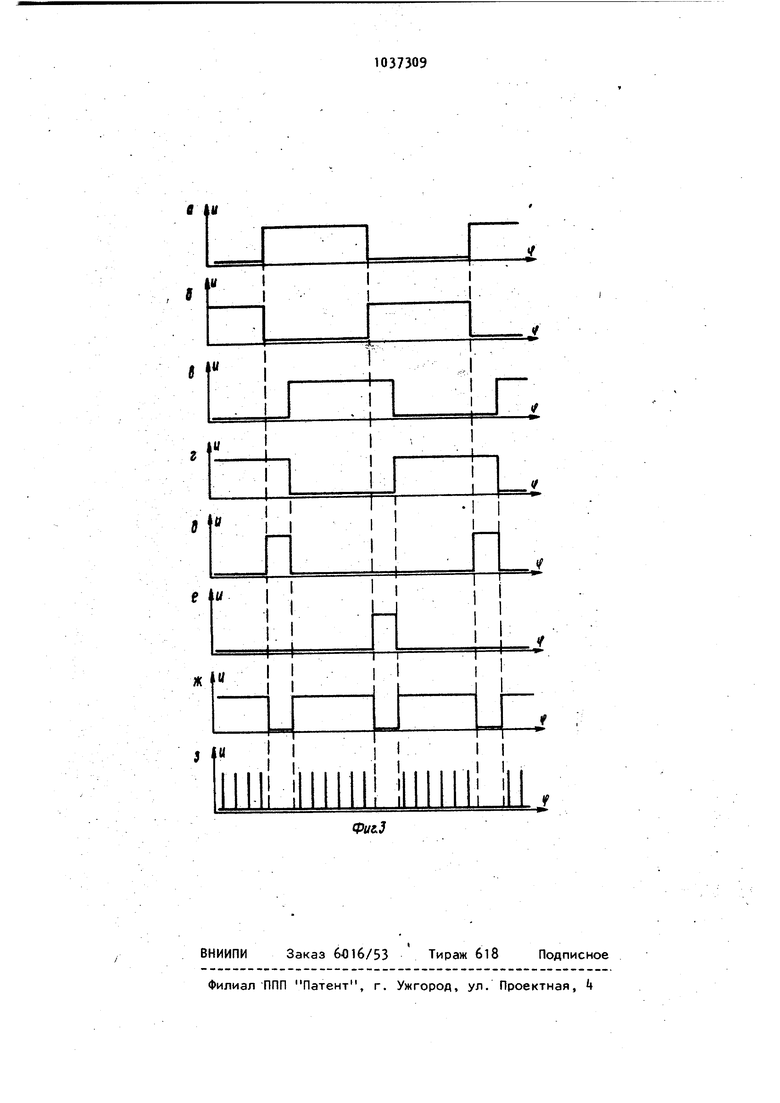

Фop 1poвaтeль запрещающего сигнала содержит элементы НЕ, И, И-НЕ, ИЛИНЕ и элемент задержки, выход которого соединен С первым входом первого элемента И-НЕ и через первый элемент НЕ - с первым входом второго элемента И-НЕ, выход второго элемента И-НЕ соединен с первым входом элемента ИЛИ-НЕ, выход которого соединен с первым входом элемента И, выход .элемента И соединен с выходом формирователя запрещающего импульса, первый управляющий вход которого подключен к второму входу второго элемента И-НЕ и входам элементов .задержки и второго элемента НЕ, выход второго элемента НЕ соедимен с.вторым входом первого элемента И-НЕ, выход которого соединен с вторым входом эл мента ИЛИ-НЕ, второй вход элемента И соединен с вторым управляющим входом формирователя запрещающего импыльса. На фиг. 1 представлена структурная схема преобразования перемещения в параллельный код; на фиг. 2 - эпюры переходных процессов, возникающих на выходе преобразователя кода при смене кода 0111 на 1000; на фиг. 3 диаграммы работы элементов формирователя запрещающего импульса. Преобразователь содержит кодовый элемент 1,чуветвительные элементы 2 расположенные по V-методу считывания, преобразователь 3 кода, формирователь k запрещающего импульса, включающий элемент 5 задержки, элементы НЕ 6 и 7, элемент И-НЕ 8 и 9, элемент ИЛИ-НЕ 10 и элемент И И, регистр 12 и источник 13 опроса. Преобразователь работает следующим образом. При произвольном положении кодового элемента чувствительные элементы 2 считывают информацию,кото рая преобразуется в цифровую форму и поступает на входы преобразователя 3 кода. Для записи выходного кода преобразователя во внешнее устройст во используется формирователь + зап рещающего импульса и регистр 13. На фиг. 2 для примера показан про цесс изменения четырехразрядного ко да 0111 на код 1000. Эпюры на фиг.2 (а,б,в и г) соответствуют изменени JO кода первого, второго, третьего и четвертого разрядов на выходах преобразователя 3 кода. При V-метод считывания преобразователь 3 кода р бот ае таким образом, что каждый последующий разряд начинает преобразование после окончания работы пр дыдущего . Поэтому при изменении кода будет иметь место задержка преобразования кода длительностью tpp. Например, время преобразования кода 0111 в код 1000 будет соответствовать если условно считать что t,- задержки, вызванные временем перехода чувствительного элемента из состояния логического нуля в состояние логической единицы или из логической единицы в логический ноль. Формирователь t запрещающего сигнала с момента любого изменения состояния кода первого разряда формирует импульс запрета записи в регистр 12, длительность которого должна быть больше времени преобразования . Импульс запрета формируется как при изменении состояния кода первого кода первого разряда из О в 1, так и из 1 в О.В первом случае импульс запрета записи формируется элементом И-НЕ 8 (фиг.З д) из сигнала кода первого разряда непосредственно (фиг. За) и сигнала кода первого разряда, задержанного элементом 5 задержки (фиг.З в) и проинвертированного элементом НЕ 6. Во втором случае импульс запрета записи формируется элементом И-НЕ 9 из задержанного элементом 5 задержки си|- нала кода первого разряда и проинвертированного инвертором 7 сигнала кода первого разряда (фиг.З б). Импульсы запрета записи (фиг.З д и е) суммируются элементом ИЛИ-НЕ 10 (фиг.З ж) и поступают на первый вход элемента И IV, запрещая поступление импульсов с выходов преобразователя 3 кода в регистр 12. Длительность импульсов запрета будет определяться . элементом Jj задержки, поэтому ее следует выбирать чуть большей времени преобразования . В результате запись в регистр может произойти только после окончания преобразования двоично-сдвинутого кода в арифметический и запись ложных значений кода, появляющихся в переходные режимы после изменения кода на выходах чувствительных эле ментов, будет исключена. Ошибка преобразования при этом не будет превышать единицы младшего разряда.. Экономический эффект от использования предлагаемогопреобразователя определяется его техническими преимуществами,.

и,

Фиг.2

Авторы

Даты

1983-08-23—Публикация

1982-04-20—Подача