2, Устройство по п. 1, отличаю ш в е с я тем, что блок форг-шрованпя коррекции содержит два сумматора, буферный регистр, два триггера, причем первый и второй входы блока формирования коррекнии соединены соответственно с первой и вторбй группой входов первого сумматора, выход которого соединен с входом второго cyivOvsaTopa, выход которого соединен с входом буферного регистра, выход которого является выходом блока формирования коррекции, выходы переноса, первого и второго сумматоров соединены соответственно с первыми входами пераого и второго триггеров, выходы котоjDbjK соединены соответственно с входами переноса первого и второго сумматоров, третий вход блока формирования коррекции соединен с первым входом разрешения приема информации первого сумматора и входом разретцения Л1риема информации первого триггера, четвертый вход блока формирования коррекции соединен с вторым входом разрешения приема информации первого сумматора и входом разрешения приема информации второго триггера, пятый вход блока формирования коррекциц соединен с входом разрешения приема информации буферного регистра, вторыми входалл первого и второго триггеров.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для умножения | 1982 |

|

SU1038937A1 |

| Устройство для умножения | 1981 |

|

SU1035601A2 |

| Устройство для умножения | 1982 |

|

SU1022156A2 |

| Устройство для умножения | 1981 |

|

SU1032453A1 |

| Множительное устройство | 1982 |

|

SU1053104A1 |

| Устройство для умножения @ -разрядных чисел | 1981 |

|

SU1022155A1 |

| Устройство для умножения п-разрядных чисел | 1981 |

|

SU985783A1 |

| Устройство для умножения | 1987 |

|

SU1495785A1 |

| Вычислительное устройство | 1988 |

|

SU1545215A1 |

| Устройство для умножения | 1982 |

|

SU1137463A1 |

1. УСТРОЙСТВО ДЛЯ УМНОЖЕНИЯ по авт. св. № 888109, отличающееся тем, что, с целью расширения фунииональных возможностей за счет обеспечения умножения чисел в дополнительном коде,оно содержит hразрядный сумматор и блок формирования коррекции, причем первый, второй, третий, четвертый и пягый входы блока формирования коррекции соединены соответственно с входами множителя, множимого, знака множителя, знака множимого и режима работы устройства, выход блока формирования коррекции соединен с четвертым входом последнего блока вычисления разрядных значений произведения выход блока формирования коррекции и выходы буферных регистров, за исключением перво.го буферного регистра второй группы соединены с соответствующими входами h-раэf рядкого сумматора. € сл с со оо со со 05

Изобретение относится к вычислительной технике и может использовано при разработке бьгстродейсгв 1ощих усгройсгв дпя умножения чисел, представленных в любой позиционной системе счисления в йополнигельном коде. Особенно эффективно его применение при использовании больших интегральных схем, в частности при разработке высокопроизводительных . наращтюаекпых ь.ткропроцессЬров и микропроцессорных систем.

По основному авт. св. № 8881О9 известно устройство для умножения, содержащее регистр множимого, п блоков BbiiRic ления разряд:-1ых значений произведения ( п -число разрядов множимого), п буферных регистров первой группы и п буферных регистров второй группы, причем первые входы блоков вычисления разрядтлк значений произведения соединены с выходами соответствующих разрядов регистра множимого, вторые входы - с входом множителя устройства, третьи и четвертые Входы -- с выходами соответствующих

буферньсс регистров первой и второй групп входы буферъЕых регистров первой и второй соединены соответственно с выходами старшего и младшего разряда соот ветвутоших блоков вычисления разрядных значений пpov звeдeш я, выход первого буферного регистра второй группы подкл.ючен к выходу устройсгва, четвертый вход последнего блока вычисления разрядных значений произведения соединен с входом коррекдт устройства (.

Недостатком известного устройства является невозможность перемножения на нем чисел, представленных в дополнительном коде, что снижает область его применения.

Цель изобретения - расширение функциональных возможностей устройства за счет обеспечения умножения чисел в дополнительном коде.

Поставленная цель достигается тем, что устройство для умножения дополнительно содержит п -разрядный сумматор и блок формирования коррекции, причем первый, второй, третий четвертый и пятый входы блока формирования коррекции соединены соответственно с входами множителя, множимого, знака множителя, знака множимого и режима работы устройства, выход блока формирования коррекции соединен с четвертым входом послед- него блока вычисления разрядных значений произведения,, выход блока формирования .коррекции и выходы б}ферных регистров, за исключением первого буферного регистра второй. rpjTtnbi соединены соответствуюшими входами п-разрядными входами п-разрядного сумматора.

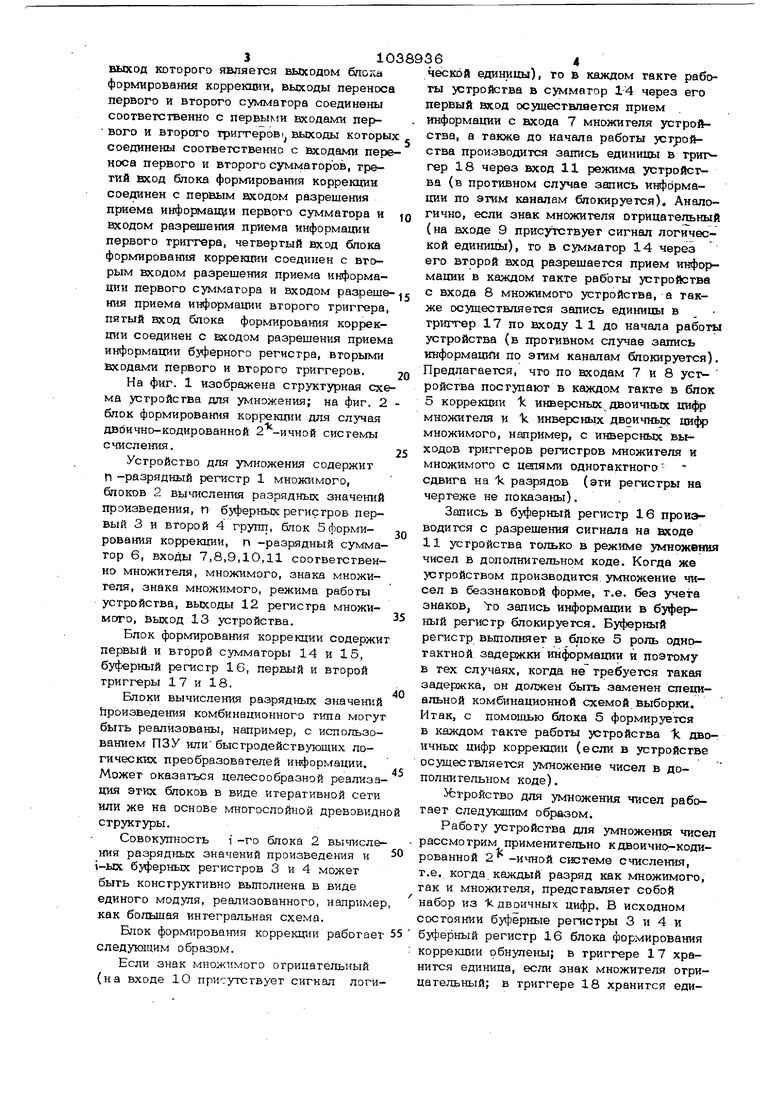

Кроме того, блок формирования коррекции содержит два с;ллматора, б}ферный регистр, два триггера, причем первый и второй входы блока формироватш коррекции соединены соответственно с первой и второй группой входов первого сумматора, выход которого соединен с входом второго сумматора,чвыход которого соединен с входом буферного регистра. ыыход которого является выходом 6noica формирования коррекции, выходы переноса первого и второго сумматора соединены соответственно с первыми входами первого и второго триггеров 1 выходы которы соединены соответственно с входами пере носа первого и второго сумматоров, третий вход блока формирования коррекции соединен с первым входом разрешения приема информации первого сумматора и входом разрешения приема информации первого триггера, четвертый вход блока формирования коррекции соединен с вторым входом разрешения приема информации первого сумматора и входом разреше ния приема И14|ормации второго триггера, пятый вход блока формирования коррекции соединен с входом разрешения прием информации буферного регистра, вторыми входами первого и второго триггеров, На фиг. 1 изображена структурная схе ма устройства для умножения; на фиг. 2 блок формирования коррекции для случая двоично-кодированной 2 -ичной системы счисления. Устройство для умножения содержит П -разрядный регистр 1 множимого, блоков 2 вычисления разрядных значений произведения, п буферных регистров первый 3 и второй 4 групп, блок 5 формирования коррекции, п -разрядный сумматор 6, входы 7,8,9,10,11 соответственно множителя, множимого, знака множителя, знака множим-ого, режима работы устройства, выходы 12 регистра множимого, выход 13 устройства. Блок формирования коррекции содержи первый и второй сумматоры 14 и 15, буферный регистр 16, первый и второй триггеры 17 и 18. Блоки вычисления разрядных значений йроизведения комбинационного типа могут быть реализованы, например, с использованием ПЗУ илибыстродействующих логических преобразователей информации. Может оказаться целесообразной реализа ция этих блоков в виде итеративной сети или же на основе многослойной древовид структуры. Совокупность 1 -го блока 2 вычисле ния разрядных значений произведения и i-ых буферных регистров 3 и 4 может быть конструктивно выполнена в виде единого модуля, реализованного, наприме как большая интегральная схема. Блок формирования коррекции работае следующим образом. Если знак множимого отрицательный (на входе 10 присутствует сигнал логи 10 6 ческой единицы), го в каждом такте работы устройства в сумматор 14 через его ервый вход осушествляется прием информации с входа 7 множителя устройства, а также до начала работы устройства производится запись единицы в триггер 18 через вход 11 режима устройства (в противном случае запись информации по этим каналам блокируется). Аналогично, если знак множителя отрицательный (на входе 9 присутствует сигнал логической единишз), то в сумматор 14 через его второй вход разрешается прием информации в каждом такте работы устройства с входа 8 множимого устройства, а также осуществляется запись единицы в триггер 17 по входу 1 1 до начала работы устройства (в противном случае запись информации по этим каналам блокируется). Предлагается, что по входам 7 и 8 устройства поступают в каждом такте в блок 5 коррекции 1с инверсных двоичных цифр множителя и 1с инверсных двоичных цифр множимого, например, с инверсных выходов триггеров регистров множителя и множимого с цепями однотактного сдвига на k разрядов (эти регистры на чертеже не показаны). Запись в буферный регистр 16 производится с разрешения сигнала на входе 11 устройства только в режиме умножения чисел в дополнительном коде. Когда же устройством производится умножение чисел в беззнаковой форме, т.е. без учета знаков, YO запись информации в буферный регистр блокируется. Буферный регистр вьшолняет в блоке 5 роль однотактной задержки информации и поэтому в тех случаях, когда не требуется такая заде{вкка, он должен быть заменен специальной комбинационной схемой выборки. Итак, с помощью блока 5 формируется в каждом такте работы устройства 1с двоичных ЦИФР коррекции (если в устройстве осуществляется умножение чисел в дополнительном коде). Ьтройство для умножения чисел работает следующим образом. Работу устройства для умножения чисел рассмотрим применительно к двоично-кодированной 2 -ичной системе счисления, т.е. когда каждый разряд как множимого, так и множителя, представляет собой набор из 1 двоичных цифр. В исходном состоянии буферные регистры 3 и 4 и буферный регистр 16 блока формирования коррекции обнулены; в триггере 17 хранится единица, если знак множителя отрицательный; в триггере 18 хранится едиюifflua, если знак кшожимэго огргахагельны в регистре 1 множимого записан п -разряд|ный 2 -ичный код множимого (п k - разрядний двоичтиый код множимого). В 1саждом из п первых тактов работы устройства на его вход 7 поступйег параллельно Ч двоигных разрядов, множите ля, нз raнaя со стороны млад)цих разрядов При этом в -. -ом блоке 2 вычисления разрядных значений произведет осущесгвляегся jTviHDxeHVie разрядо множителя, пост тпакжиих на его второй вход с входа 7 устройства, нн k двоичных, разрядов множимого, лоступакжцих HG его первый вход с выхода 12 i -го 2 --ИЧНОГО разряда регистра 1 множимого и гфибавление к 1 младшим двоичным разрядам попу-тзшег-ося при этом 2 ра рядного произведения через четвертый и третий Входы блока 2 соответственно k мла.цятос. двоичных разрядов произведения ( 1 +1-ГО блока 2, сфоркгированных в предыдущим такте и храниМхЫ.к. в (i +1) -ом буферном регистре 4 и 1с старших двоичных разрядов произведения . -i -го блока 2, с юрктраванных в предыдущем такте и xpaifHMbix в блферном регистре 3. После этого оформироЕ.анные k младшнх двоичных, разрядов произведения i -го блока 2 с его записываются в т -ый регистр 4, а k старших двоичных разртдов произведешгя - в i -ый буферный регистр 3. Одновременно с формированием Б такте работы устройства разрядньос произведегШй в блоках 2 устройства в блоке 5 коррекш-ги форми руется k двоичных ЦИФР корреыпгИ; которые с задер.жкой в один такт подаются на Вход коррекнии устройства. Запись информации в буферные регистры 3 и 4, в буферный регистр 16 к в триггеры 17 и 18 бяока 5 формирования коррекза&ции осуществляется под действием одного и того же cHtocpoHNcnyjibca. Вывод 2 п 2 -ичных разрядов произведения осуществляется через выход устройства для у;,;ножения 13 по 1с двоичг ных разрядов за такт. Ускоренный вывод произведения возможен за п +1 гакт, для чего необходимо в {п+1)-ом гакге осуществить суммирование содержимого буферных регистров 3,4 и 16 (кроме первого буферного регистра 4) на сумжаторе 6. В устройстве для умножения исг1ол,яу ется алгоритм уктожения чисел в дополнительном коде с flByKfsJ явными коррекциями. Следует только огмегигь, что- ес пи знаки множимого и rнoжитeля входят в их старшие 2 -нчтшш цифры, то в качестве коррекгируюших поправок в блоке 5 коррекции используются дополнительные коды множимого и множителя, а знак результата определяется двумя старшими да оичными разрядами наиболее значимой 2 -ичиой цифры произведения. Если же знаки множимого и множителя не являются составной частью из старших 2 ичнь1х цифр (т.е. они не участв тог непосредственно в умножении), то в качептре корректирующих поправок в блоке 5 используются дополнения множимого и множителя, а знак результата должен быть сфор мирован отдельно путем сложения по модулю два знаков сокшожигелей. Технико-экономические преимущества предлагаемого устрбйства в сравнении с известным состоят в расширении его функциональных возможностей за счет обеспечения умножения чисел в дополнительном коде. Кроме того, оно позволяет умножить числа в беззнаковой форме, г,е. без учета знаков, что расширяет область его применения.

bi

jq

w

j

10 9

. i

Фиг.2

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Устройство для подачи костяных пластин в много шпиндельных станках для изготовления пуговиц | 1926 |

|

SU8881A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1983-08-30—Публикация

1982-05-12—Подача