31

; Изобретение относится к радиотех- I нике и может, быть использовано в ка- |честве испол1игельного элемента сие- :тем автоматического регулирования по частоте, фазе или временной задержке, i Целью изобретения является расширение диапазона регулировки фазы.

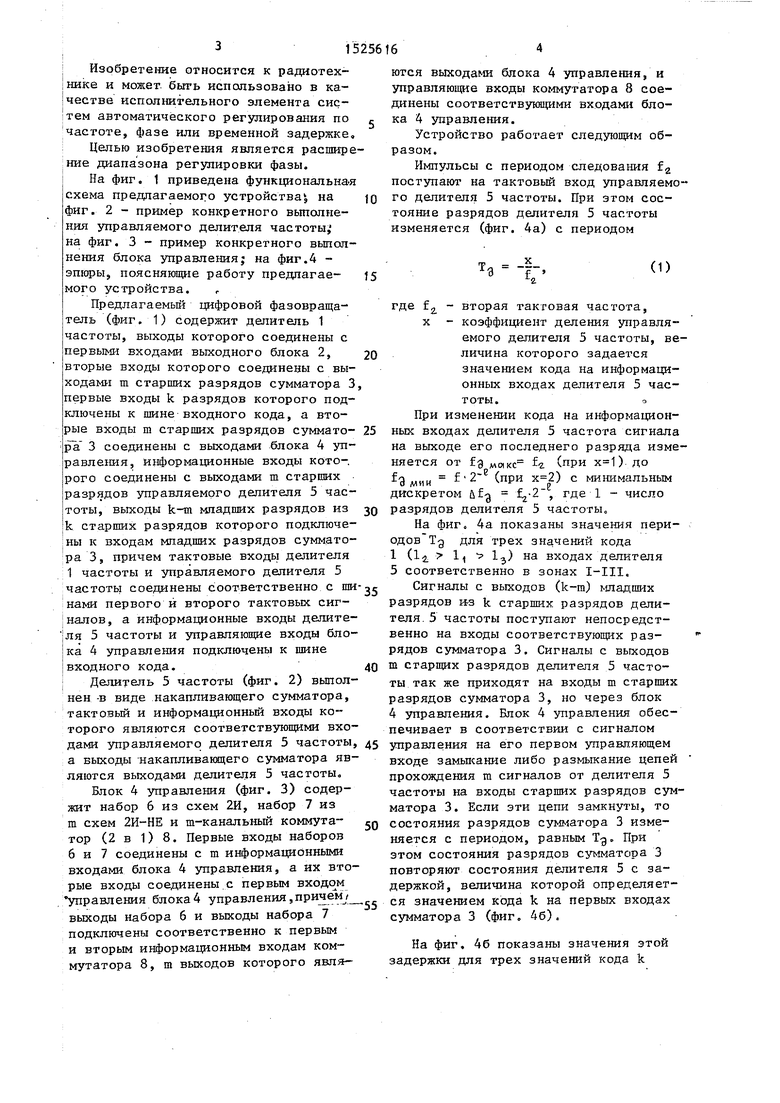

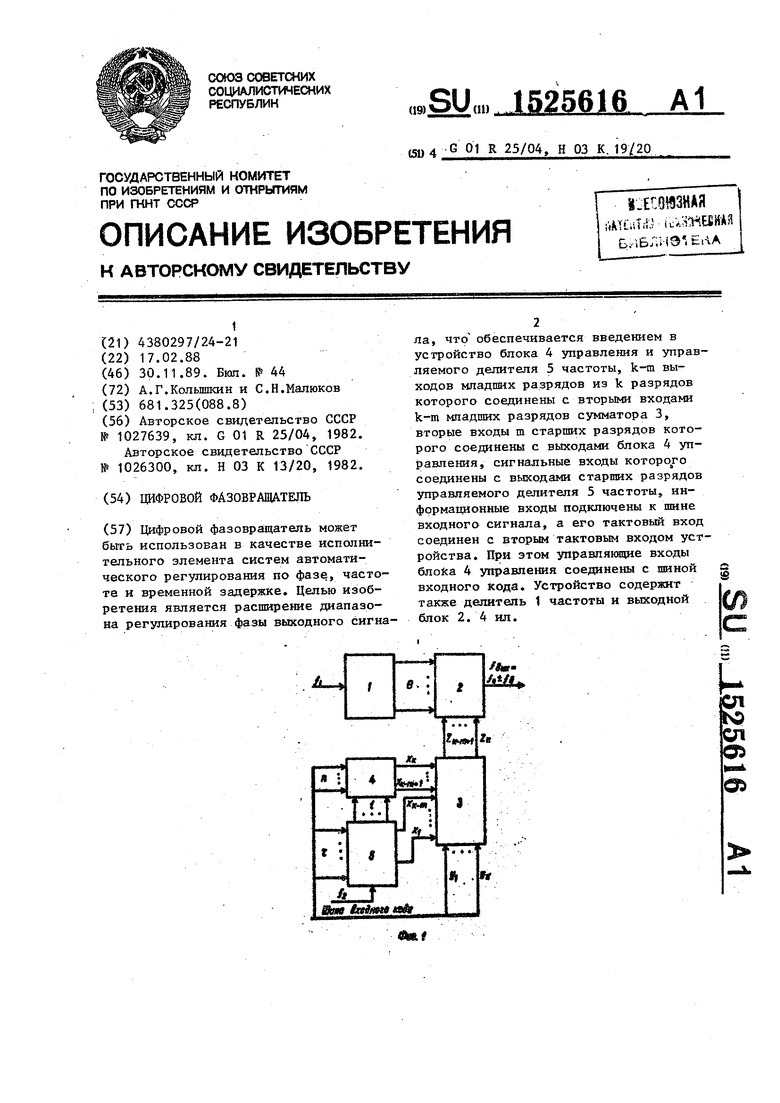

На фиг. 1 приведена функциональная схема предлагаемого устройства , на фиг. 2 - пример конкретного вьтолне- ния управляемого делителя частоты, на фиг. 3 - пример конкретного вьтол- нения блока управления; на фиг.4 - эп1оры, поясняющие работу предпагае- мого устройства.

Предлагаемый цифровой фазовращатель (фиг. 1) содержит делитель 1 частоты, выходы которого соединены с первыми входами выходного блока 2, вторые входы которого соединены с выходами m старших разрядов сумматора 3 первые входы k разрядов которого подключены к шине входного кода, а вторые входы m старших разрядов суммато- pia 3 соединены с выходами блока 4 управления, информационные входы кото-, рого соединены с выходами m старших разрядов управляемого делителя 5 частоты, выходы k-m младших разрядов из k старших разрядов которого подключены к входам младших разрядов сумматора 3, причем тактовые входы делителя 1 частоты и управляемого делителя 5 частоты соединены Соответственно с пм первого и второго тактовых сигналов, а информационные входы делителя 5 частоты и управляющие входы блока 4 управления подключены к шине входного кода.

Делитель 5 частоты (фиг. 2) вьшол- нен -в виде накапливающего сумматора, тактовый и информационный входы которого являются соответствующими входами управляемого делителя 5 частоты а выходы накапливанщего сумматора являются выходами делителя 5 частоты.

Блок 4 управления (фиг. 3) содержит набор 6 из схем 2И, набор 7 из m схем 2И-НЕ и т-канальньй коммута- тор (2 в 1) 8. Первые входы наборов 6 и 7 соединены с m информационными входами блока 4 управления, а их вторые входы соединены.с первым входом управления блока4 управления,причем / выходы набора 6 и выходы набора 7 подключены соответственно к первым и вторым информационным входам коммутатора 8, m выходов которого явля-

16,4

ются выxoдa ш блока 4 управления, и управляю1ще входы коммутатора 8 соединены соответствующими входами блока 4 управления.

Устройство работает следующим образом.

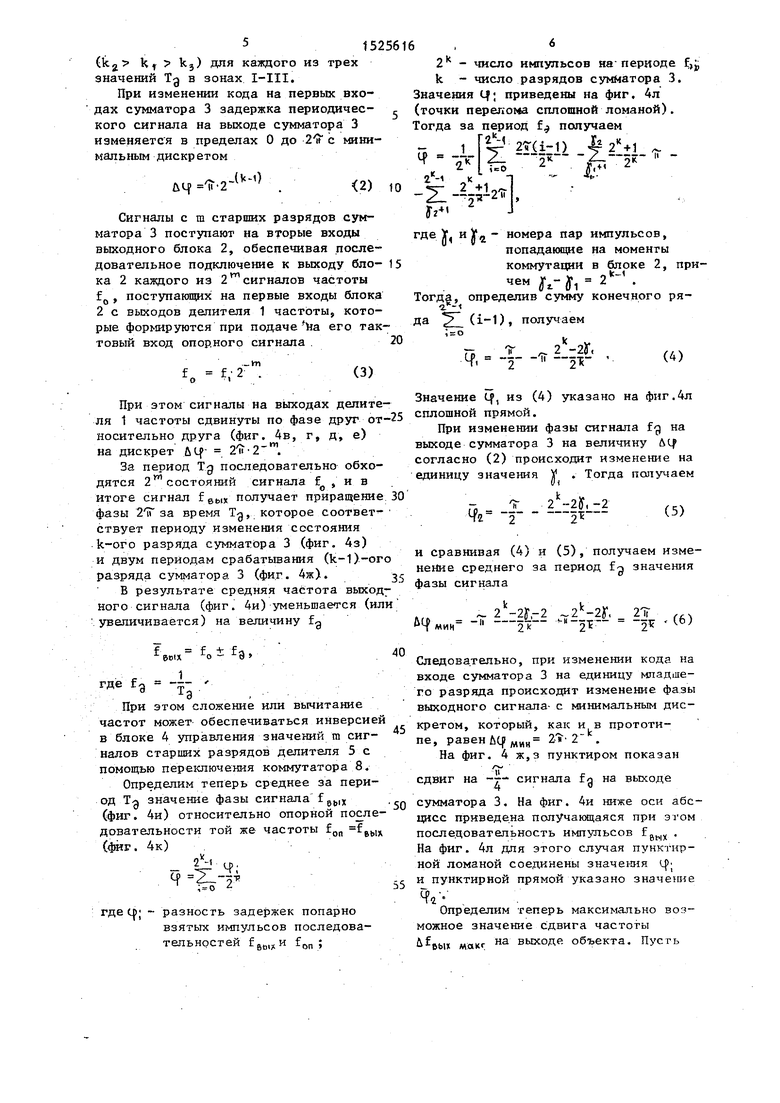

Импульсы с периодом следовагшя fg поступают на тактовый вход управляемго делителя 5 частоты. При этом состояние разрядов делителя 5 частоты изменяется (фиг. 4а) с периодом

гр

АЗ f

(1)

где f, - вторая тактовая частота,

X - коэффициент деления управляемого делителя 5 частоты, величина которого задается значением кода на информационных входах делителя 5 частоты,о При изменении кода на информационных входах делителя 5 частота сигнала на выходе его последнего разряда изменяется от э мо1кс г (при ). до Э wtiH f 2 (при ) с минимальным дискретом uf -2, где 1 - число разрядов делителя 5 частоты.

На фиг. 4а показаны значения периодов Тд для трех значений кода 1 (1-2. 1 1) на входах делителя 5 соответственно в зонах I-III,

Сигналы с выходов (k-m) младших разрядов и-з k старших разрядов делителя. 5 частоты поступают непосредственно на входы соответствующих разрядов сумматора 3. Сигналы с выходов m старщих разрядов делителя 5 частоты так же приходят на входы m старших разрядов сумматора 3, но через блок 4 управления. Блок 4 управления обеспечивает в соответствии с сигналом управления на его первом управляющем входе замьпсание либо размыкание цепей прохождения m сигналов от делителя 5 частоты на входы старших разрядов сумматора 3. Если эти цепи замкнуты, то состояния разрядов сумматора 3 изменяется с периодом, равным Т-д. При этом состояния разрядов сумматора 3 повторяют состояния делителя 5 с задержкой, величина которой определяется значением кода k на первых входах сумматора 3 (фиг. 4б).

На фиг. 4б показаны значения этой задержки для трех значений кода k

51525616

(k ) для казкдого из трех значений Тд в зонах I-III.

При изменении кода на первых входах сумматора 3 задержка периодического сигнала на выходе сумматора 3 изменяется в пределах О до 2 с мини мальным дискретом

,-(VH)

5 (

2) 10

где Y и V - номера пар импульсов, попадающие на моменты коммутации в блоке 2, при

чем -Ji Тогда, определив сумму конечного ря 2Гда (1-1), получаем

tf, -I--.

(4)

Сигналы с ш старпшх разрядов сумматора 3 поступают на вторые входы выходного блока 2, обеспечивая последовательное подключение к выходу бло- 15 ка 2 каждого из 2 сигналов частоты f, поступающих на первые входы блока 2 с выходов делителя 1 частоты, которые формируются при подаче te его тактовый вход опорного сигнала . 20

.т fo f, 2 .(3)

При этом сигналы на выходах делите- Значение Cf, из (4) указано на фиг.4л ля 1 частоты сдвинуты по фазе друг от-25 сплошной прямой.

носительно друга (фиг. 4в, г, д. е) изменении фазы сигнала fg на

на дискрет 2 ii-2 .

За период Тд последовательна обходятся 2 состояний сигнала f , и в итоге сигнал получает приращение 30 фазы 2 ir за время Тд, которое соответ- ствует периоду изменения состояния k-oro разряда сумматора 3 (фиг. 4з) и двум периодам срабатывания (k-1).-oro разряда сумматора 3 (фиг. 4ж).35 среднего за период f значения

В результате средняя частота выходу сигнала

кого сигнала (фиг. 4и) уменьшается (или 1 ,k v ,.. . 2 -2f,-2 2 -2j, 2 It ,,4 Utf „„ -II2 - -2Tf (6)

выходе сумматора 3 на величину Лср согласно (2) происходит изменение на единицу значения У . Тогда получаем

Гр . 2 l2|L:2

Чг 22

(5)

увеличивается) на величину fg

и сравнивая (4) и (5), получаем изме

2 - число импульсов на-периоде f, k - число разрядов сумйатора 3. Значения tf; приведены на фиг, 4л (точки перелома сплошной ломаной). Тогда за период fj получаем

ч

2) 10

где Y и V - номера пар импульсов, попадающие на моменты коммутации в блоке 2, причем -Ji Тогда, определив сумму конечного ря 2Гда (1-1), получаем

tf, -I--.

(4)

Р изменении фазы сигнала fg на

среднего за период f значения

выходе сумматора 3 на величину Лср согласно (2) происходит изменение на единицу значения У . Тогда получаем

Гр . 2 l2|L:2

Чг 22

(5)

среднего за период f значения

и сравнивая (4) и (5), получаем изме

| название | год | авторы | номер документа |

|---|---|---|---|

| Умножитель частоты периодических импульсов | 1980 |

|

SU935956A1 |

| Цифровой фазометр | 1986 |

|

SU1348744A1 |

| Цифроаналоговый преобразователь | 1987 |

|

SU1642585A1 |

| Способ преобразования угла поворота вала в код и устройство для его осуществления | 1988 |

|

SU1647901A1 |

| Делитель частоты с переменным коэффициентом деления | 1988 |

|

SU1677869A2 |

| Умножитель частоты следования периодических импульсов | 1980 |

|

SU980094A1 |

| ГЕНЕРАТОР СИНУСОИДАЛЬНОГО СИГНАЛА | 2014 |

|

RU2568391C1 |

| Умножитель частоты | 1986 |

|

SU1332316A1 |

| Устройство для коррекции шкалы времени | 1987 |

|

SU1432451A2 |

| Цифровой регулятор | 1982 |

|

SU1056130A2 |

Цифровой фазовращатель может быть использован в качестве ииполнительного элемента систем автоматического регулирования по фазе, частоте и временной задержке. Целью изобретения является расширение диапазона регулирования фазы выходного сигнала, что обеспечивается введением в устройство блока 4 управления и управляемого делителя 5 частоты, K-M выходов младших разрядов из K разрядов которого соединены с вторыми входами K-M младших разрядов сумматора 3, вторые входы M старших разрядов которого соединены с выходами блока 4 управления, сигнальные входы которого соединены с выходами старших разрядов управляемого делителя 5 частоты, информационные входы подключены к шине входного сигнала, а его тактовый вход соединен с вторым тактовым входом устройства. При этом управляющие входы блока 4 управления соединены с шиной входного кода. Устройство содержит также делитель 1 частоты и выходной блок 2. 4 ил.

60IX

f

9

где f,, --При этом сложение или вычитание частот может обеспечиваться инверсией в блоке 4 управления значений m сигналов старших разрядов делителя 5 с помощью переключения коммутатора 8.

Определим теперь среднее за период Тд значение фазы сигнала fg. (фиг. 4и) относительно опорной довательности той же частоты f fgt,ix (фиг. 4к)

2-.

-1

где ср - разность задержек попарно

взятых импульсов последовательностей fgo, f on ;

1

Следовательно, при изменении кода на входе сумматора 3 на единицу младшего разряда происходит изменение фазы выходного сигнала- с минимальным дискретом, который, как ив прототипе, равен йС||„„„ 2 «--2 .

На фиг. 4 ж,з пунктиром показан

сдвиг на -г- сигнала fg на выходе

сумматора 3. На фиг. 4и ниже оси абсцисс приведена получающаяся при этом последовательность импульсов f,, . На фиг. 4л для этого случая пунктирной ломаной соединены значения Ц) и пунктирной прямой указано значегте

Ч-,- ,

Определим теперь максимально возможное значение с:двига частоты вык млкг и выходе объекта. Пусть

на входе делителя 1 частота сигнала

i f,,, тогда .

f;2(7)

В соответствии с anroigijTMOM работы предлагаемого усхрейства два различных состояния сигнала на шлходе cytf, матора 3 должны быть разнесены во вре мёни не менее, чем на период частоты f, следовательно период изменения состояния Младшего из m старших разрядов сумматора 3 должен быть не мене двух перирдов частоты fg. В старшем из разрядов сумматора 3 этот период будет в 2 раз больше, а частота сигнала на его выходе будет в этом случае ограничена сверху

f 3 V 2

.tn

(8)

Но в соответствии с алгоритмом работы устройства

Ч .uf

6ЫХ

и тогда, в силу (7) и (8).

МО КС

-т

(9) 30

Сравним if jyb,x MctKc прототипе и в предлагаемом устройстве в одинаковых условиях, т.е. при одинаковых f и fj и при m 2, для k 2,3,4 получа- ем в прототипе

f

--t

-б

.8ЫХ ЛАЯ КС

f, 2 ; fv 2-; f, 2 ° (10)

в предлагаемом устройстве согласно 40 (9)

вы ллокс

const 2

Ч

(11)

Из сравнения (10) и (11) следует, что при k 2 предлагаемое устройство и прототип обеспечивают равные диапазоны управления частотой. Но в этом случае k-2 0, что делает невозможной реализа;цию прототипа, так

как он содержит счетчик 6, для существования которого должно выполняться k 2.,

А для любых k 2 предлагаемое устройство обеспечивает больший диапазон регулировки частоты, чем прототип, причем

2 „.- -2

(12)

Следовательно, по сравнению с прототипом, предлагаемое устройство обеспечивает расширение диапазона регулировки фазы.

Формулаиз обр етения

Цифровой фазовращательj содержащий делитель частоты, тактовый которого подключен к клемме первого тактового входа устройства, а выходы делителя частоты соединены с первыми входами выходного блока, вторые входы которого соединены с m выходами CJTM- матора, k первых входов которого подключены к шине входного кода, причем . выход выходного блока соединен с выходной шиной устройства, о т л и - ч а ю щ и и е я тем, что, с целью расширения диапазона регулирования в него введены блок управления и управляемый -делитель частоты, k-m выходов младших разрядов из k разрядов которого соединены с вторыми входами k-m младших разрядов сумматора, вторые входы m старших разрядов которого соединены с выходами блока управления, сигнальные входы которого соединены с выходами m старших разрядов управляемого делителя частоты, информационные входы которого подключены к шине входного кода, а его тактовый вход подключен к шине второго тактового входа устройства, причем управ- ляю1цие входы блока управления подключены к шине входного кода.

Фиг.З

ё

В

д

е

V-I

I I t Г I I t

I I Г If I HI I Г I 1 I

11 I ll I It t I I I I I

iLL I it i till

e -JLJU

t jyn ll r

t 1 I t Г I

Фиг,

| Устройство для дискретной регулировки фазы | 1982 |

|

SU1027639A1 |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Преобразователь код-фаза | 1982 |

|

SU1026300A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1989-11-30—Публикация

1988-02-17—Подача