2. Устройство по п. 1, о т л ич а. юще е с я тем, что в нем логический блок содержит элементы ИЛИ, преобразователь код - период импульгров, преобразователь код - число импульсов и интеграторы, первый, второй и третий входы первого интегратора соединены с соответствующими входами логического блока, а первый и второй выходы - с соответствующими входами преобразователя код-число импульсов, третий вход которого подключен к четвертому входу логического бЛока, первые входы первого и второго элементов ИЛИ непосредственно и вторые входы через последовательно соединенные преобразователь кодпериод импульсов и второй интегра- тор соединены соответственно с первым и вторым выходами преобразователя код-число импульсов, а выходы первого иiвторого элементов ИЛИ подключены к соответствующим выходам логического блока.

| название | год | авторы | номер документа |

|---|---|---|---|

| Фазометрическое устройство | 1980 |

|

SU918883A1 |

| Аналоговое запоминающее устройство | 1980 |

|

SU875464A1 |

| Преобразователь угловых перемещений в код | 1985 |

|

SU1311024A1 |

| Устройство компенсации сдвига частот | 1985 |

|

SU1316097A2 |

| Интегратор азимутных импульсов | 1977 |

|

SU736123A2 |

| Синхронный самонастраивающийся фильтр | 1979 |

|

SU944079A1 |

| Фазометрическое устройство | 1980 |

|

SU917123A1 |

| Интегратор азимутных импульсов | 1977 |

|

SU691877A2 |

| ПРЕОБРАЗОВАТЕЛЬ ФАЗА - ПОСЛЕДОВАТЕЛЬНОСТЬИМПУЛЬСОВ | 1971 |

|

SU416722A1 |

| Устройство программного управления антенной | 1988 |

|

SU1594487A1 |

1. ИМПУЛЬСНО-ФАЗОВОЕ СЛЕДЯЩЕЕ УСТРОЙСТВО, содержащее усилитель.ограничитель, выход которого непосредственно и через инвертор соединен соответственно с первыми входами первого и второго блоков выборки,выходы которых соединены с первым и ---:,:« fe-V,--. I .. у;-|. вторым входами реверсивного счетчика, формирователь следящих импульсов, вход которого подключен к первому выходу синхронизатора, а первый выход - к второму входу первого блока выборки, отли-чающееся тем, что, с целью повышения точности устройства, оно содержит блок задержки и логический блок, первый и второй входы которого соединены с соответствующими выходами реверсив- ирго счетчика, третий вход через блок задержки и четвертый вход непосредственно - с вторым выходом синхронизатора, а первый и второй выходы - с соответствующими входами синхронизатора, второй выход формиро-о вателя следящих импульсов подключен к второму входу второго блока выбор(Л ки . со оо

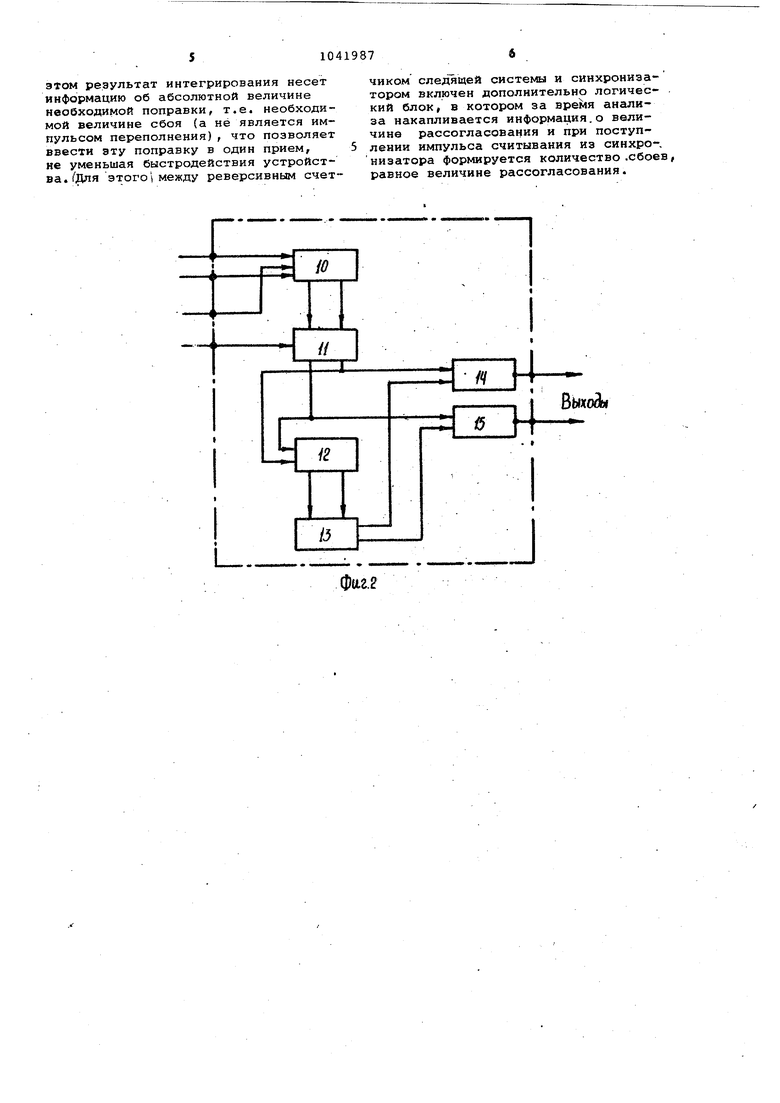

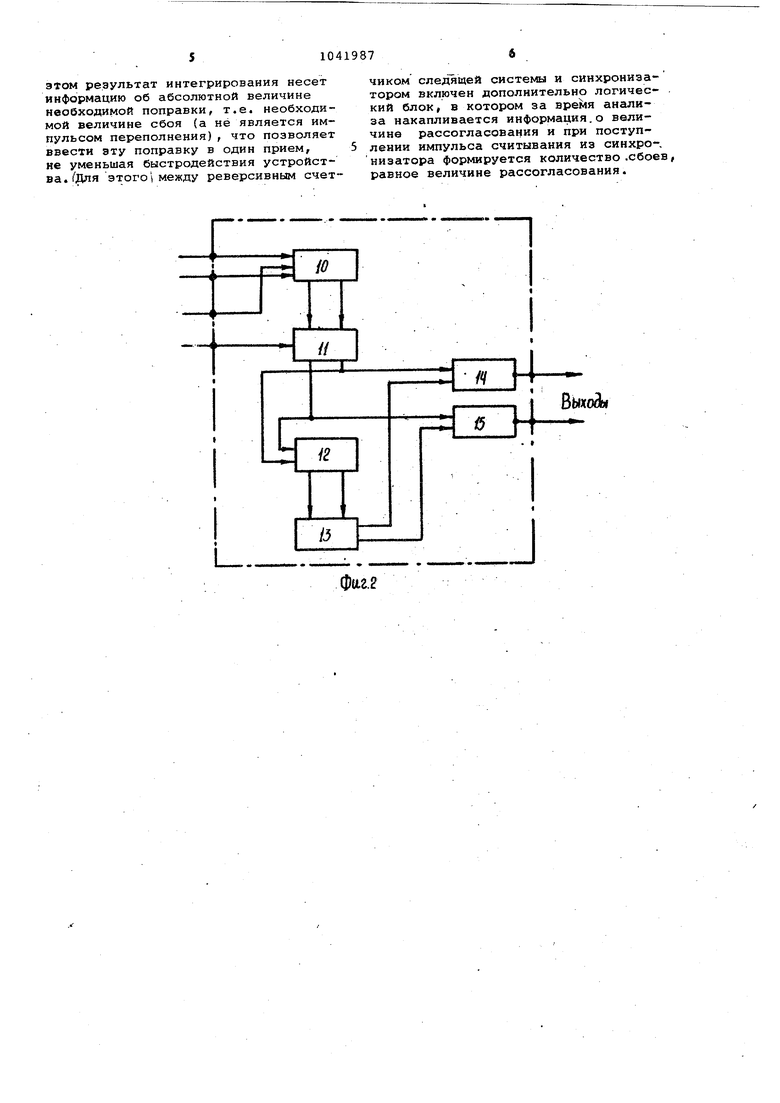

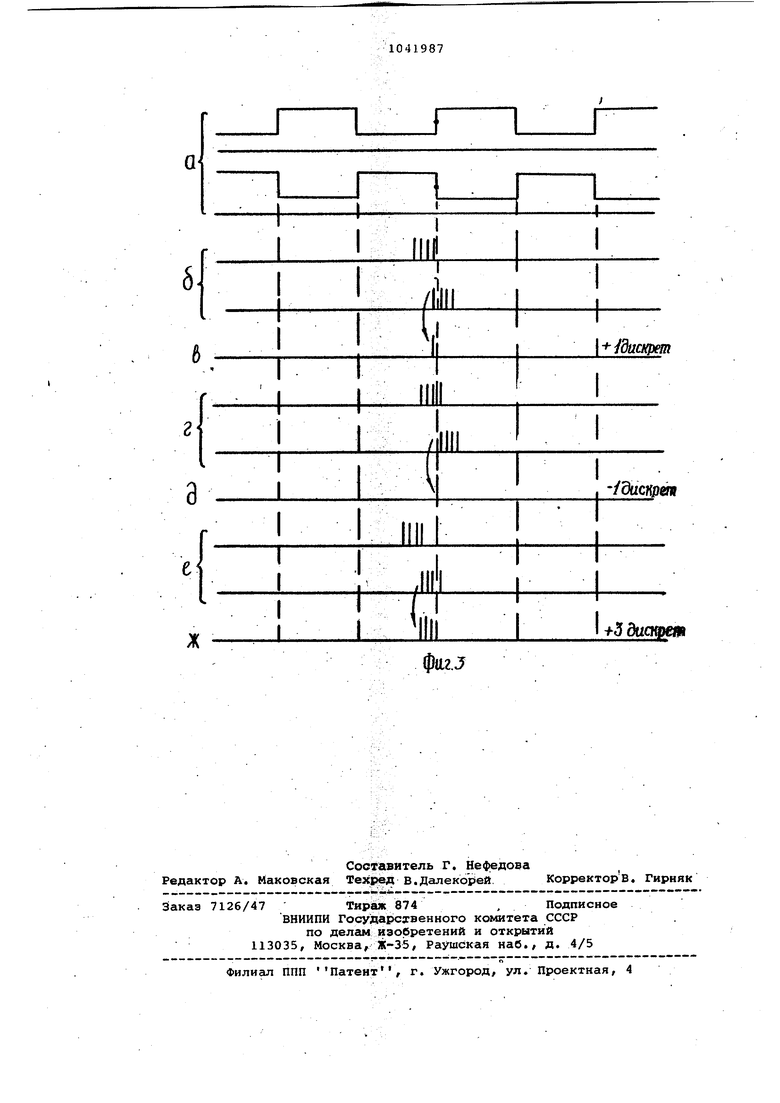

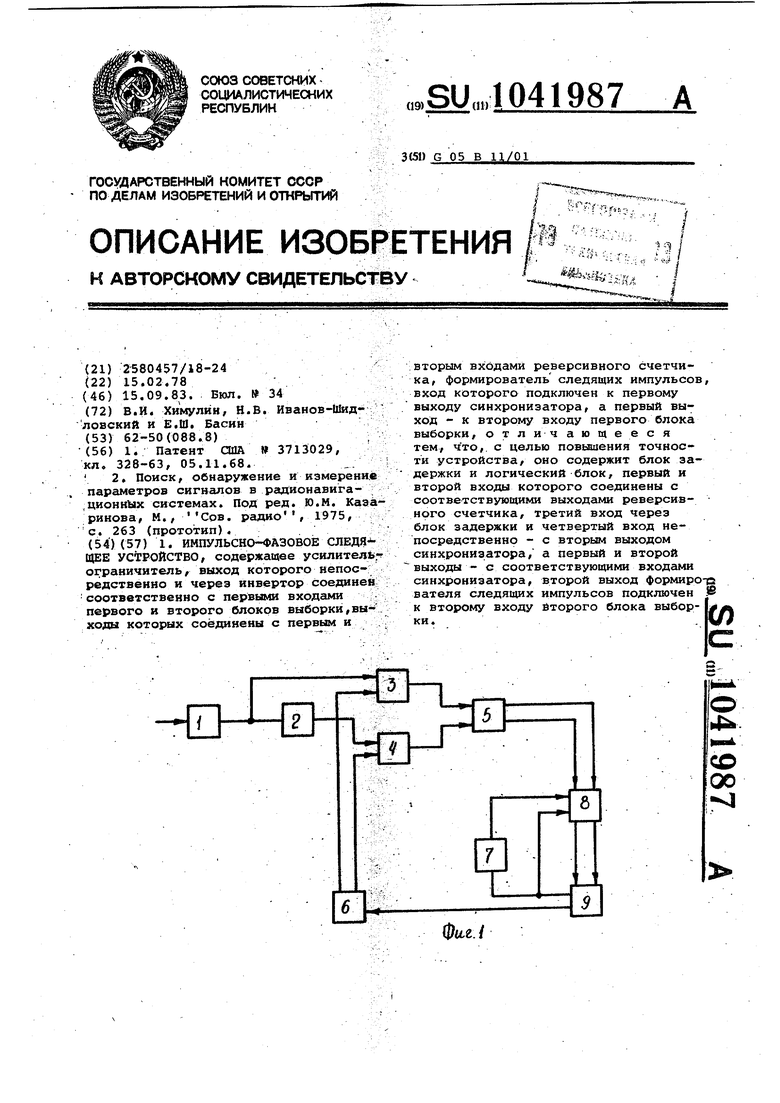

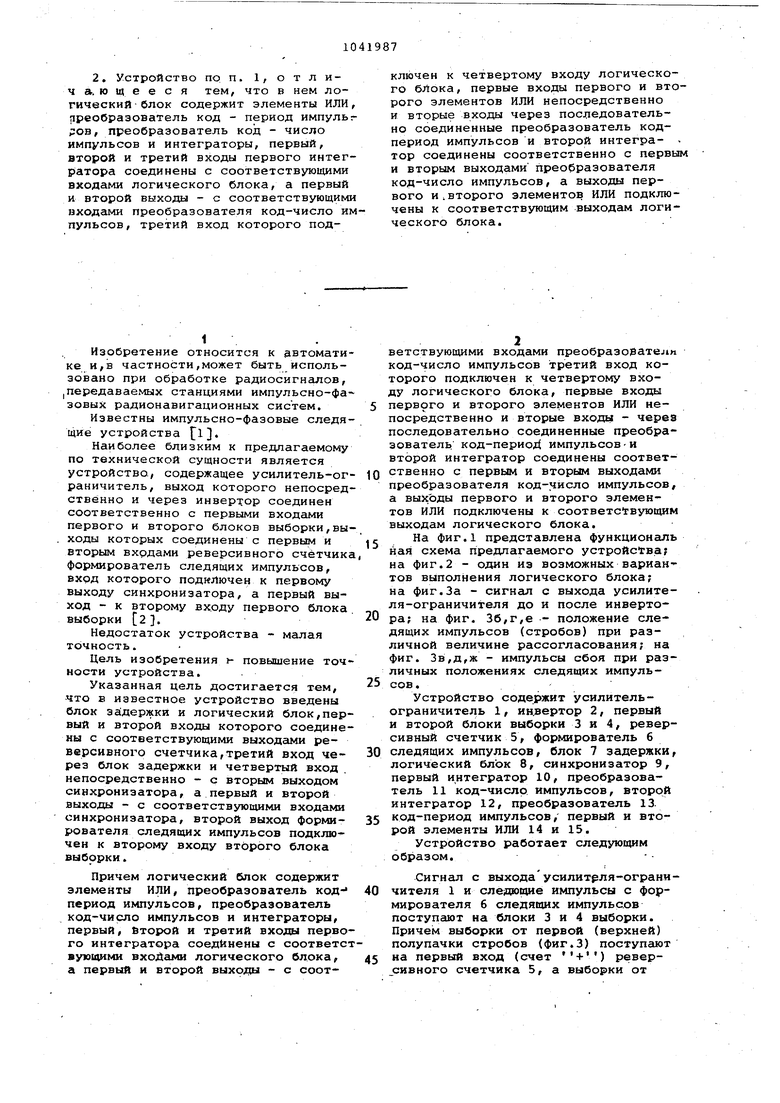

Изобретение относится к автомати ке и,в частности,может быть использовано при обработке радиосигналов, Iпередаваемых станциями импульсно-фа зовых радионавигационных систем. Известны импульсно-фазовые следя щие устройства fl. Наиболее близким к предлагаемому по технической сущности является устройство., содержащее усилитель-ог раничитель, выход которого непосред ственно и через инвертор соединен соответственно с первыми входами первого и второго блоков выборки,вы . ходы которых соединены с первым и вторым вхрдами реверсивного счётчик формирователь следящих импульсов, вход которого подключен к первому выходу синхронизатора, а первый выход - к второму входу первого блока выборки 2. Недостаток устройства - малая точность. Цель изобретения j- повышение точ ности устройства. Указанная цель достигается тем, что в известное устройство введены блок за держки и логический блок,пер вый и второй входы которого соедине ны с соответствующими выходами реверсивного счетчика,третий вход через блок задержки и четвертый вход непосредственно - с вторым выходом синхронизатора, а первый и второй выходы - с соответствующими входами синхронизатора, второй выход формирователя следящих импульсов подключен к второму входу второго блока выборки. Причем логический блок содержит элементы ИЛИ, преобразователь код- период импульсов, преобразователь код-число импульсов и интеграторы, первый, Второй и третий входы перво го интегратора соединены с соответс вующими входами логического блока, а первый и второй выходы - с соответствующими входами преобразователи код-число импульсов третий вход которого подключен к четвертому входу логического блока, первые входы первого и второго элементов ИЛИ непосредственно и вторые входы - через последовательно соединенные преобразователь. код-перио4 импульсов-и второй интегратор соединены соответственно с первым и вторым выходами преобразователя код-число импульсов, а выходы первого и второго элементов ИЛИ подключены к соответствующим выходам логического блока. На фиг.1 представлена функдиональ ная схема предлагаемого устройства; на фиг.2 - один из возможных вариантов выполнения логического блока; на фиг.За - сигнал с выхода усилителя-ограничителя до и после инвертора; на фиг. 36,г,е - положение следящих импульсов (стробов) при различной величине рассогласования; на фиг. Зв,д,ж - импульсы сбоя при различных положениях следящих импульсов. Устройство содержит усилительограничитель 1, инвертор 2, первый и второй блоки выборки 3 и 4, реверсивный счетчик 5, формирователь 6 следящих импульсов, блок 7 задержки, логический блок 8, синхронизатор 9, первый и,нтегратор 10, преобразователь 11 код-число импульсов, второй интегратор 12, преобразователь 13. код-период импульсов, первый и второй элементы ИЛИ 14 и 15. Устройство работает следующим образом. Сигнал с выходаусилитрля-ограничителя 1 и следюоще импульсы с формирователя б следящих импульс.ов поступают на блоки 3 и 4 выборки. Причем выборки от первой (верхней) полупачки стробов (фиг.З) поступают на первый вход (счет +) реверjCHBHoro счетчика 5, а выборки от второй (нижней) полупачки стробов на его второй вход (счет -). Сигнал ошибки при этом непропорционален, как в известном устройстве а равен величине временного рассогласования сле дящих стробов. На фиг. 36 показано смещение следящих стробов на 1 дискрет влево. При этом .импульсы (верхние) совпадают с нулем сигнала и на выходе блока 3 выборки импульсов счета нет, а в нижней по лупачке один импульс совпадает с положительной полуволной сигнала. На выходе блока 4 вы&орки появляется 1 импульс сбоя (фиг. Зв). Обратная картина,будет при смещении на 1 дискрет вправо (фиг.Зг и Зд). При смещении на 3 дискрета влево на выходе блока, 4 выборки появляется уже 3 импульса сбоя (фиг.. Зе и ЗГж) . Эти импульсы сбоя (т.е. информация о величине рассогласования следящих импульсов) далее усредняешься ревер, сивным счетчиком 5, объём которого , числу анализируемых за один цикл импульсов. Таким образом, если время анализа выбрано равным 10 периодам следования сигнала, то за 1 цикл анализируется & импульорв и объём реверсивного счетчика 5 вы бйрается равным 80. Тогда при велида не рассогласования, равной 1 дискрету, за время анализа реверсивный счетчик 5 переполняется 1 раз и на его выходе появляется 1 импульс. величине рассогласования, равнрй трем дискретам, на выходе реверсив-. ного счетчика за время анализа пройдёт 3 импульса и т.д. Эти; импульсы, поступают далее на логический блок, 8/ который в момент поступления импульса- считывания формирует такое количество импульсов сбоя, которое к этому времени накопилось в его схе ме памяти, т.е. количество j cKpeтов сбоя равно измеренной ве/1ичиие рассогласования. Импульсы сбоя пос тупают в синхронизатор 9, где по команде добавляется или вычитается соответствующее количество импульс д в периоде следования, и происходите временкой сдвиг выходных импульсов% синхронизатора 9 и следящих импуль-, сов. Таким образом, если за время анализа реверсивный счетчик 5 перепел.няется 5 раз в + и 5 раз в --j то при поступлении импульсов считы, .вайия на логический блок 8 сбоя нех: будет, так как в схеме памяти ( ческого блока 8) к этому времени 4; будет записан +5-5«0 дискретов. . Если за время ансшиза реверсивный счетчик 5 переполняется 6 раз в и 4 раза в -, то при поступления импульсов считывания вырабатывается команда сбоя на +2 дискрета. . В известном устройстве за это же время в среднем следящий строб тоже флюктуирует около истинного значения, но разбросы мгновенных положений стробов в каждый данный момент времени значительно больше, чем в предлагаемом устройстве, так как на синхронизатор 9 пройдет каждый отдельный сбой, т.е. скорость отработки в данном устройстве остается той же, что и в известном, но разброс мгновенных отклонений следящих стробов значительно уменьшается, а следовательно, повышается точность единичного измерения. После команды сбоя в блоке 7 задержки формируется импульс сброса, задержанный по времени относительно импульсов считывания, который после прохождения сбоя обнуляет логический блок 8..При реализации следящей системы второго порядка логический блок 8 может иметь, например, вид, изображенный на фиг.2. В первом интеграторе 10 логического блока за время анализа усредняется информация о величине рассогласования следящего строба, которая через преобразователь 11 код-число импульсов в момент поступления им- пульса считывания поступает на это-, рой интегратор (скорости) 12 и на первый и второй элементы ИЛИ 14, 15. Число импульсов на выходе преобразователя 11 Код-число импульсов равно числу, записанному в. первом интеграторе 10, т.е. равно величине временного рассогласования следящих импульсов относительно перехода фазы После поступлесигнала через. ния этих импульсов через элементы ИЛИ 14 или 15 на синхронизатор .9 строб слежения перемещается непосредственно на эту величину. После прохождения сбоя первый интегратор 10 сбрасывается в начальное состояние импульсом сброса. Число во втором интеграторе- 12 (а ,йледовательно, и число дополнительных импульсов сбоя) растет до тех пор,дока не сравняется количество сбоев в + и в - на входе второго интегратора 12. Это соответствует нулевой ошибке по скорости. Чем болье скорость, тем большее число записано во втором интеграторе 12 и т.ем чаще ( меньшим периодом) поступают дополнительные импульсы сбоя с преобразователя 13 код-период имульсов. Так,при скорости 0,1 мкс/с и дискретов сбоя 0,1 мкс импульсы с выхода преобразователя 13 код-период импульсов следует с периодом 1с, а скорости 1 мкс/с - в 10 раз чаще. Такое выполнение устройства позоляет повысить точность за счет обавочного интегрирования, но при

этом результат интегрирования несет информацию об абсолютной величине необходимой поправки, т.е. необходимой величине сбоя (а не является импульсом переполнения), что позволяет ввести эту поправку в один прием, не уменьшая быстродействия устройства. /Для этого ) между реверсивным счетчиком следящей системы и синхронизатором включен дополнительно логический блок, в котором за время анализа накапливается информаг ия. о величине рассогласования и при поступлении импульса считывания из синхро-, низатора формируется количество .сбоев, равное величине рассогласования.

фагЛ

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Патент ОНА W 3713029, кл, 328-63, 05.11.68.. | |||

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Поиск, обнаружение и измерение параметров сигналов в радионавига,ционнЫх системах | |||

| Под ред | |||

| Ю.м | |||

| Каэаринова, М., Сов | |||

| радио , 1975, с | |||

| Железнодорожный снегоочиститель на глубину до трех сажен | 1920 |

|

SU263A1 |

Авторы

Даты

1983-09-15—Публикация

1978-02-15—Подача