первый, второй, третий, четвертый, пятый, шестой, седьмой, восьмой и девятый элементы И, элемент ИЛИ и генератор тактовых импульсов, выход которого соединен с четвертыми входами четвертого, пятого и восьмого элементов И, с вторыми входами второго и третьего элементов И и через инвертор с четвертым входом девятого элемента И и с вторым входом первого элемента И, выход которого соединен с вторым входом второго триггера, первый вход которого соединен с прямым выходом первого триггера, первый вход которого соединен с входом

блока, первый, четвертый, пятый и.второй выходы которого соединены соответственно с выходами ч твертого, пятого, восьмого элементов И и элемента ИЛИ, входы которого соединены G выходами шестого и седьмого элементов И, прямой выход третьего триггера -соединен с третьим выходом блока и третьими входами первого элемента И и первого триггера,

второй вход которого соединен с инверсным выходом третьего триггера, второйвход которого соединен с выходом второго элемента И и вторым входом счетчика, первый выход которого соединен с третьими входами пятого, шестого, .девятого и через инвертор четвертого и восьмого элементов И, прямой и инверсный выходы второго триггера соединены с первыми входами соответственно второго и третьего элементов И, выход третьего элемента И соединен с первым входом счетчика,второй выход которого соединен с первыми входами шестого, восьмого, девятого и через инвертор четвертого, пятого и седьмого элементов И, третий выход счетчика соединен с вторыми входами седьмого, восьмого, девятого и через инвертор четвертого, пятого и шестого элементов И, выход девятого элемента И соединен с первым входом третьего триггера.

3. Устройство по п. 1, о т л ичающееся тем, что блок выделения и идентификации символа содержит первый, второй и третий триггеры, первый, второй, третий, четвертый, пятый, шестой, седьмой

элементы,И и элемент ИЛИ, инверсный выход которого соединен с первым входом седьмого элемента И, выход которого соединен с пятым выходом блока, первый, второй, третий, четвертый , iJiecToA выходы которого соединены соответственно с выходами пятого, четвертого, третьего, второго шестого элементов И, выход пятого элемента И соединен с вторыми входами шестого и седьмого элементов И первый вход блока соединен с вторым входом третьего триггера, прямой выход которого соединен с третьими входами второго, третьего, шестого элементов И и с первым входом элемента ИЛИ, второй вход которого соединен с третьими входами четвертого элемента И и третьего триггера и с прямым выходом второго триггера второй вход которого соединен с выходом первого элемента И, первый вход которого соединен с вторым входом блока, третий вход которого соединен с первыми входами третьего и четвертсЗго элементов И и второго триггера, инверсный выход которого соединен с первым входом шестого элемента И, четвертый и пятый входы блока соединены соответственно С вторым и третьим входами первого триггера, выход которого соединен с вторыми входами первого, второго, третьего, четвертого, пятого элементов И, шестой вход блока соединен с первыми входами первого триггера и второго элемента И, седьмой вход блока соединен с первыми , входами пятого элемента И и третьего триггера, инверсный выход которого соединен с третьим входом первого элемента И.

4, Устройство по п. 1, отличающееся тем, что блок управления движением головки содержит схему сравнения, первый и второй элементы И, первый и второй триггеры вход первого адреса дорожки, вход второго адреса дорожки и выход сравнения блока соединены соответственно с первым и вторым входами и первым выходом схемы сравнения, второй и третий выходы которого соединены с первыми входами соответственно первого и второго элементов И, вторые входы которых соединены с входом разрешения блока, выход Шаг назгщ и выход Шаг вперед которого соединены с выходами соответственно первого и второго триггеров, вторые входы которых соединены с входом Начало дорожки блока, выходы первого и второго элементов И соединены с первыми входами соответственно первого и второго триггеров. Изобретение относится к вычислительной технике и может, быть применено в ЭВМ с перезагружаемой память микропрограмм. HsrifecTHo устройство, содержащее сдвигаквдий регистр, сепаратор,.счет чик байтов 1 . Недостатком устройства является отсутствие возможности его использования для загрузки микропрограмм в процессор, так как информация, считанная с пультового накопителя, может использоваться только для диагностических и сервисных функций Известно также устройство управл ния для аппаратуры хранения последо вательной информации, содержащее сепаратор , счетчик байтов, регистр данных накопителя, коммутатор, регистр данных 2 . Недостатком этого устройства являются большие затраты оборудования. Наиболее близким к изобретению является устройство, содержащее регистр данных накопителя, регистр данных, счетчик символов и сепаратор, первый вход и выход которого соединены соответственно с первым входом устройства и с первым входо регистра данных накопителя, первый выход которого соединен со вторым входом регистра данных, выход кото рого соединен с первым выходом устройства з . Недостатком данного устройства являются избыточные затраты оборудования, связанные с реализацией возможности модификации адреса доро ки На произвольную величину, а также с наличием сложного оборудова ния для определения конца массива. данных и окончания процесса загрузки. Кроме того, избыточн г1е затраты 9борудования требуются для идентифи кации. . считываемой с носителя инфо . мации и для реализации довольно сложного алгоритма связи этого устрой ства с процессором. Цель изобретения - сокращение jаппаратурных затрат. Поставленная цель достигается тем, что в устройство управления загрузкой микропрограмм, содержащее регистр сдвига, счетчик символов, регистр данных и блок выделения временных битов и битов данных, пер вый вход KOTOiporo подключен к информационному входу устройства, а первый выход - к информационному вх ду регистра сдвига, выход данных которого соединен с входом данных, регистра данных, выход которого под ключей к выходу данных устройства, в него введены блок синхронизации, блок выделения и идентификации символоЁ, счетчик адреса дорожки, блок управления движением головки, триггер и -элемент И, причем выход счетчика еимволов подключен к перво- му входу блока выделения и идентификации символов, к первому входу счетчика адреса дорожки и первому входу элемента И, выход которого соединен с выходом .конца передачи массива устройства, а второй-вход с выходом триггера, вход блока синхронизации подключен к информационному входу устройства, первый выход - к второму входу блока выделения временных битов и, к управляющему входу регистра сдвига, второй выход - к третьему входу блока выделения временных битов и битов данных, третий выход - к четвертому входу блока выделения временных битов и-битов данных, пятый вход которого соединен с входом сброса регистра сдвига и первым выходом блока выделения и идентификации данных, , второй выход которого подключен к установочному входу триггера, вход данных которого соединен с входом первого адреса дорожки блока управления движением головки и выходом регистра сдвига, третий выход блока выделения и идентификации символа подключен к разрешающему входу регистра данных, четвертый выход к входу счетчика символов, пятый выход - к входу разрешения блока управления движением головки, шестой выход - к выходу строба передачи устройства, второй вход - к выходу сравнения блока управления движением головки, третий вход - к второму выходу блока синхронизации, пятый вход - к выходу признака регистра сдвига, шестой вход - к четвертому выходу блока синхронизации, седьмой вход - к пятому выходу блока синхронизации, второй вход счетчика адреса дорожки подключен к входу начального адреса устройства, а выход - с входом второго адреса дорожки блока управления движением головки, вход Начало дорожки которого соединен с входом Начало дорожки устройства, а выходы Шаг назад и Шаг вперед - с выходами Шаг назад и Шаг вперед устройства соответственно. Блок синхронизации содержит счетчик, первый, второй .и третий триггеры, первый, второй, третий, четвертый, пятый, шестой, седьмой, восьмой, девятый элементы И, элемент ИЛИ и генератор тактовых импульсов, выход которого соединен с четвертыми входами ,четвертого, пятого и восьмого элементов И, с вторыми входами второго и третьего элементов И и че-. рез инвертор с четвертым входом девятого элемента И и с вторым входом первого элеменга И, выход которого соединен с вторым входом второго триггера, первый вход которого соединен с прямым выходом первого триггера, первый вход которого соединен с входом блока, четвертый, пятый и второй выходы которого соединены cooTBeTCTjleHHo с выходами чет вертого, пятого, восьмого элементов И и элемента ИЛИ, входы которого йОединены с выходами шестого и седьмого элементов И, прямой выход третьего триггера соединен с третьим выходом блока и тpeтьи м входами первого элемента И и первого триггера, второй вход которого соединен с инверсным, выходом третьего триггера, второй вход которого соединен с выходом второго элемента И и вторым входом счетчика, первый выход кото,рого соединен с третьими входами пятого, шестого, девятого и через инвертор четвертого и восьмого элементов И, прямой и инверсный выходы второго триггера соединены с первыми входами соответственно второго и третьего элементов И, выход третьего элемента И соединен с первым входом счетчика, второй выход которого соединен с первыми входами шестого, восьмого, девятого и через инвертор четвертого, пятого и седьмго элементов И, третий выход счетчика соединен с вторыми входами ,восьмого,девятого и через инвертор четвертого,пятого и шестого элементов И,выход девятого элемента И соединен с первым входом третьего триггера. Блок выделения и идентификации символа содержит первый, второй и третий триггеры, первый, второй, третий, четвертый, пятый, шестой, седьмой элементы И и элемент ИЛИ, инверсный выход которого соединен с первым входом седьмого элемента И, выход которого соединен с пятым выходом блока, первый, второй, третий, четвертый, шестой выходы которого соединены соответственно с выходами пятого, четвертого, третьего, второго, шестого элементов И, выход пятого элемента И соединен с вторыми входами шестого и седьмого элементов И, первый вход блока соединен с вторым входом третьего триггера, прямой выход которого соединен с третьими входами второго, третьего, шестого элементов и и с первым входом элемента ИЛИ, второй вход которого соединен с третьими входами четвертого элемента И и третьего триггера и с npHNMM выходом второго триггера, втрой вход которого соединен с выходом первого элемента И, первый вход которого соединен с вторым входом блока, третий вход которого соединен с первыми входами третьего и четвертого элементов И и второго

триггера, инверсный выход которого соединен с первым входом шестого элемента И, четвертый и пятый входы блока соединены соответственно с вторым и третьим входами первого триггера,выход которого соединен с вторыми входами первого, второго третьего, четвертого, пятого элементов И, шестой вход блока соединен с первыми входами первого триггера и второго элемента И, седьмой .вход блока соединен с первыми вход МИ пятогоэлемента И и третьего триггера, инверсный выход которого соединен с третьим входом первого элемента И.

Блок управления движением голоВ ки содержит схему сравнения, первый и второй элементы И, первый и второй триггеры, причем вход первого адреса дорожки, вход второго адреса дорожки и выход сравнения блока соединены соответственно с первым и вторым входами и первым выходом cxevbi сравнения, второй и третий выходы которой соединены спервыми входами соотве -ственно первого и второго элементов И, вторые входы которых соединены с входом разрешения блока, выход Шаг назад и выход Шаг вперед которого соединены с выходами соответственно первого и второго триггеров, вторые входы которых соединены с входом Начало дорожки блока, выходы первого и второго элементов И соединены с первыми входами соответственно первого и второго триггеров.

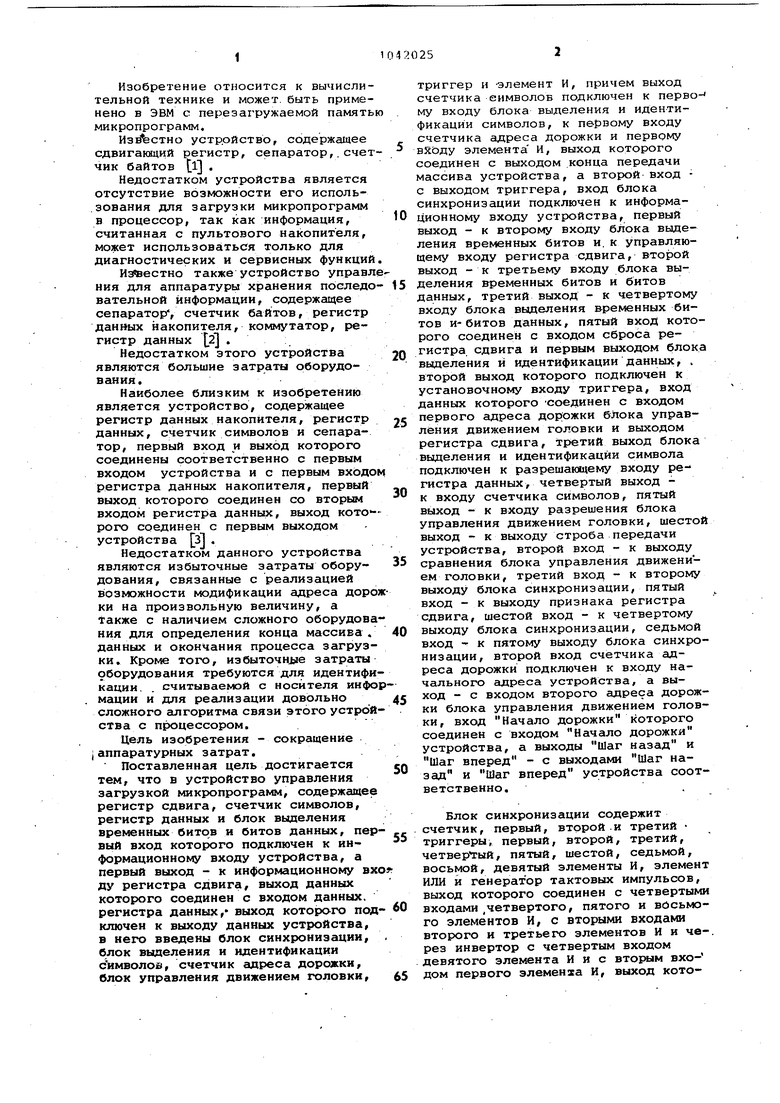

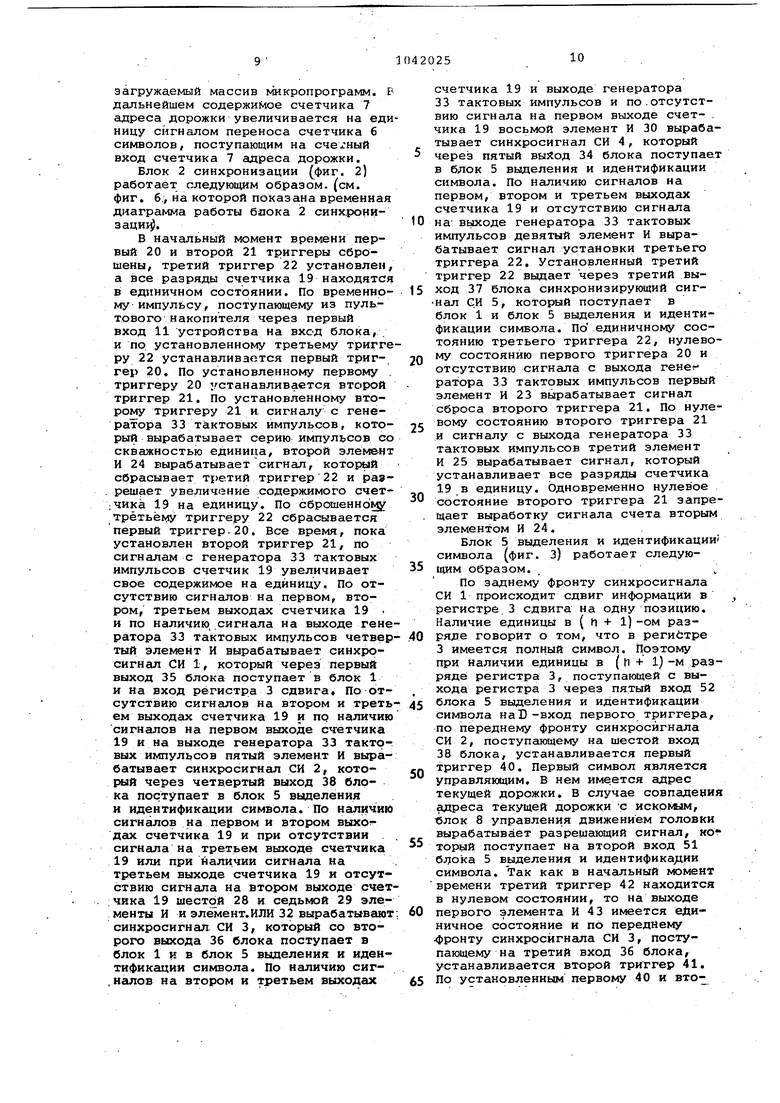

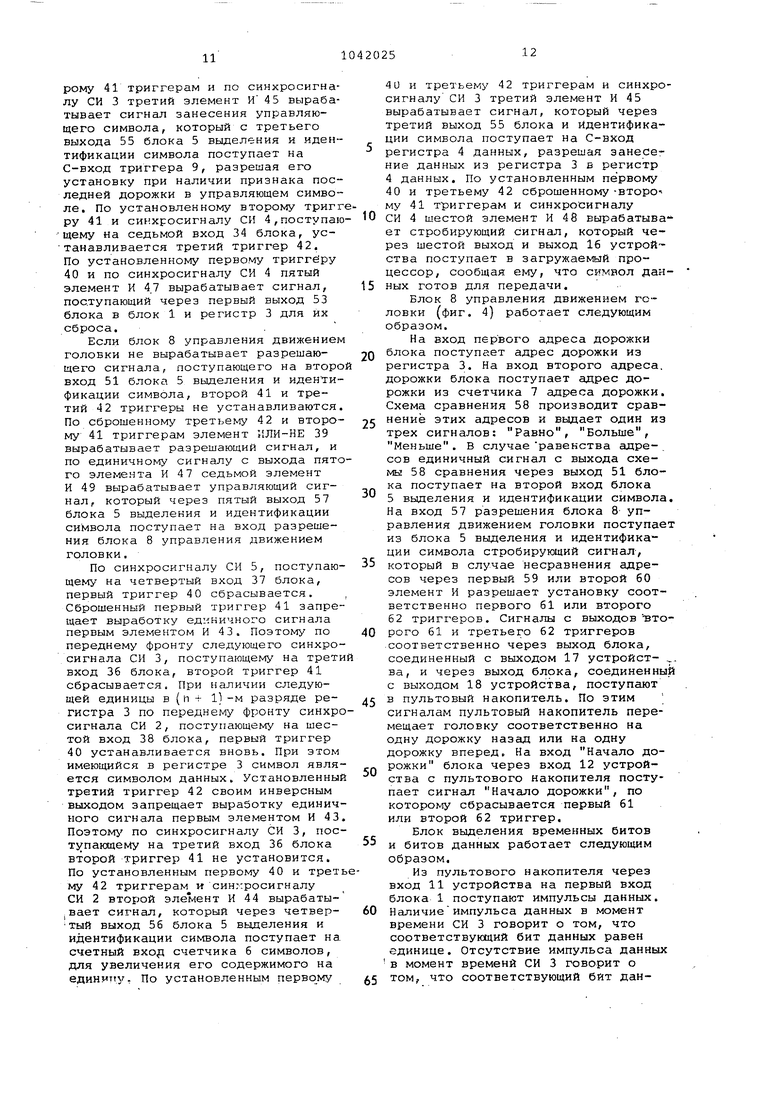

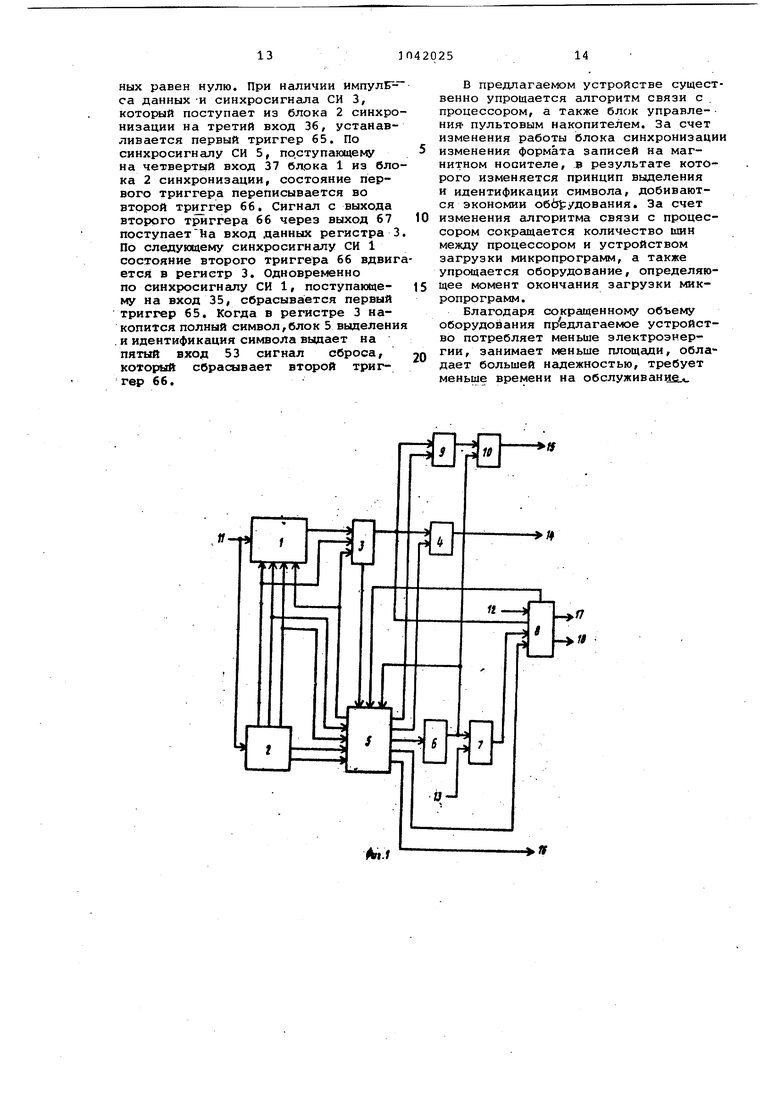

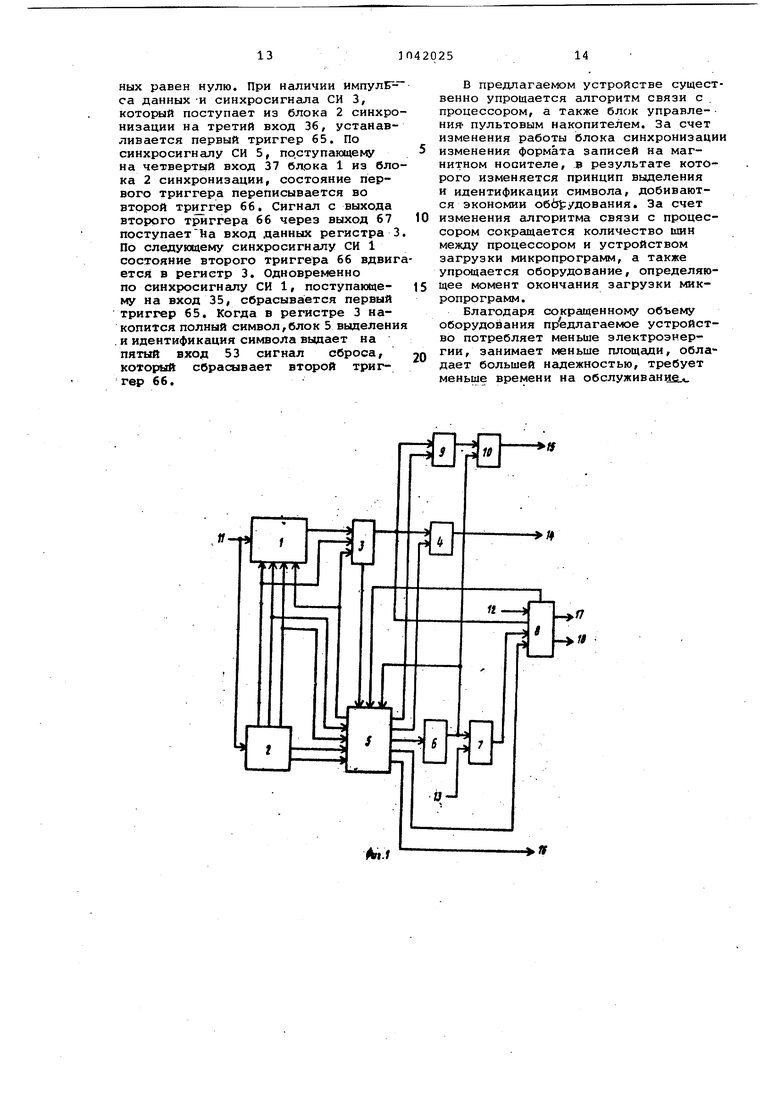

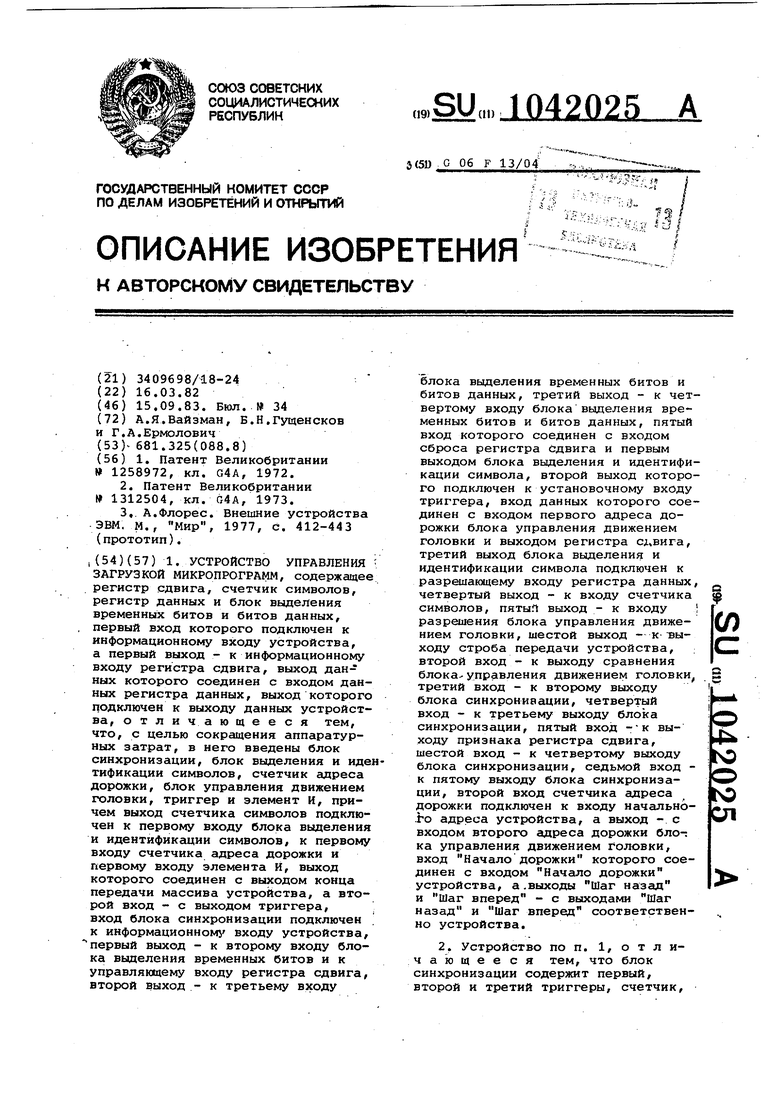

На фиг. 1 изображена схема предлагаемого устройства управления загрузкой микропрограмм; на фиг.2 схема блока синхронизации; на фиг. 3 - то же, блока выделейия и идентификации символа; на фиг. 4 то же, блока управления движением головки; на фиг. 5 - то же, блока выделения временных битов и битов данных; на фиг. б - временная диаграмма работы блока синхронизации.

Устройство управления загрузкой микропрогралфл (фиг. ,1) содержит блок 1 выделения временных битов и битов данных, блок 2 синхронизации, регистр 3 сдвига, регистр 4 данных, блок 5 выделения и идентификации символа, счетчик 6 символов, счетчик 7 адреса дорожки, блок 8 управления движением головки, триггер 9 и элемент И 10; 11-13 - входы и 14-18 - выходы устройства.

Информационный вход 11устройства загрузки микропрограмм соединен с первым входом блока 1 и с входом блока 2 синхронизации. Первый выход блока 2 синхронизации соединен со вторыми входами блока 1 и регистра 3,второй выход блока 2 синхронизации соединен с третьими входами блока 1 и блока 5 вьщеления и идентификации символа. Третий выход блока 2 синхронизации соединен с четвертыми входами блока 1 и блока

5выделения и идентификации символа. Четвертый и пятый выходы блока

2синхронизации соединены соответственно с шестым и седьмым входами блока 5 выделения и идентификации символа. Первый выход блока 5 выделения и идентификации символа соединен с пятым входом блока 1 и входом сброса регистра 3.. Выход блока

1 соединен с входом данных регистра

3сдвига. Выход данных регистра 3 соединен со входом первого адреса дорожки блока 8 управления движением головки, со входом данных регистра 4 и выходом данных триггера

9. Второй выход признака регистра

3соединен с пятым входом блока 5 выделения и идентификации символа; Второй выход блока 5 выделения и идентификации символа соединен с установочным входом триггера 9. Выход триггера 9 соединен со вторым входом та И 10. Третий выход блока 5 выд.еления и идентификации символа соединен с решающим входом регистра 4 данных. Выход регистра 4данных соединен с выходом 14 данных устройства. Четвертый выход блока 5 выделения и идентификации символа соединен со входом счетчика

6символов. Выход счетчика б символов соединен с первым входом счетчика 7 адреса дорожки, с первым входом блока 5 выделения и идентифи кации символа и первым входом элемента И 10. Выход элемента И 10 сое динен с выходом 15 конца передачи массива устройства. Пятый выход

блока 5 выделения и идентификация символа соединен с входом разрешения блока 8 управления движением головки. Шестой выход блока 5 выделения и идентификации символа соеди нен с выходом 16 строба передачи устройства. Второй вход счетчика 7 адреса дорожки соединен с входом 13 начального адреса устройства, Выход счетчика 7 адреса дорожки соединен с входом второго адреса дорожки блока 8 управления движение головки. Вход Начало дорожки блока 8 управления движением головкисоединен со входом Начало дорожки устройства. Выход блЬка управления движением головки соединен со вторым входом 5 блока выделения и идентификации символа. Шлсоды 17 и 18 Шаг назад и Шаг вперед устройства совпадают соответственно с выходами Шаг назад вперед блока 8 управления движением головки

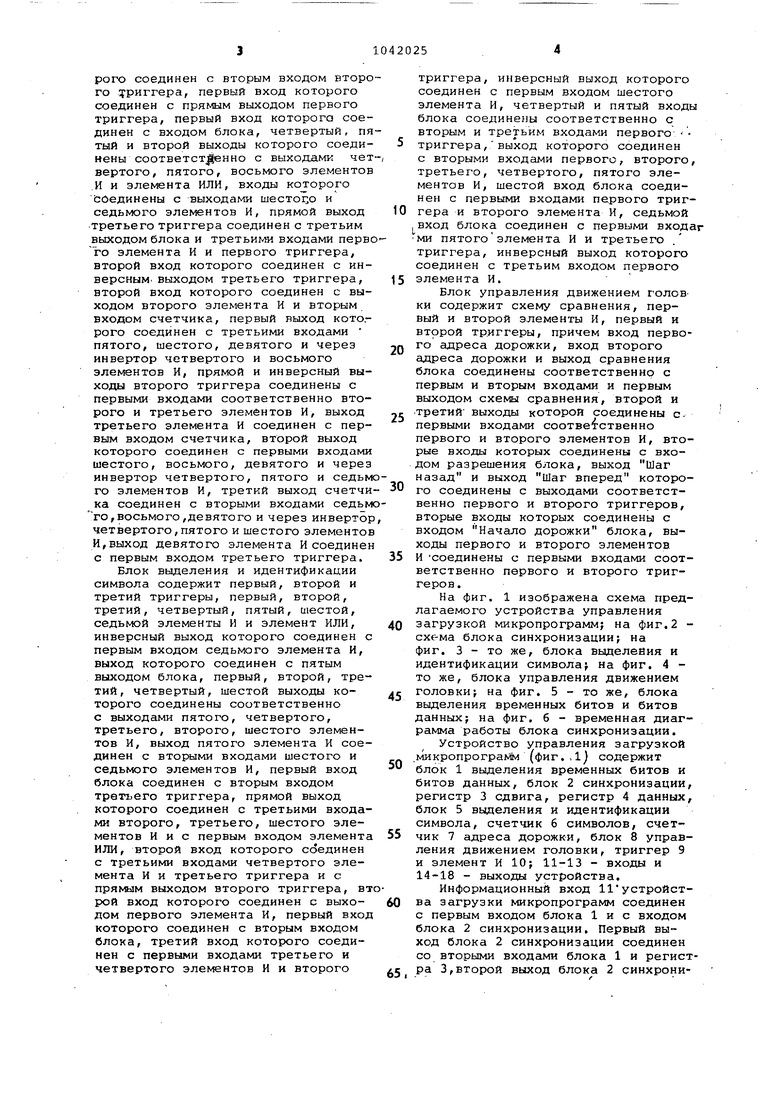

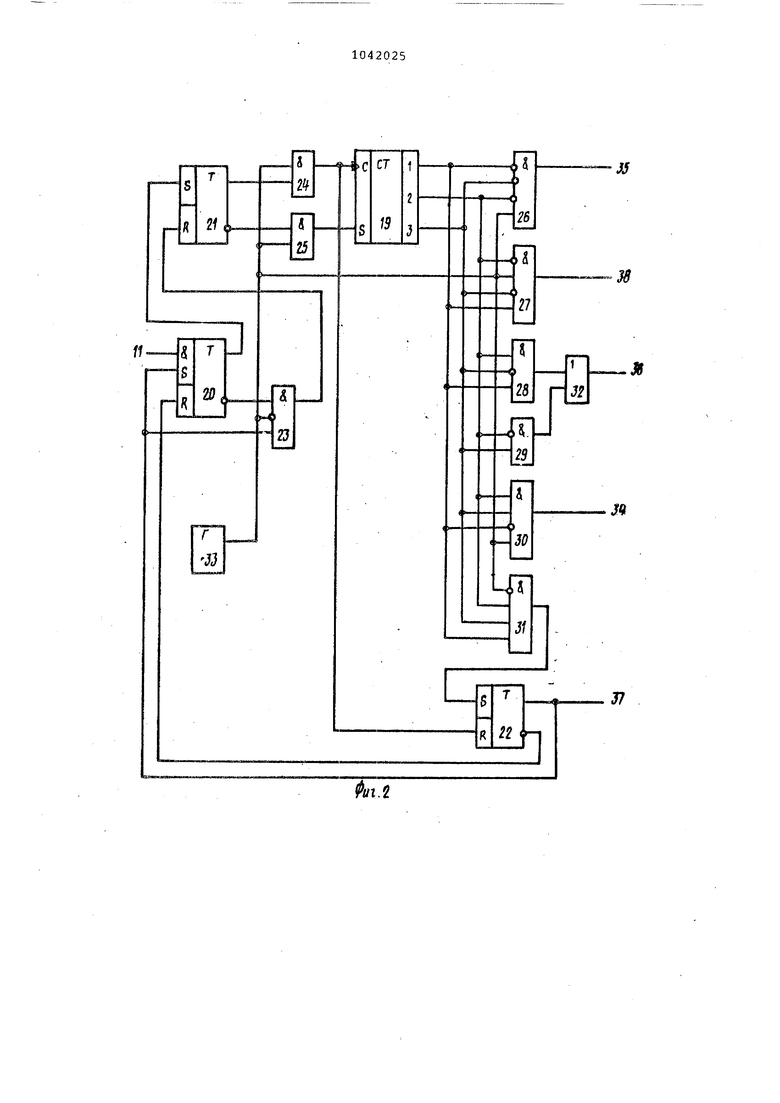

Влок 2 синхронизации (фиг. поёдназначен для выработки синхрони

зирующих сигналов, управляквдих работой устройства. Он содержит счетчик 19, первый 20, второй 21 и третий 22 триггеры, первый 23, второй 24, третий 25, четвертый 26, пятый 27, шестой 28, седьмой 29, восьмой 30, девятый 31 элементы И, элемент ИЛИ 32 и генератор 33 тактовых импульсов, 34-38 - выходы блока.

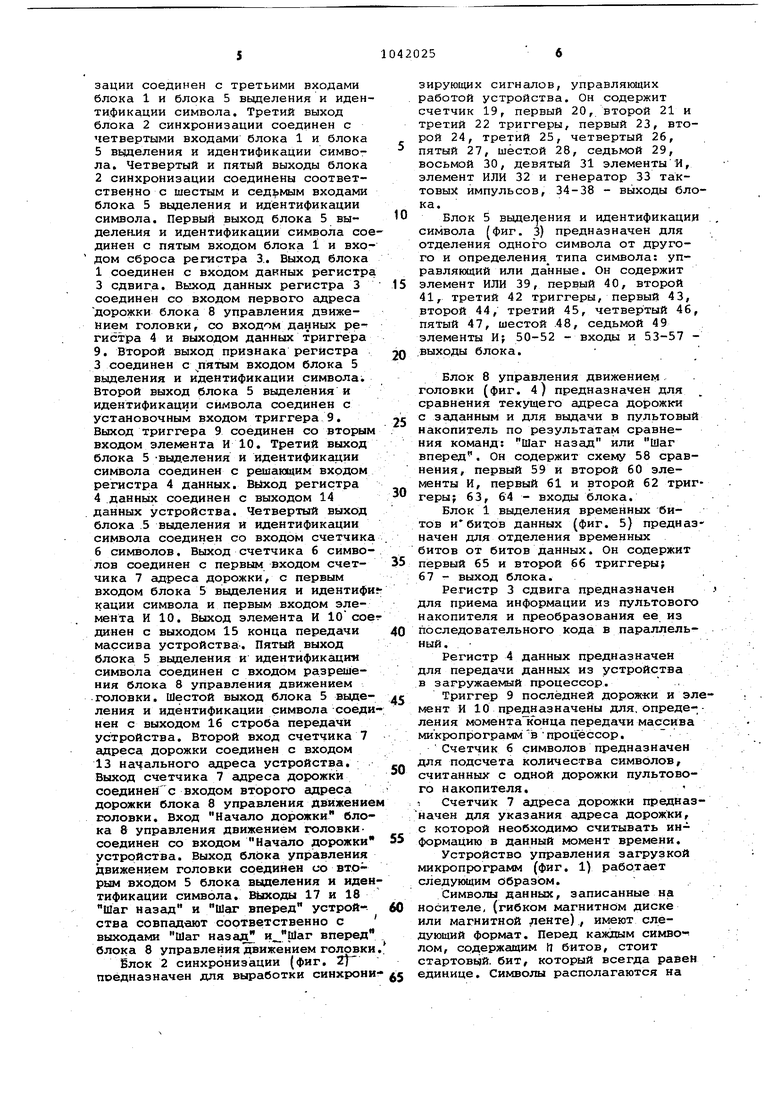

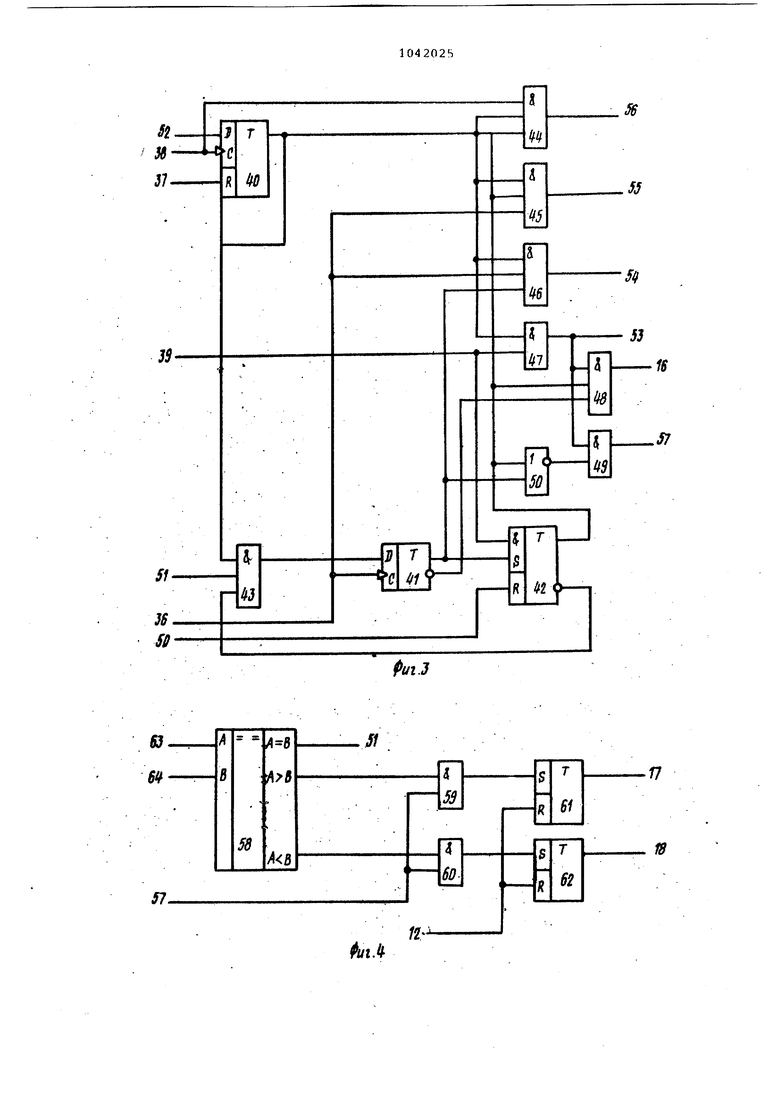

Блок 5 выдед ения и идентификации символа (фиг. 3) предназначен для отделения одного символа от другого и определения типа символа: управляющий или данные. Он содержит элемент ИЛИ 39, первый 40, второй 41, третий 42 триггеры, первый 43, второй 44, третий 45, четвертый 46 пятый 47, шестой .48, седьмой 49 элементы И; 50-52 - входы и 53-57 .выходы блока.

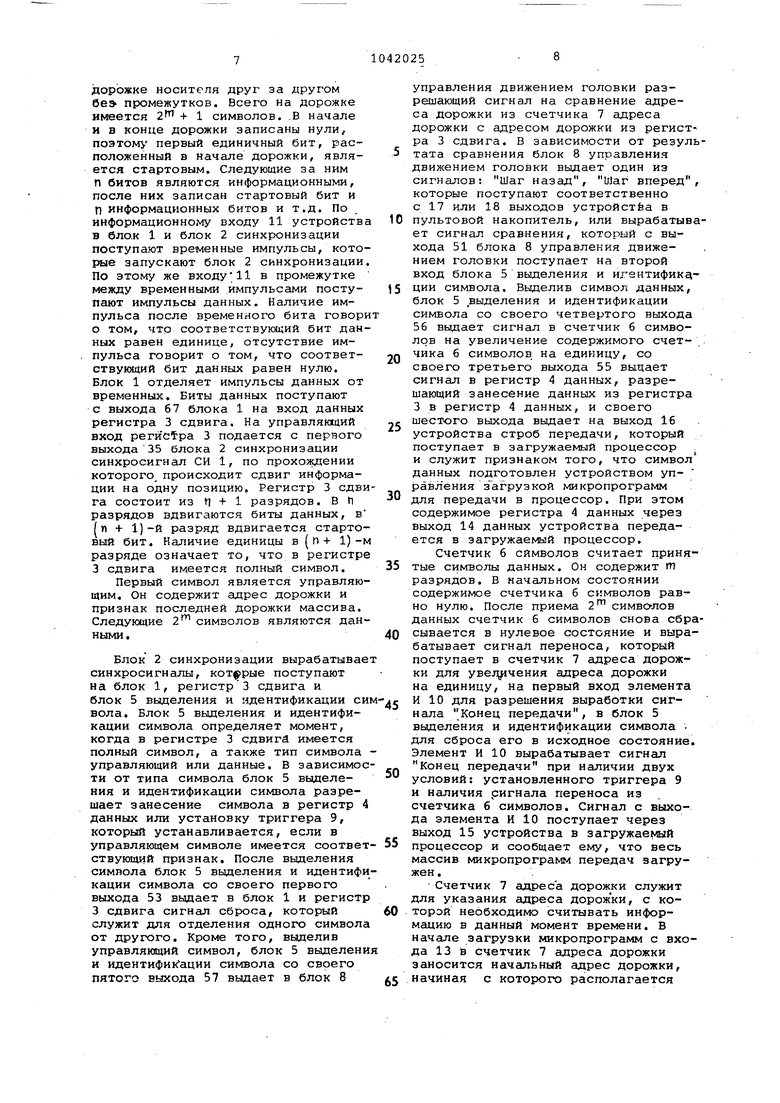

Блок 8 управления движением головки (фиг. 4) предназначен для сравнения текущего адреса Дорожкя с заданным и для выдачи в пультовый накопитель по результатам сравнения команд: Шаг назад или Шаг вперед. Он содержит схему 58 сравнения, первый 59 и второй 60 элементы И, первый 61 и второй 62 триггеры; 63, 6:4 - входы блока.

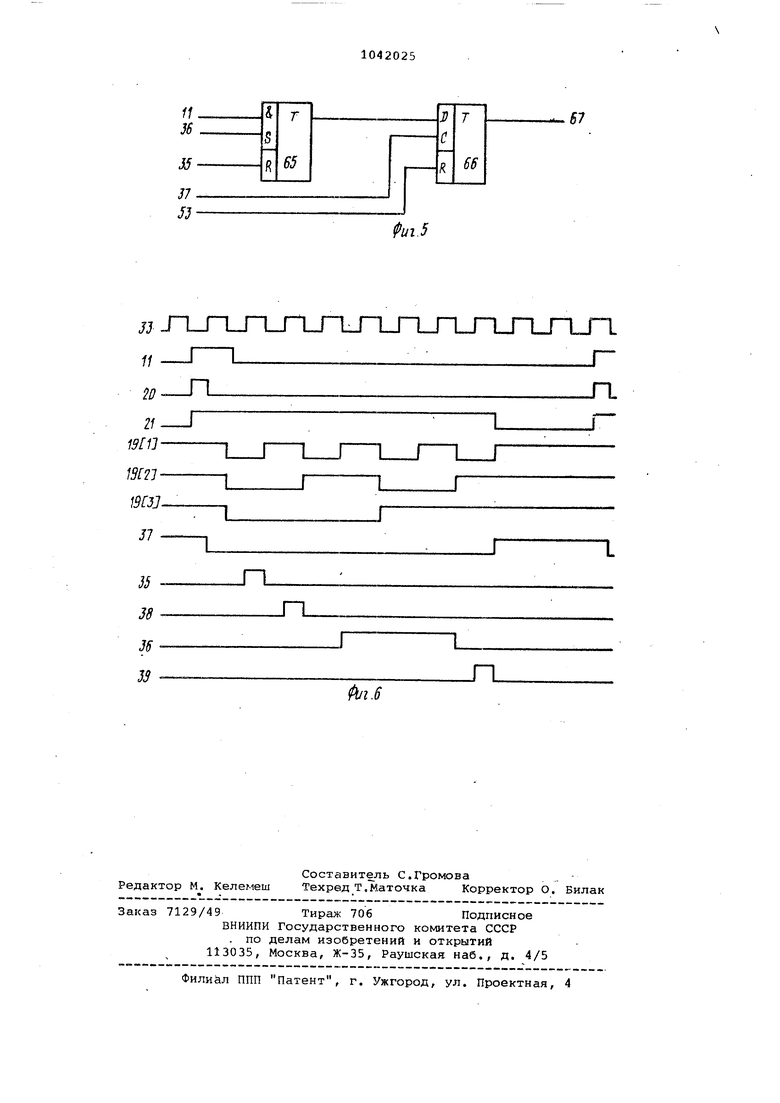

Блок 1 выделения временных битов и битов данных (фиг. 5) предназначен для отделения временных битов от битов данных. Он содержит первый 65 и второй 66 триггеры; 67 - выход блока.

Регистр 3 сдвига предназначен для приема информации из пультового накопителя и преобразования ее из последовательного кода в параллельный.

Регистр 4 данных предназначен для передачи данных из устройства в загружаемый процессор. ,

Триггер 9 последней дорож-ки и элмент И 10 предназначены для. определения моментакЪнца передачи массива микропрограммвпроцессор.

Счетчик 6 символов предназначен для подсчета количества символов, считанных с одной дорожки пультового н акопителя. л Счетчик 7 адреса дорожки предназначен для указания адреса дорожки, с которой необходимо считывать информацию в данный момент времени.

Устройство управления загрузкой микропрограмм (фиг. 1) работает следующим образом.

Символы данных, записанные на носителе, (гибком магнитном диске или магнитной ленте), имеют следующий формат. Перед каждым символом, содержащим П битов, стоит стартовый, бит, который всегда равен единице. Симво.пы располагаются на дорожке носителя друг за другом бе промежутков. Всего на дорожке имеется 2 + 1 символов. .В начале и в конце дорожки записаны нули, поэтом первый единичный бит, расположенный в начале дорожки, является стартовым. Следующие за ним п битов являются информационными, после них записан стартовый бит и П информационных битов и т.д. По информационному входу 11 устройств в бло.к 1 и блок 2 синхронизации поступают временные импульсы, кото рые запускают блок 2 синхронизации По этому же входу;11 в промежутке между временными импульсами поступают импульсы данных. Наличие импульса после временного бита говор о том, что соответствующий бит дан ных равен единице, отсутствие импульса говорит о том, что соответствующий бит данных равен нулю. Блок 1 отделяет импульсы данных от временных. Биты данных поступают с выхода 67 блока 1 на вход данных регистра 3 сдвига. На управляющий вход регистра 3 подается с первого выхода 35 блока 2 синхронизации синхросигнал СИ 1, по прохоадении которого происходит сдвиг информации на одну позицию. Регистр 3 сдв га состоит из tl + 1 разрядов. В h разрядов вдвигаются биты данных, в (п + 1)-й разряд вдвигается старто вый бит. Наличие единицы в ( И + 1)разряде означает то, что в регистр 3 сдвига имеется полный символ. Первый символ является управляю щим. Он содержит адрес дорожки и признак последней дорожки массива. Следующие 2 символов являются дан ными , Блок 2 синхронизации вырабатыва синхросигналы, которые постуПс1ЮТ на блок 1, регистр 3 сдвига и блок 5 выделения и идентификации с вола. Блок 5 выделения и идентификации символа определяет момент, когда в регистре 3 сдвиги имеется полный символ, а также тип символа управляющий или данные. В зависимо ти от типа символа блок 5 выделения и идентификации символа разрешает занесение символа в регистр данных или установку триггера 9, который устанавливается, если в управляющем символе имеется соотве ствующий признак. После выделения символа блок 5 выделения и идентиф кации символа со своего первого выхода 53 выдает в блок 1 и регист 3 сдвига сигнал сброса, который служит для отделения одного символ от другого. Кроме того, выделив управляющий символ, блок 5 выделен и идентифИ1 ации символа со своего пятого вьзхода 57 выдает в блок 8 управления движением головки разрешающий сигнал на сравнение адреса дорожки из счетчика 7 адреса дорожки с адресом дорожки из регист ра 3 сдвига. Б зависимости от результата сравнения блок 8 управления движением головки выдает один из сигналов; Шаг назад, Шаг вперед, которые поступают соответственно с 17 или 18 выходов устройстЁа в пультовой накопитель, или вырабатывает сигнал сравнения, который с выхода 51 блока 8 управления движением головки поступает на второй вход блока 5 выделения и игзнтификдции символа. Выделив символ данных, блок 5 .выделения и идентификации символа со своего четвертого выхода 56 выдает сигнал в счетчик б символов на увеличение содержимого счет- чика б символов на единицу, со своего третьего выхода 55 выдает сигнал в регистр 4 данных, разрешающий занесение данных из регистра 3 в регистр 4 данных, и своего шестого выхода выдает на выход 16 устройства строб передачи, который поступает в загружаемый процессор . и служит признаком того, что символ данных подготовлен устройством управления загрузкой микропрограмм для передачи в процессор. При этом содержимое регистра 4 данных через выход 14 данных устройства передается в загружаемый процессор. Счетчик 6 СИМВОЛОВ считает цринятые символы данных. Он содержит гп разрядов. В начальном состоянии содержимое счетчика б символов равно нулю. После приема 2 символов данных счетчик б символов снова сбрасывается в нулевое состояние и вырабатывает сигнал переноса, который поступает в счетчик 7 адреса дорожки для увел ченкя адреса дорожки на единицу, на первый вход элемента И 10 для разрешения выработки сигнала Конец передачи, в блок 5 выделения и идентификации символа . для сброса его в исходное состояние. Элемент И 10 вырабатывает сигнал Конец передачи при наличии двух условий: установленного триггера 9 и наличия ригнала переноса из счетчика 6 символов. Сигнал с выхода элемента И 10 поступает через выход 15 устройства в загружаемый процессор и сообщает ему, что весь массив микропрограмм передач загружен . Счетчик 7 адреса дорожки служит для указания адреса дорожки, с которой необходимо считывать информацию в данный момент времени. В начале загрузки микропрограмм с входа 13 в счетчик 7 адреса дорожки заносится начальный адрес дорожки, начиная с которого располагается загружаемый массив NMKponporpaMM. Дсшьнейшем содержимое счетчика 7 адреса дорожки увеличивается на ед ницу сигналом переноса счетчика б символов, поступающим на счетный вход счетчика 7 адреса дорожки. Блок 2 синхронизации (фиг. 2) работает следующим образом.(см. фиг. 6., на которой показана временная диаграмма работы блока 2 синх.ронизаци. В начальный момент времени первый 20 и второй 21 триггеры сброшены, третий триггер 22 установлен а все разряды счетчика 19 находятс в единичном состоянии. По временно му импульсу, поступающему из пультового накопителя через первый вход 11 устройства на вход блока, . и по установленному третьему тригг ру 22 устанавливается первый триггер 20. По установленному первому триггеру 20 устанавливается второй триггер 21. По установленному второму триггеру 21 и сигналу с генератора 33 тактовых импульсов, кото рый вырабатывает серию импульсов со скважностью единица, второй элемен И 24 вырабатывает сигнал, который сбрасывает третий триггер 22 и раз решает увеличение содержимого счет :Чика 19 на единицу. По сброшенноь третьему триггеру 22 сбрасывается первый триггер.20. Все время, пока установлен второй триггер 21, по сигналам с генератора 33 тактовых импульсов счетчик 19 увеличивает свое содержимое на единицу. По отсутствию сигналов на первом, втором, третьем выходах счетчика 19 . и по наличию, сигнала на выходе гене ратора 33 тактовых импульсов четвер тый элемент И вырабатывает синхросигнал СИ 1, который через первый выход 35 блока поступает в блок 1 и На вход регистра 3 сдвига По-отсутствию сигналов на втором и треть ем выходах счетчика 19 и по наличию сигналов на первом выходе счетчика 19 и на выходе генератора 33 тактовых импульсов пятый элемент И вырабатывает синхросигнсш СИ 2, который через четвертый выход 38 блока поступает в блок 5 выделения и идентификации символа. По наличи1 сигналов на первом и втором счетчика 19 и при отсутствии сигнала на третьем выходе счетчика 19 или при наличии сигнала на третьем выходе счетчика 19 и отсутствию сигнала на втором выходе счет :чика 19 шестой 28 и седьмой 29 элементы И и элёмент.ИЛИ 32 вырабатывают синхросигнал СИ 3, который со второго выхода 36 блока поступает в блок 1 к в блок 5 выделения и идентификации символа. По наличию сиг, налов на втором и третьем выходс1Х счетчика 19 и выходе генератора 33 тактовых импульсов и по.отсутствию сигнала на первом выходе счет- . чика 19 восьмой элемент И 30 вырабатывает синхросигнал СИ 4, который чере:з пятый выйод 34 блока поступает в блок 5 выделения и идентификации символа. По наличию сигналов на первом, втором и третьем выходах счетчика 19 и отсутствию сигнала на выходе генератора 33 тактовых импульсов девятый элемент И вырабатывает сигнал установки третьего триггера 22. Установленный третий триггер 22 выдает через третий выход 37 блока синхронизирующий сигнал СИ 5, который поступает в блок 1 и блок 5 выделения и идентификации символа. По единичному состоянию третьего триггера 22, нулево состоянию первого триггера 20 и отсутствию сигнала с выхода гене ратора 33 тактовых импульсов первый элемент И 23 вырабатывает сигнал сброса второго триггера 21. По нулевому состоянию второго триггера 21 и сигналу с выхода генератора 33 тактовых импульсов третий элемент И 25 вырабатывает сигнал, который устанавливает все разряды счетчика 19 в единицу. Одновременно нулевое состояние втоЕюго триггера 21 запрещает выработку сигнала счета вторым элементом И 24. Блок 5 выделения и идентификации символа (фиг. З) работает следующим образом. По заднему фронту синхросигнала СИ 1 происходит сдвиг информации в регистре 3 сдвига на одну позицию. Наличие единицы в ( h + 1)-ом разряде говорит о том, что в регистре 3 имеется полный символ. Поэтому при наличии единицы в (и+ 1)-м разряде регистра 3, поступающей с выхода регистра 3 через пятый вход 52 блока 5 выделения и идентификации Символа на) -вход первого триггера, по переднему фронту синхросигнала СИ 2, поступсшлцему на шестой вход 38 блока, устанавливается первый триггер 40. Первый символ является управляющим. В нем имеется адрес текущей дорожки. В случае совпадения адреса текущей дорожки с искомым, «лок 8 управления движением головки вырабатывает разрешающий сигнал, ко торый поступает на второй вход 51 блока 5 выделения и идентификации символа. Так как в начальный момен1г времени третий триггер 42 находится в нулевом состоянии, то на выходе первого элемента И 43 имеется единичное состояние и по переднему 4)ронту синхросигнала СИ 3, поступающему на третий вход 36 блока, устанавливается второй триггер 41. По установленным первому 40 и второму 41 триггерам и по синхросигналу СИ 3 третий элемент И 45 вырабатывает сигнал занесения управляющего символа, который с третьего выхода 55 блока 5 выделения и идентификации символа поступает на -вход триггера 9, разрешая его установку при наличии признака последней дорожки в управляющем симвое. По установленному второму тригге ру 41 и сиыхросигналу СН 4,поступаюему на седьмой вход 34 блока, устанавливается третий триггер 42. По установленному первому триггеру 40 и по синхросигналу СИ 4 пятый элемент И 47 вырабатывает сигнал, поступающий через первый выход 53 блока в блок 1 и регистр 3 для их сброса.

Если блок 8 управления движением головки не вырабатывает разрешаюего сигнала, поступающего на второй вход 51 блока 5 выделения и идентиикации символа, второй 41 и треий 42 триггеры не устанавливаются. По сброшенному третьему 42 и второу 41 триггерам элемент .ШИ-НЕ 39 вырабатывает разрешающий сигнал, и по единичному сигналу с выхода пятого элемента И 47 седьмой элемент И 49 вырабатывает управляющий сигнал, который через пятый выход 57 блока 5 выделения и идентификации символа поступает на вход разрешения блока 8 управления движением головки.

По синхросигналу СИ 5, поступающему на четвертый вход 37 блока, первый триггер 40 сбрасывается. , Сброшенный первый триггер 41 запрещает выработку единичного сигнала первым элементом И 43. Поэтому по переднему фронту следующего синхросигнала СИ 3, поступающему на третий вход 36 блока, второй триггер 41 сбрасывается. При наличии следующей единицы в ( h -f 1) -м разряде регистра 3 по переднему фронту синхросигнала СИ 2, поступающему на шестой вход 38 блока, первый триггер 40 устанавливается вновь. При этом имеющийся в регистре 3 символ является символом данных. Установленный третий триггер 42 своим инверсным выходом запрещает выработку единичного сигнала первым элементом И 43. Поэтом по синхросигналу СИ 3, пост пающему на третий вход 36 блока второй триггер 41 не установится. По установленным первому 40 и третьему 42 триггерам и син::росигналу СИ 2 второй элемент И 44 вырабатывает сигнал, который через четвертый выход 56 блока 5 выделения и идентификации символа поступает на. счетный Bxofi счетчика 6 символов, для увеличения его содержимого на единипу. По установленным первому

4 и и третьему 42 триггерам и синхросигналу СИ 3 третий элемент И 45 вырабатывает сигнал, который через третий выход 55 блока и Идентификации символа поступает на С-вход регистра 4 данных, разрешая занесение данных из регистра 3 в регистр

4данных. По установленным первому 40 и третьему 42 сброшенному второ му 41 триггерам и синхросигналу

0 си 4 шестой элемент И 48 вырабатыва ет стробирующий сигнал, который через шестой выход и выход 16 устройства поступает в загружаемый процессор, сообщая ему, что символ данных готов для передачи.

Блок 8 управления движением головки (фиг. 4) работает следующим образом.

На вход первого адреса дорожки

Q блока поступает адрес дорожки из регистра 3. На вход второго адреса. дорожки блока поступает адрес дорожки из счетчика 7 адреса дорожки. Схема сравнения 58 производит срав5 нениё этих адресов и выдает один из трех сигналов: Равно, Больше, Меньше. В случае равенства адресов единичный сигнал с выхода схемы 58 сравнения через выход 51 блока поступает на второй вход блока

5выделения и идентификации символа, На вход 57 разрешения блока 8 управления движением головки поступает из блока 5 выделения и идентификации символа стробирующий сигнал-,

5 который в случае несравнения адресов через первый 59 или второй 60 элемент И разрешает установку соответственно первого 61 или второго 62 триггеров. Сигналы с выходов второго 61 и третьего 62 триггеров соответственно через выход блока, соединенный с выходом 17 устройст- .... ва, и через выход блока, соединенный с выходом 18 устройства, поступают

5 в пультовый накопитель. По этим

сигналам пультовый накопитель перемещает головку соответственно на одну дорожку назад или на одну дорожку вперед. На вход Начало доQ рожки блока через вход 12 устройства с пультового накопителя поступает сигнал Начало дорожки, по которому сбрасывается первый 61 или второй 62 триггер.

Блок выделения временных битов

5 и битов данных работает следующим образом.

Из пультового накопителя через вход 11 устройства на первый вход блока 1 поступают импульсы данных.

0 Наличие импульса данных в момент времени СИ 3 говорит о том, что соответствующий бит данных равен единице. Отсутствие импульса данных в момент времени СИ 3 говорит о

5 том, что соответствующий бит данных равен нулю. При наличии импулБ са данных И синхросигнала СИ 3, который поступает из блока 2 синхронизации на третий вход 36, устанавливается первый триггер 65. По синхросигналу СИ 5, поступающему на четвертый вход 37 бдока 1 из блока 2 синхронизации, состояние первого триггера переписывается во второй триггер 66, Сигнал с выхода второго триггера 66 через выход 67 поступаетha вход данных регистра 3. По следующему синхросигналу СИ 1 состояние второго триггера 66 вдвигается в регистр 3. Одновременно по синхросигналу СИ 1, поступающему на вход 35, сбрасывается первый триггер 65. Когда в регистре 3 накопится полный символ,блок 5 выделения . и идентификация символа вьвдает на пятый вход 53 сигнал сброса, который сбрасывает второй триггер 66.

В предлагаемом устройстве существенно упрощается алгоритм связи с процессором, а также блок управления- пультовым накопителем. За счет изменения работы блока синхронизаци изменения формата записей на магнитном носителе, в результате которого изменяется принцип выделения и идентификации символа, добиваются экономии обб5:/дования. За счет изменения гшгоритма связи с процессором сокращается количество шин между процессором и устройством загрузки микропрограмм, а также упрощается оборудование, определяющее момент окончания загрузки микропрограмм.

Благодаря сокращенному объему оборудования предлагаемое устройство потребляет меньше электроэнергии, занимает меньше площади, обладает большей надежностью, требует меньше времени на обслуживание...

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство управления загрузкой микропрограмм | 1983 |

|

SU1136175A2 |

| Устройство управления загрузкой микропрограмм | 1983 |

|

SU1119019A1 |

| Устройство для сопряжения ЭВМ с внешним устройством | 1986 |

|

SU1377864A1 |

| Устройство для контроля переписи информации перезагружаемой управляющей памяти процессора | 1981 |

|

SU1008746A1 |

| Устройство управления накопителями на магнитных дисках | 1982 |

|

SU1053143A1 |

| Устройство приема информации волоконно-оптической линии связи | 1990 |

|

SU1753605A1 |

| Устройство контроля электропитания процессора | 1983 |

|

SU1096649A1 |

| Устройство для отображения информации | 1986 |

|

SU1441450A1 |

| Устройство для запоминания состояний процессора | 1985 |

|

SU1278858A1 |

| Устройство для сбора данных о работе ЭВМ | 1982 |

|

SU1121679A1 |

1. УСТРОЙСТВО УПРАВЛЕНИЯ ЗАГРУЗКОЙ МИКРОПРОГРАММ, содержащее регистр сдвига, счетчик символов, регистр данных и блок выделения временных битов и битов данных, первый вход которого подключен к информационному входу устройства, а первый выход - к информационному входу регистра сдвига, выход данных которого соединен с входом данных регистра данных, выход которого подключен к выходу данных устройства, отличающееся тем, что, с целью сокращения аппаратурных затрат, в него введены блок синхронизации, блок выделения и идентификации символов, счетчик адреса дорожки, блок управления движением головки, триггер и злемент И, причем выход счетчика символов подключен к первому входу блока выделения и идентификации символов, к первому входу счетчика адреса дорожки и первому входу злемента И, выход которого соединен с выходом конца передачи массива устройства, а второй вход - с выходом триггера, вход блока синхронизации подключен к информационном входу устройства, первый выход - к второму входу блока выделения временных битов и к управляющему входу регистра сдвига, второй выход - к третьему входу блока выделения временных битов и битов данных, третий выход - к четвертому входу блокавьщеления временных битов и битов данных, пятый вход которого соединен с входом сброса регистра Сдвига и первым выходом блока выделения и идентификации символа, второй выход которого подключен к установочному входу триггера/ вход данных которого соединен с входом первого адреса дорожки блока управления движением головки и выходом регистра сдвига, третий выход блока выделения и идентификации символа подключен к разрешающему входу регистра данных, четвертый выход - к входу счетчика символов, пятыП выход - к входу 1 (Л разрешения блока управления движением головки, шестой выход - к эыходу строба передачи устройства, : второй вход - к выходу сравнения блока-управления движением головки, третий вход - к второму выходу блока синхрониаации, четвертый вход - к третьему выходу блока синхронизации, пятый вход -к выходу признака регистра сдвига, шестой вход - к четвертому выходу блока синхронизации, седьмой вход к пятому выходу блока синхронизации, второй вход счетчика адреса дорожки подключен к входу иачальнб.Го адреса устройства, а выход - с входом второго адреса дорожки бло-: ка управления движением головки, вход Начало дорожки которого соединен с входом Начало дорожки устройства, а,выходы Шаг назад и Шаг вперед - с выходами Шаг назад и Шаг вперед соответственно устройства. 2. Устройство по п. 1, отличающееся тем, что блок синхронизации содержит первый, второй и третий триггеры, счетчик.

/7

Г/

ft.X

n

rтз.

37

ГТ

35 38 36 JS

ГТ

г.6

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Теплица | 1983 |

|

SU1258972A1 |

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Внешние устройства ЭВМ | |||

| М., Мир, 1977, с | |||

| Способ применения поваренной соли в нагревательной закалочной ванне при высоких температурах | 1923 |

|

SU412A1 |

| , | |||

Авторы

Даты

1983-09-15—Публикация

1982-03-16—Подача