1

Изобретение относится к автоматике и вычислительной технике, в частности к пороговым логическим элементам.

Известен многопороговыП логический элемент, содержащий линейный сумматор, подключенный к резистивному делителю, соединенному с многопороговым дискриминатором 1.

Недостатком известного многопорогового логического элемента является высокая потребляемая мощность.

Известен многопороговый логический элемент, содержащий линейный сумматор, состоящий из входных диодов и реэисторной матрицы, подключенный через разделительные диоды к резистивному делителю, соединенному с одниг ш входами логических элементов И-НЕ, образующих многопороговый дискриминатор, второй вход каждого из которых соединен с выходом последующего логического элемента И-НЕ fZJ

Недостатком этого многопорогового элемента является то, что входные сигналы в форме положительных потенциалов запирают в любых комбинациях входные диоды, входящие в состав .линейного сумматора. Этим обеспечивается переключение тока от источника питания в цепь резистивного делителя. При поступлении на входы многопорогового логического элемента

5 большого числа логических переменных равных единице, потенциал на выходе линейного сумматора возрастает. Это приводит к уменьшению степени насыщения разделительных диодов, входя 0 тих в состав линейного сумматора, из-за уменьшения разности потенциалов между анодом-и катодом диода. Это, в свою очередь, приводит к увеличению погрешности и уменьшению

5 линейности суммирования из-за изменения тока через диоды. Кроме,того, даже в этом случае,.когда входные сигналы многопорогового логического элемента равны нулю, имеет место

20 потребление мощности линейным сумматором из-за протекания токов черрз входные диоды.

Цель изобретения - уменьшение потребляемой мощности, повышение линейности и уменьшение погрешности линейного сумматора.

Для достижения поставленной цели многопороговый логический элемент, содержащий резистивный делитель,

30 выходы которого соединены с одними

входами логических элементов И-НЕ, образуюиих многопороговый дискриминатор, второй вход каждого из которых соединен с выходом последующего логического элемента , содержит транзисторы, эмиттеры которых подключены к отрицательному полюсу источника питания, базы подключены к выходным клеммам многопорогового элемента, а коллекторы через резисторы соединены с выходом резистивного делителя, вход которого подключен к положительному полюсу источника питания.

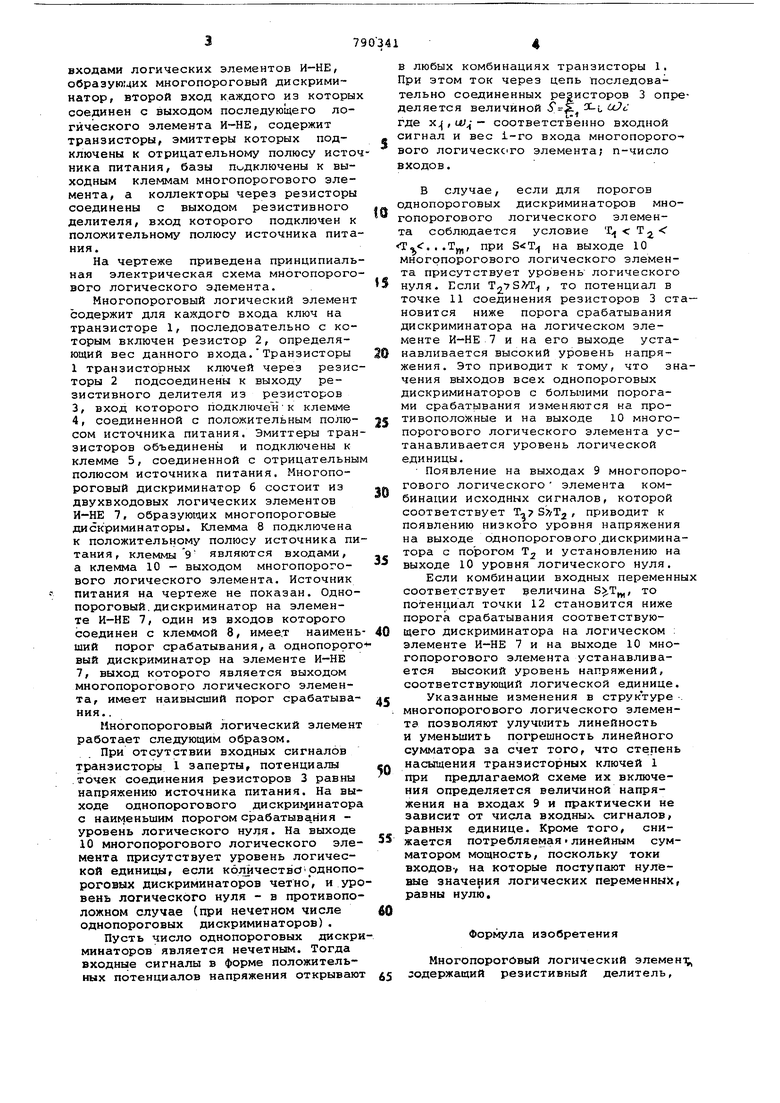

На чертеже приведена принципиальная электрическая схема многопорогового логического элемента.

Многопороговый логический элемент содержит для каждого входа ключ на транзисторе 1, последовательно с которым включен резистор 2, определяющий вес данного входа.Транзисторы 1 транзисторных ключей через резисторы 2 подсоединены к выходу резистивного делителя из резисторов

3,вход которого подключат К клемме

4,соединенной с положительным полюсом источника питания. Эмиттеры транзисторов объединены и подключены к клемме 5, соединенной с отрицательным полюсом источника питания. Многопороговый дискриминатор 6 состоит из двухвходовых логических элементов

И-НЕ 7, образующих многопороговые дискриминаторы. Клемма 8 подключена к положительному полюсу источника питания, клеммы э являются входами, а клемма 10 - выходом многопорогового логического элемента. Источник питания на чертеже не показан. Однопороговый, дискриминатор на элементе И-НЕ 7, один из входов которого соединен с клеммой 8, имее.т наименьший порог срабатывания, а однопоррговый дискриминатор на элементе И-НЕ 7, выход которого является выходом многопорогового логического элемента, имеет наивысший порог срабатывания. .

Многопороговый логический элемент работает следующим образом.

При отсутствии входных сигналов транзисторы 1 заперты, потенциалы .точек соединения резисторов 3 равны напряжению источника питания. На выходе однопорогового дискри 4инатора с наименьшим порогом срабатывания уровень логического нуля. На выходе 10 многопорогового логического элемента присутствует уровень логической единицы, если к6л 1чествс рднопороговых дискриминаторов четно, и уровень логического нуля - в противоположном случае (при нечетном числе однопороговых дискриминаторов).

Пусть число однопороговых дискриминаторов является нечетным. Тогда входные сигналы в форме положительных потенциалов напряжения открывают

в любых комбинациях транзисторы 1. При этом ток через цепь последовательно соединенных резисторов 3 опрделяется величиной S LL uJc где х., соответственно сигнал и вес i-ro входа многопорогового логическсго элемента; п-число входов.

В случае, если для порогов однопороговых дискриминаторов многопорогового логического элемента соблюдается условие Т Т...Т, при на выходе 10 многопорогового логического элемента присутствует уровень логического нуля. Если , то потенциал в точке 11 соединения резисторов 3 стновится ниже порога срабатывания дискриминатора на логическом элементе И-НЕ 7 и на его выходе устанавливается высокий уровень напряжения. Это приводит к тому, что знчения выходов всех однопороговых дискриминаторов с большими порогами срабатывания изменяются на противоположные и на выходе 10 многопорогового логического элемента устанавливается уровень логической единицы.

Появление на выходах 9 многопорогового логического элемента комбинации исходных сигналов, которой соответствует Т., , приводит к появлению низкого уровня напряжения на выходе однопорогового дискриминатора с порогом Tj и установлению на выходе 10 уровня логического нуля.

Если комбинации входных переменн соответствует величина , то потенциал точки 12 становится ниже порога срабатывания соответствующего дискриминатора на логическом : элементе И-НЕ 7 и на выходе 10 многопорогового элемента устанавливается высокий уровень напряжений, соответствующий логической единице.

Указанные изменения в структуре многопорогового логического элемента позволяют улучшить линейность и уменьшить погрешность линейного сумматора за счет того, что степень насыщения транзисторных ключей 1 при предлагаемой схеме их включения определяется величиной напряжения на входах 9 и практически не зависит от числа входных сгигналов, равных единице. Кроме того, снижается потребляемая линейным сумматором мовдно.сть, поскольку токи входов-, на которые поступают нулевые значения логических переменных, равны нулю.

Формула изобретения

Многопороговый логический элемент;, содержащий резистивный делитель,

выходы которого соединены с одними входами логических элементов И-НЕ, обраэую1цих многопороговый дискриминатор, второй вход каждого из которых соединен с выходом последующего логического элемента И-НЕ, отличаюмийся тем, что, с целью уменьшения потребляемой мощности, повышения линейности и уменьшения погремнос.-и линейного сумматора, он содержит транзисторы, эмиттеры которых подключены к отрицательному полюсу источника питания

базы подключены ко входным клеммам многопорогового элемента, а коллекторы через резисторы соединены с выходом резистивного делителя, вход которого подключен к положительному полюсу источника питания.

Источники информации, принятые во внимание при экспертизе

1.Авторское свидетельство СССР 608266, кл. Н 03 К 19/42, 1978.

2.Авторское свидетельство СССР 538490. кл. Н 03 К 19/12, 1977.

| название | год | авторы | номер документа |

|---|---|---|---|

| Многопороговый логический элемент | 1988 |

|

SU1575307A1 |

| Многопороговый логический элемент | 1983 |

|

SU1132366A2 |

| Многопороговый логический элемент четности | 1980 |

|

SU928653A1 |

| Многопороговый логический элемент | 1982 |

|

SU1042183A1 |

| МНОГОПОРОГОВЫЙ ЛОГИЧЕСКИЙ ЭЛЕМЕНТ | 2000 |

|

RU2189110C2 |

| Многопороговый логический элемент | 1979 |

|

SU788384A1 |

| Многопороговый логический элемент четности | 1977 |

|

SU660261A2 |

| Многопороговый логический элемент | 1990 |

|

SU1728966A2 |

| Многопороговый логический элемент | 1977 |

|

SU705684A1 |

| Многопороговый логический элемент четности | 1980 |

|

SU900455A2 |

Авторы

Даты

1980-12-23—Публикация

1979-01-25—Подача