I

Изобретение относится к автомати|ке и вычислительной технике, в частности к пороговым логическим элементам.

По основному авт. св. № известен многопороговый логический элемент четности, содержащий линейный сумматор, состоящий из входных диодов и резисторной матрицы, подключенный через разделительные диоды к резистивному делителю и многопороговому дискриминатору, выполненному в виде нескольких взаимосвязанных одно пороговых дискриминаторов на двухвходовых элементах И-НЕ. В цепь обратной связи многопорогового элемента включен RS-триггер на логических элементах И-НЕ,один вход триггера соединен с выходом однопорогового дискриминатора с наибольшим порогом срабатывания, второй вход соединен с источником стробирующего сигнала, а выход триггера подключен к одному из входов линейного сумматора |1.

Недостатком многопорогового логического элемента четности является то, что перед подачей на входы линей ного сумматора очередного двоичного набора RS-триггер, входящий в состав многопорюгового элемента, должен быть установлен в исходное (нулевое) состояние. Это сужает функциональные возможности, исключает возможность применения подобного многопорогового логического элемента четности в асинхронных схемах цифровых устройств.

Целью изобретения является расши-рение функциональных возможностей, т.е. обеспечение возможности использования многопорогового логического элемента в асинхронных схемах цифровых устройств.

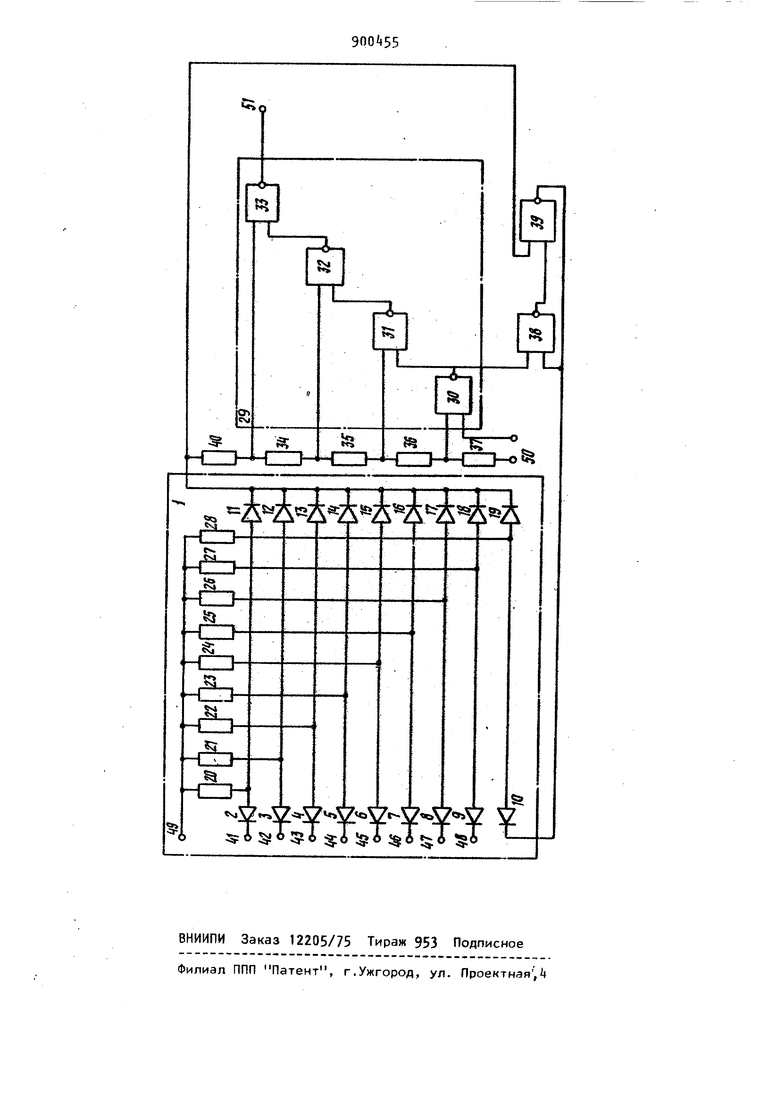

Поставленная цель достигается тем, что в многопороговом логическом элементе четности второй вход RSтриггера соединен с выходом линейного сумматора и через дополнительный резистор подключен к резистивному делителю. Указанные изменения сделали возможным использование многопорогового логического элемента четности в асинхронных схемах цифровых устройст за счет автоматического возврата RSтриггера в исходное состояние в тех случаях, когда последовательно сменяющие на входах линейного сумматора двоичные наборы удовлетворяют условиямПI S X uj 7, ч и S X . uj i -А i-l соответственно о Многопороговый логический элемент четности содерх ит линейный сумматор 1 , состоящий из диодов 2-19 и резисторов 20-28, образующих резис торную матрицу, многопороговый дискриминатор 29, состоящий из двухвхо.довых логических элементов И-НЕ 3033, резистивный делитель из резисторов , RS-триггер, образованный логическими элементами И-НЕ 38 и 39 и дополнительный однопороговый дискриминатор, состоящий из логического элемента И-НЕ 39 и резистора 40. На входы линейного сумматора 1 поданы входные сигналы, на входы 9 ИдЗО - напряжение питания., Выходные сигналы снимаются с выхода 51. Работает многопороговый логический элемент четности следующим образом. Значения весовых коэффициентов основных входов линейного сумматора равны единице. Вес входа многопорогового элемента, связанного с нулевым выходом RS-.триггера равен Ц, порог срабатывания однопорогового диск риминатора на элементе И-НЕ 39 равен , а на элементах 30 - 33 соответственно 8, 7, 6, 5; В исходном состоянии диоды 2-9 связанные со входами , проводят ток от источника питания -через соответствующие резисторы 20-27. Ток через резистор 28 от положительного полюса источника питания, диод 19 и резистор Q поступает в цепь после довательно, соединенных резисторов и далее к отрицательному полюсу источника питания. На выходе 51 многопорогового логического элемента и выходе элементов И-НЕ 30-33 в этом случае присутствует уровень логической единицы, RS-триггер находится в нулевом состоянии и на выходе элемента И-НЕ 39 присутствует потенциал логической единицы. Входные сигналы 0 форме положительных потенциалов напряжения запирают в любых комбинациях диоды 2-9. Если положительный потенциал присутствует только на одном из входов линейного сумматора 1, то соответствующий диод запирается и ток от источника питания через соответствующие резисторы 20-2/ и соответствующие диоды 11-18 переключается в цепь резисторов lO, . При этом потенциал на входе элемента И-НЕ 331 связанном с резистивным делителем, становится достаточным для появления на выходе 51 низкого уровня напряжения, соответствующего логическому нулю. При наличии высоких потенциалов на двух или трех входах линейного сумматора 1, соответствующие диоды 2-8 запираются и ток через резисторы 20-27 и диоды 11-19 переключается в цепь резисторов kQ, Это приводит к срабатыванию дискриминаторов на логических элементах 32 и 33 или 31 - 33, что вызывает появление на выходе 51 многопорогового логического элемента .четности высокого или низкого уровня напряжения, соответствующего логической единице или нулю. Ток от источника питания через резистор 28 и диод 19 протекает через резисторы 40, до тех пор, пока RS-триггер на элементах 38-39 не изменит своего состояния на противоположное. А это произойдет в том случае, ког.яа ко входам линейного сумматора 1 поступит четыре или более единичных логических сигналов. При этом на выходе логического элемента 30, имеющего значение порога Т-8, установится низкий потенциал, триггер изменит свое состояние на противоположное. После этого ток через резистор 28 от источника питания переключится в цепь диода 10, а на выходе 51 многопорогового логического элемента для реализации функции четности установится значение сигнала, определяемое входным воздействиемо Возврат RS-триггера в исходное состояние осуществляется в том случае, если последовательно сменяющие на входах линейного сумматора 1 двоичные наборы содержат четыре или более единиц и менее четырех единиц. При этом величина напряжения на связанном с выходом линейного сумматора входе логического элемента И-НЕ 39 оказывается недостаточной для поддержания на выходе логического элемента И-НЕ 39 низкого уровня напряжения соответствукицего логическому нулю. Это приводит к возврату RS-триггера в исходное (нулевое)состояние, запиранию диода 10 и переключению тока через резистор 23 в цепь последовательно соединенных резисторов 40, . На выходе 5 многопорогового логического элемента четности установится сигнал, определяемый входным воздействием.

Таким образом, организация однопорогового дискриминатора с порогом срабатывания Т- на логическом элементе И-НЕ 39, входящим в состав RS-триггера, сделала возможным автоматический возврат триггера в исходное состояние, если последовательно сменяющие на входах линейного сумматора двоичные наборы содержат четыре и более единиц и менее четырех единиц.

Формула изобретения

to Многопороговый логический элемент яетности по авт. св. К , о т ч личающийся тем, что, с 14елью расширения функциональных возможностей в нем, второй вход ЯЗ-триг s гера соединен с выходом линейного сумматора и через дополнительный резистор подключен к реэистивнсму делителю.

Л Источники информации,

принятые во внимание при экспертизу

1. Авторское свидетельство СССР W , кл. « 03 К 19/t2, 24.tt.75.

г

чЬ

ниэ

.-Ь

чЬ

| название | год | авторы | номер документа |

|---|---|---|---|

| Многопороговый логический элемент четности | 1980 |

|

SU928653A1 |

| МНОГОПОРОГОВЫЙ ЛОГИЧЕСКИЙ ЭЛЕМЕНТ | 2000 |

|

RU2189110C2 |

| Многопороговый логический элемент четности | 1976 |

|

SU608266A1 |

| Многопороговый логический элемент | 1985 |

|

SU1272499A2 |

| Многопороговый логический элемент четности | 1977 |

|

SU660261A2 |

| Многопороговый логический элемент четности | 1975 |

|

SU538490A1 |

| Многопороговый логический элемент | 1983 |

|

SU1132366A2 |

| Многопороговый логический элемент | 1979 |

|

SU788384A1 |

| Многопороговый логический элемент | 1977 |

|

SU705684A1 |

| Многопороговый логический элемент | 1988 |

|

SU1575307A1 |

V

3:6 si

Авторы

Даты

1982-01-23—Публикация

1980-05-28—Подача