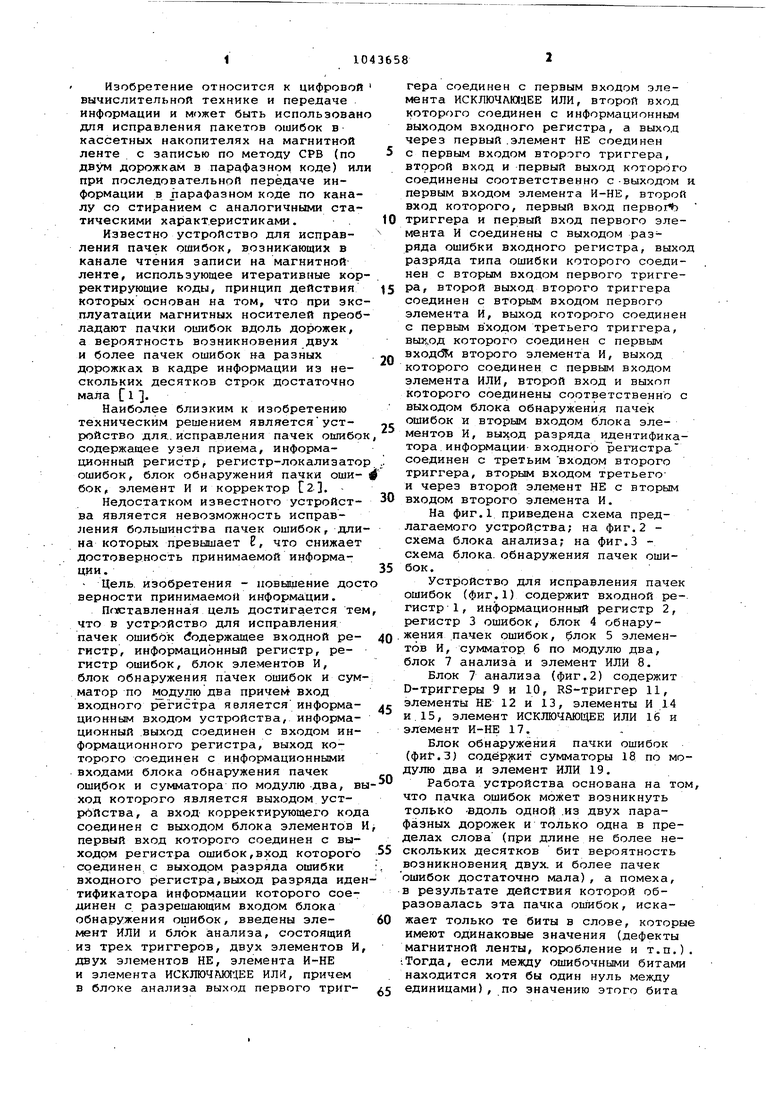

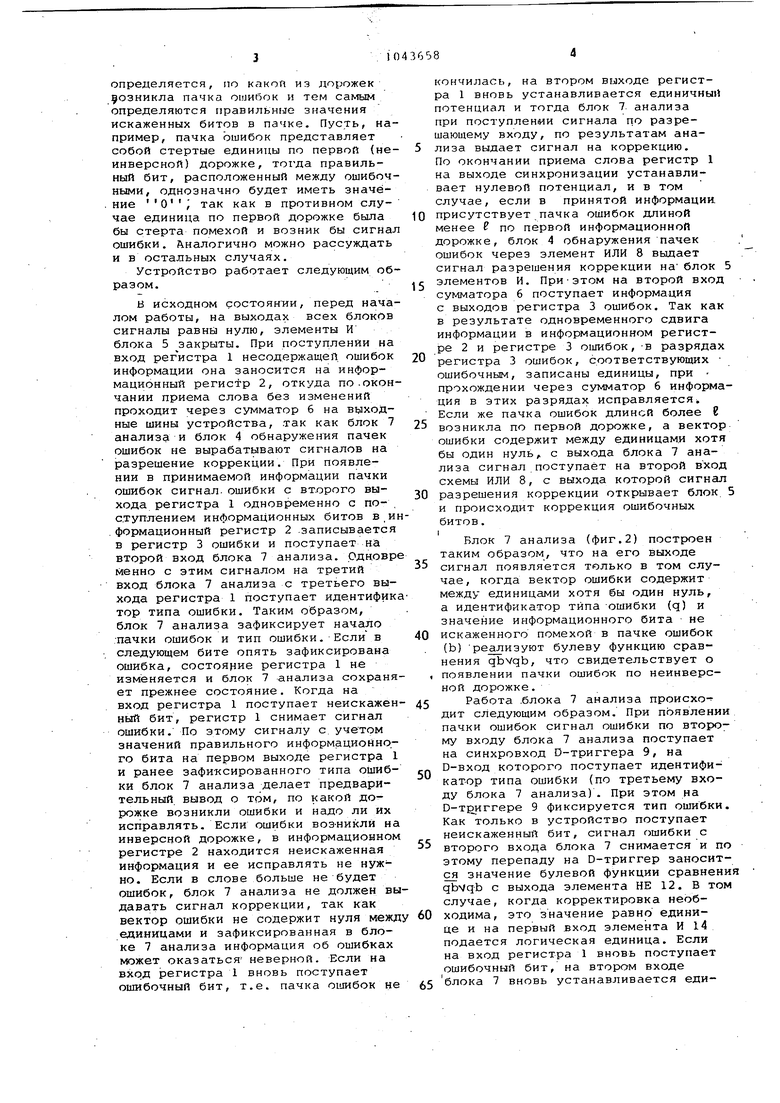

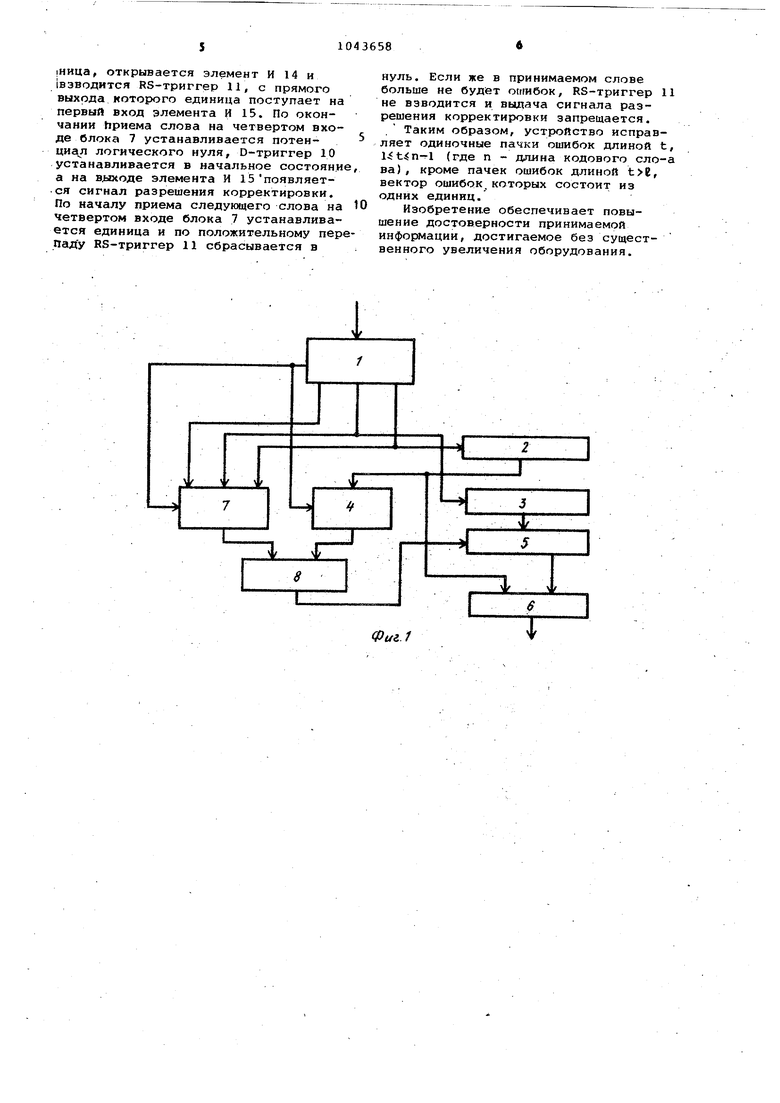

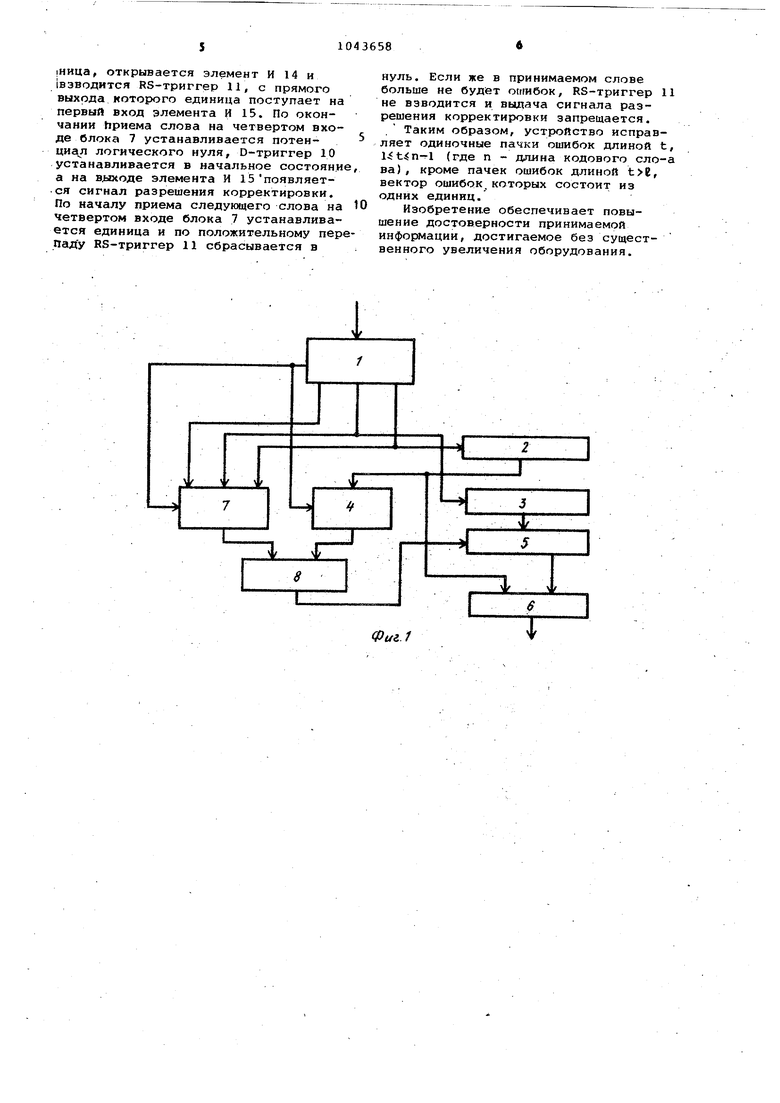

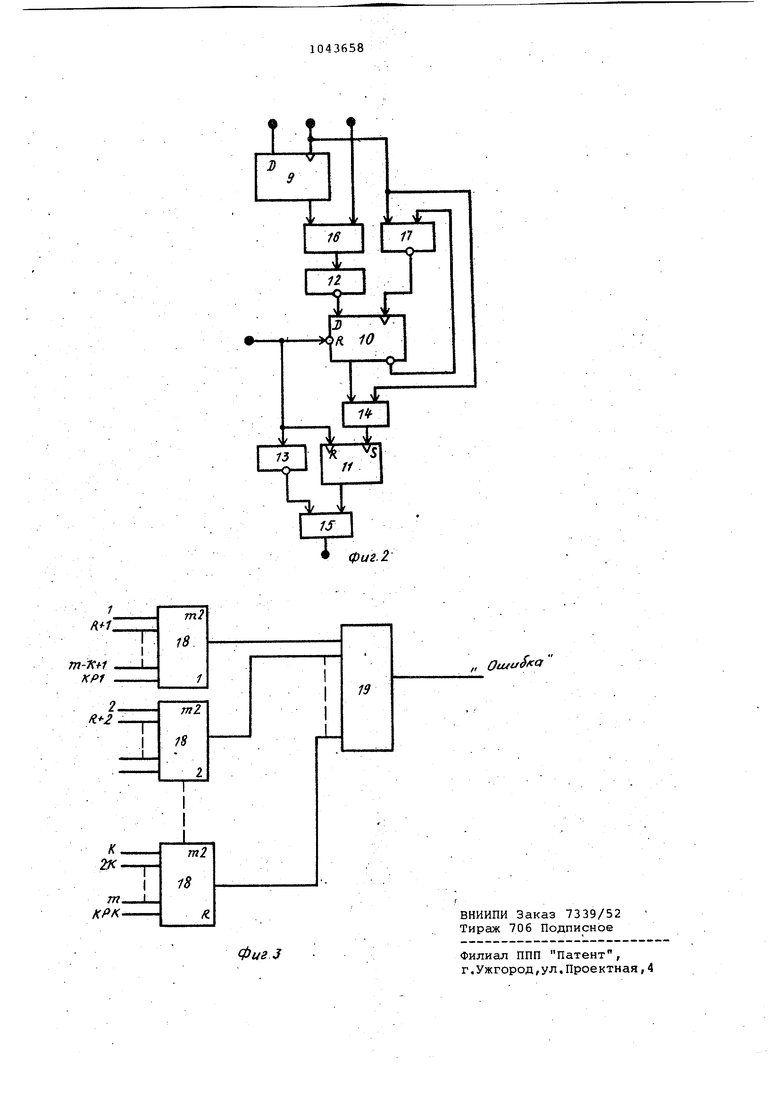

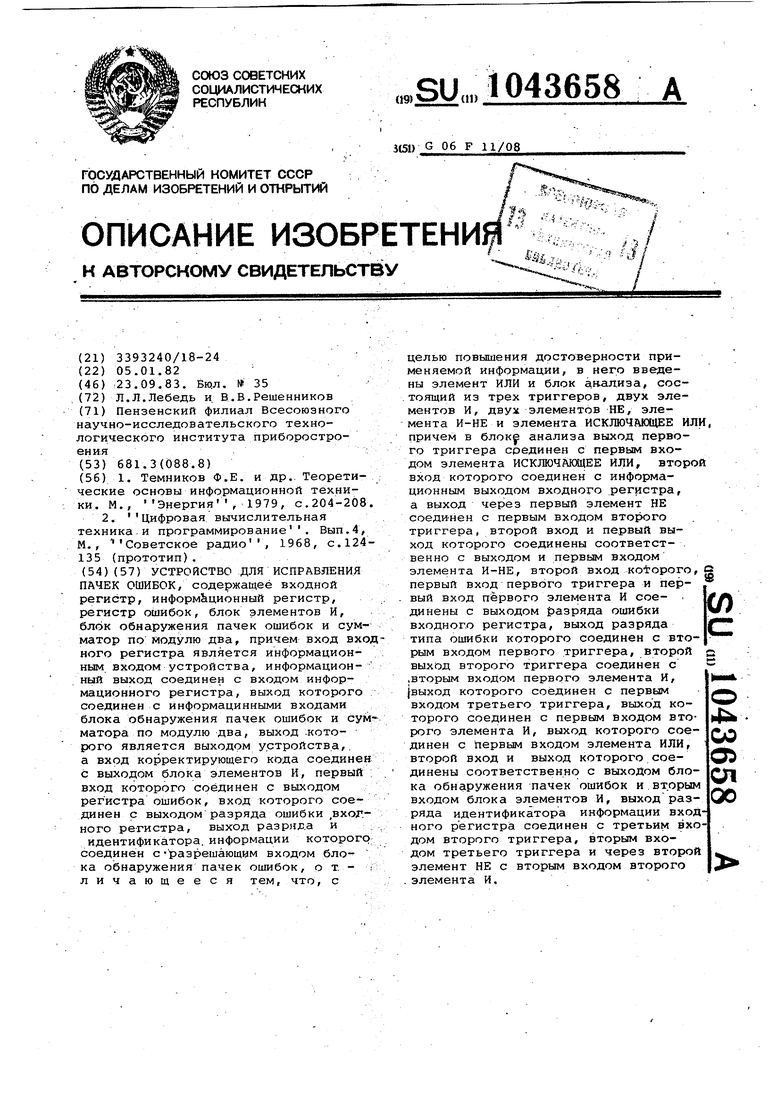

Изобретение относится к цифровой вычислительной технике и передаче информации и может быть использован для исправления пакетов ошибок вкассетных накопителях на магнитной ленте с записью по методу СРВ (по двум дорожкам в параФаэном коде) ил при последовательной передаче информации в рарафазном коде по каналу со стиранием с аналогичными статическими характеристиками. Известно устройство для неправления пачек ошибок, возникающих в канале чтения записи на магнитной ленте, использующее итеративные кор ректирующие коды, принцип действия которых основан на том, что при экс плуатации магнитных носителей преоб ладают пачки ошибок вдоль дорожек, а вероятность возникновения двух и более пачек ошибок на разных дорожках в кадре информации из нескольких десятков строк достаточно мала С1 . Наиболее близким к изобретению техническим решением являетсяустройство для,, исправления пачек ошибо содержащее узел приема, информационный регистр, регистр-локализато ошибок, блок обнаружений пачки ошибок, элемент И и корректор С2. Недостатком известного устройства является невозможность исправления большинства пачек ошибок, дли на которых превышает В, что снижает достоверность принимаемой информации . - Цель, изобретения - повышение дос верности принимаемой информации. Пгзставленная цель достигается те что в устройство для исправления пачек ошибок Содержащее входной регистр, информационный регистр, регистр ошибок, блок элементов И, блок обнаружения пачек ошибок и сум матор по модулю два причем вход входного регистра являетсяинформационным входом устройства, информационный выход соединен с входом информационного регистра, выход которого соединен с информационными входами блока обнаружения пачек ошцбок и сумматора по модулю два, в ход которого является выходом устройства, а вход корректирующего код соединен с выходом блока элементов первый вход которого соединен с выходом регистра ошибок,вход которого соединен с выходом разряда ошибки входного регистра,выход разряда иде тификатора информации которого соединен с разрешающим входом блока обнаружения ошибок, введены элемент ИЛИ и блок анализа, состоящий из трех триггеров, двух элементов И двух элементов НЕ, элемента И-НЕ и элемента ИСКЛЮЧМЯДЕЕ ИЛИ, причем в блоке анализа выход первого триг.гера соединен с первым входом элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, второй вход которого соединен с информационным выходом входного регистра, а выход через первый .элемент НЕ соединен с первым входом второго триггера, второй вход и первый выход которого соединены соответственно с-выходом н первым входом элемента И-НЕ, второй вход которого, первый вход nepBort) триггера и первый вход первого элемента И соединены с выходом разряда ошибки входного регистра, выход разряда типа ошибки которого соединен с вторьлм входом первого триггера, второй выход второго триггера соединен с вторым входом первого элемента И, выход которого соединен с первым входом третьего триггера, выз,од которого соединен с первым входсЗ второго элемента И, выход которого соединен с первым входом элемента ИЛИ, второй вход и выхол которого соединены соответственно с выходом блока обнаружения пачек ошибок и вторым входом блока элементов И, выход разряда идентификатора информации- входного регистра соединен с третьим входом второго триггера, вторым входом третьегои через второй элемент НЕ с вторым входом второго элемента И. На фиг.1 приведена схема предлагаемого устройства; на фиг.2 схема блока анализа; на фиг.З схема блока, обнаружения пачек ошибок . Устройство для исправления пачек ошибок (фиг,1) содержит входной регистр 1, информационный регистр 2, регистр 3 ошибок, блок 4 обнаружения пачек ошибок, блок 5 элементов И, сумматор, б по модулю два, блок 7 анализа и элемент ИЛИ 8. Блок 7 анализа (фиг.2) содержит D-триггеры 9 и 10, RS-триггер 11, элементы НЕ 12 и 13, элементы И 14 и.15, элемент ИСКЛЮЧАЮЩЕЕ ИЛИ 16 и элемент И-НЕ 17. Блок обнаружения пачки ошибок (фиГ.З) содёрясит сумматоры 18 по модулю два и элемент ИЛИ 19. Работа устройства основана на том, что пачка ошибок может возникнуть только -вдоль одной .из двух парафазных дорожек и только одна в пределах слова (при длине не более нескольких десятков бит вероятность возникновении двух, и более пачек ошибок достаточно мала), а помеха, в результате действия которой образовалась эта пачка ошибок, искажает только те биты в слове, которые имеют одинаковые значения (дефекты магнитной ленты, коробление и т.п.). -Тогда, если между ошибочными битами находится хотя бы один нуль между единицами), по значению этого бита

определяется, no какой из дорожек возникла пачка О1,ои6ок и тем самым определяются иравильние значения искаженных битов в пачке. Пусть, например, пачка ошибок представляет собой стертые единицы по первой (неинверсноП) дорожке, тохда правильный бит, расположенный между ошибочными, однозначно будет иметь значеО

ние

так как в противном случае единица по первой дорожке была бы стерта помехой и возник бы сигнал ошибки. Аналогично можно рассуждать и в остальных случаях.

Устройство работает следующим образом.

Б исходном состоянии, перед началом работы, на выходах всех блоков сигналы равны нулю, элементы И блока 5 закрыты. При поступлении на вход регистра 1 несодержащей ошибок информации она заносится на информационный регистр 2, откуда по .окончании приема слова без изменений проходит через сумматор 6 на выходные шины устройства, так как блок 7 анализа и блок 4 обнаружения пачек ошибок не вырабатывают сигналов на разрешение коррекции. При появлении в принимаемой информации пачки ошибок сигнал.ошибки с второго выхода регистра 1 одновременно с поступлением информационных битов в.и.формационный регистр 2 .записывается в регистр 3 ошибки и поступает на второй вход блока 7 анализа. Одновр менно с этим сигналом на третий вход блока 7 анализа с третьего выхода регистра 1 поступает идентификтор типа ошибки. Таким образом, блок 7 анализа зафиксирует начало пачки ошибок и тип ошибки. Если в следующем бите опять зафиксирована ошибка, состояние регистра 1 не изменяется и блок 7 анализа сохраняет прежнее состояние. Когда на вход регистра 1 поступает неискаженный бит, регистр 1 снимает сигнал ошибки. По этому сигналу с учетом значений правильного информационного бита на первом выходе регистра 1 и ранее зафиксированного типа ошибки блок 7 анализа делает предварительный вывод о том, по какой дорожке возникли ошибки и надо ли их исправлять. Если ошибки воз-никлй на инверсной дорожке, в информационном регистре 2 находится неискаженная информация и ее исправлять не нужно. Если в слове больше не будет ошибок, блок 7 анализа не должен выдавать сигнал коррекции, так как вектор ошибки не содержит нуля межд единицами и зафиксированная в б.поке 7 анализа информация об ошибках может оказаться неверной. Если на вход регистра 1 вновь поступает ошибочный бит, т.е. пачка ошибок не

кончилась, на втором выходе регистра 1 вновь устанавливается единичный потенциал и тогда блок 7. анализа при поступлении сигнала по разрешающему входу, по результатам анализа выдает сигнал на коррекцию. По окончании приема слова регистр 1 на выходе синхронизации устанавливает нулевой потенциал, и в том случае, если в принятой информации присутствует пачка ошибок длиной

0 менее Р по первой информационной дорожке, блок 4 обнаружения пачек ошибок через элемент ИЛИ 8 выдает сигнал разрешения коррекции на блок 5 элементов И. Приэтом на второй вход

5 cyjviMaTopa 6 поступает информация с выходов регистра 3 ошибок. Так как в результате одновременного сдвига информации в информационном регистре 2 и регистре 3 ошибок,-в разрядах

0 регистра 3 ошибок, соответствующих ошибочным, записаны единицы, при прохождении через сумматор 6 информация в этих разрядах исправляется Если же пачка ошибок длиной более Е

5 возникла по первой дорожке, а вектор ошибки содержит между единицами хотя бы один нульд с выхода блока 7 анализа сигнал поступает на второй вход схемы ИЛИ 8, с выхода которой сигнал разрешения коррекции открывает блок, 5

0 и происходит коррекция ошибочных битов.

Блок 7 анализа (фиг. 2) построен таким образом, что на его выходе

5 сигнал появляется только в том случае, когда вектор ошибки содержит между единицами хотя бы один нуль, а идентификатор типа -ошибки (q) и значение информационного бита не

0 искаженного помехой в пачке ошибок (Ь)реализуют булеву функцию сравнения qbvqb, что свидетельствует о появлении пачки ошибок по неинверсной дорожке.

Работа .блока 7 анализа происхо5дит с.ледующим образом. При появлении пачки ошибок сигнал ошибки по второму входу блока 7 анализа поступает на синхровход D-триггера 9, на D-вход которого поступает идентифи0катор типа ошибки (по третьему входу блока 7 анализа). При этом на О-т иггере 9 фиксируется тип ошибки. Как только в устройство поступает неискаженный бит, сигнал г)шибки с

5 второго входа блока 7 снимается и по этому перепаду на D-триггер заносится значение булевой функции сравнения qbvqb с выхода элемента НЕ 12. В том случае, когда корректировка необ0ходима, это значение равно единице и на первый вход элемента И 14 подается логическая единица. Если на вход регистра 1 вновь поступает ошибочный бит, на втором входе блока 7 вновь устанавливается еди5

гница, открывается элемент И 14 и взводится RS-триггер 11, с прямого выхода которого единица поступает на первый вход элемента И 15. По окончании Ьриема слова на четвертом входе блока 7 устанавливается потенциа л логического нуля, D-триггер 10 устанавливается в начальное состояние, а на в Jxoдe элемента И 15 появляется сигнал разрешения корректировки. По началу приема следующего слова на Ю четвертом входе блока 7 устанавливается единица и по положительному переПадУ RS-триггер 11 сбрасывается в

нуль. Если же в принимаемом слове больше не будет ошибок, RS-триггер 11 не взводится и выдача сигнала разрешения корректировки запрещается.

Таким образом, устройство исправляет одиночные пачки ошибок длиной t, (где п - дляна кодового сло-а ва) , кроме пачек ошибок длиной t(t, вектор ошибок.которых состоит из одних единиц.

Изобретени.е обеспечивает повышение достоверности принимаемой информации, достигаемое без существенного увеличения оборудования.

| название | год | авторы | номер документа |

|---|---|---|---|

| Декодирующее устройство линейного циклического кода | 1990 |

|

SU1718386A1 |

| СИСТЕМА ПЕРЕДАЧИ И ПРИЕМА ИНФОРМАЦИОННЫХ СООБЩЕНИЙ ПО РАДИОНАВИГАЦИОННОМУ КАНАЛУ ИМПУЛЬСНО-ФАЗОВОЙ РАДИОНАВИГАЦИОННОЙ СИСТЕМЫ | 1999 |

|

RU2158933C1 |

| Устройство для обнаружения и коррекции ошибок | 1986 |

|

SU1372367A1 |

| Регистр | 1980 |

|

SU987681A1 |

| Устройство для коррекции ошибок в информации | 1986 |

|

SU1372365A1 |

| СИСТЕМА ПЕРЕДАЧИ И ПРИЕМА ИНФОРМАЦИОННЫХ СООБЩЕНИЙ ПО РАДИОНАВИГАЦИОННОМУ КАНАЛУ ИМПУЛЬСНО-ФАЗОВОЙ РАДИОНАВИГАЦИОННОЙ СИСТЕМЫ | 2006 |

|

RU2318220C1 |

| УСТРОЙСТВО ОБНАРУЖЕНИЯ И ИСПРАВЛЕНИЯ ОШИБОК | 1996 |

|

RU2109405C1 |

| Устройство для обнаружения и коррекции ошибок | 1990 |

|

SU1783583A1 |

| Запоминающее устройство на цилиндрических магнитных доменах | 1990 |

|

SU1737510A1 |

| Запоминающее устройство с самоконтролем | 1984 |

|

SU1243032A1 |

УСТРОЙСТВО ДЛЯ ИСПРАВЛЕНИЯ ПАЧЕК ОШИБОК, содержащее входной регистр, информационный регистр, регистр ошибок, блок элементов И, блок обнаружения пачек ошибок и сумматор по: модулю два, причем вход вход него регистра является информацион- : ным входом устройства, информационный выход соединен с входом информационного регистра, выход которого соединен с информацинными входами блока обнаружения пачек ошибок и сумг матора по модулю два, выход .которого является выходом устройства,, а вход корректирующего кода соединен с выходом блока элементов И, первый ; вход которого соединен с выходом регистра ошибок, вход которого соединен с выходом разряда ошибки ,входтного регистра, выход разряда и ; , идентификатора, информации которого; соединен с разрешающим входом блока о

m-Ki-1 .

Kpr 2. .

„

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Темников Ф.Е | |||

| и др. | |||

| Теоретические основы информационной техники | |||

| М., Энергия, 1979, с.204-208 | |||

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Цифровая вычислительная техника и программирование | |||

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

| , Советское радио , 1968, с.124135 (прототип). | |||

Авторы

Даты

1983-09-23—Публикация

1982-01-05—Подача