микрокоманд, прямой выход первого счетного триггера соединен с вторыми входами первых и вторых элементов И-НЕ и ИЛИ и с третьим входом третьего элемента ИЛИ, инверсный выход первого счетного триггера соединен со своим информационным входом и синхровходом второго счетного триггера, инверсньй выход которого соединен со своим информационным входом, а прямой выход соединен с первым входом пятого элемента И-НЕ, первьш вход второго элемента И соединен с входом элемента НЕ, с входом второго синхроимпульС..1 млкропроцессора и с четвертым

входом блока формирования адреса, второй вход второго элемента И соединен с входом сброса первого счетного триггера и с инверсным выходом триггера прерываний, а выход второго элемента И соединен с входом сброса второго счетного триггера, вькод элемента НЕ соединен с вторыми входами с третьего по пятый элементов И-НЕ и первого элемента И , выход пятого элемента И -НЕ соединен с входом сброса триггера прерываний , вход установки которого соединен с входом прерьшаний микропроцессора.

| название | год | авторы | номер документа |

|---|---|---|---|

| Микропрограммное устройство управления | 1987 |

|

SU1522203A1 |

| Устройство для восстановления работы процессора | 1984 |

|

SU1191910A1 |

| Микропроцессор для управления памятью микрокоманд | 1979 |

|

SU793153A1 |

| Мультимикропрограммное устройство управления | 1985 |

|

SU1256025A1 |

| Устройство для сопряжения периферийных устройств с процессором и оперативной памятью | 1983 |

|

SU1156084A1 |

| Устройство для сопряжения ЭВМ с внешним абонентом | 1988 |

|

SU1594553A1 |

| Микропрограммное устройство управления | 1984 |

|

SU1264172A1 |

| Двухканальное устройство для контроля и восстановления процессорных систем | 1986 |

|

SU1397917A1 |

| Микропрограммное устройство для сопряжения процессора с абонентами | 1987 |

|

SU1539787A1 |

| Устройство для контроля и восстановления вычислительного процесса | 1988 |

|

SU1605233A1 |

МИКРОПРОЦЕССОР ДЛЯ УПРАВЛЕНИЯ ПАМЯТЬЮ ^ШKPOKOMAHД, содержащий регистр микрокоманд, блок формирова- 1ШЯ адреса, первьй регистр адреса микрокоманд, причем информационный вход регистра микрокоманд соединен с входом микрокоманд микропроцессора, а выход регистра микрокоманд соединен с первым входом блока формирования адреса, второй вход которого соединен с информационным входом микропроцессора, первый выход блока формирования адреса соединен с адресным входом первого регистра адреса микрокоманд, отличающий с я тем, что, с целью расширения функциональных возможностей микропроцессора за счет осуществления обработки прерьшаний на микропрограммном уровне и повышения его быстродействия, в него введены второй регистр адреса микрокоманд,коммутатор, управляющий триггер, элементы И, ИЛИ, НЕ, И-НЕ, два счетных триггера, триггер прерьшаний, причемвыходы первого и второго регистров адреса микрокоманд соединены соответственно с первым и вторым информационными входами коммутатора, выход которого соединен с выходом адреса микропроцессора и третьим входом бло,ка формирования адреса, первый выход которого соединен с адресным входом второго регистра адреса микрокоманд, прямой выход управляющего триггера соединен с первыми входаьш первых элементов И-НЕ и 1ШИ и первым управляющим входом коммутатора, ин- версньш выход управляющего триггера соединен со своим информационным входом и с первыми входами вторых элементов И-НЕ и ИЛИ и с вторым управляющим входом коммутатора, выходы первого и второго элементов И-НЕ соединены соответственно с входами установки первого и второго регистров адреса микрокоманд, выход второго элемента ИЛИ соединен с первым входом третьего элемепта И-НЕ, выход которого соединен с синхровхо- дом второго регистра адреса микрокоманд, выход первого элемента ИЛИ соединен с первым входом четвертого элемента И-НЕ, выход которого соединен с синхровходом первого регистра адреса микрокоманд, второй и третий выходы блока формирования адреса соединены с первым и вторым входами третьего элемента ИЛИ соответственно, выход которого соединен с первым входом первого элемента П, выход которого соединен с синхровходом управляющего триггера, синхровход первого счетного триггера соединен с входом первого синхроимпульса микропроцессора и с тактовым входом регистраёСОс 00оС/0*^>&

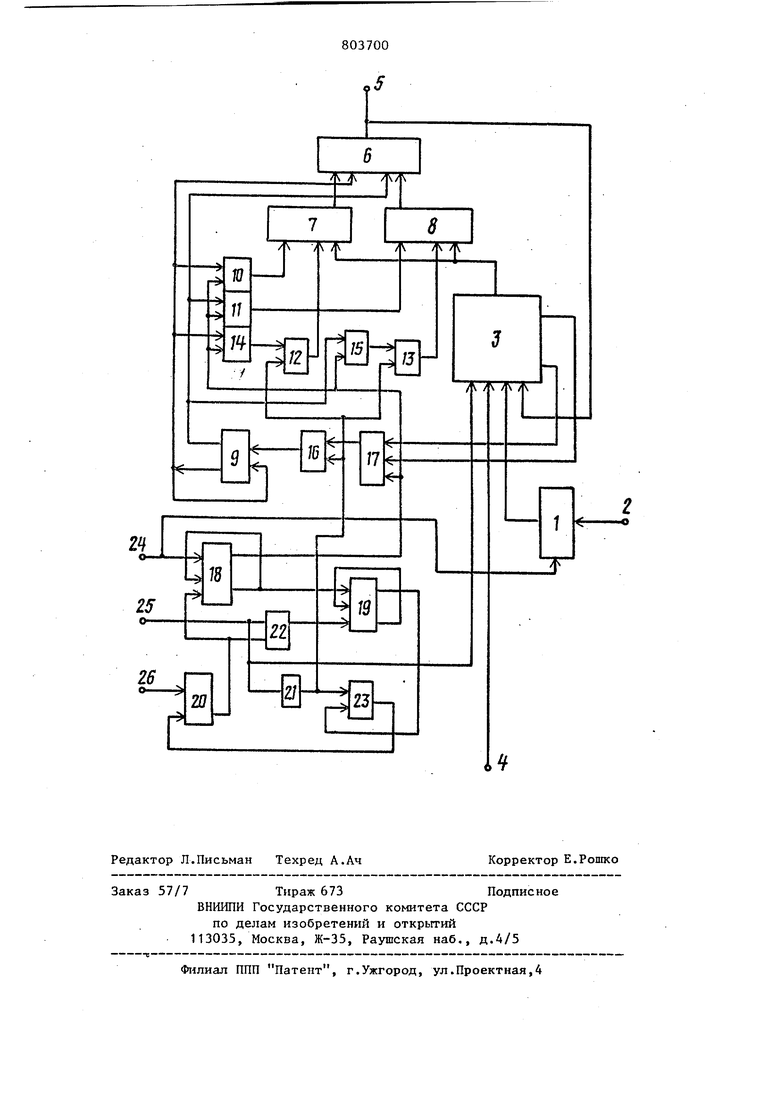

Изобретение относится к области цифровой вычислительной техники, а именно к проектированию цифровых вычислительных машин на основе больших интегральньк.схем (БИС) микропроцессоров. Известны микропроцессорные наборы БИС, отличительной чертой которых является наличие микропрограммного устройства управления, предназначенные для конструирования цифровых вычислительных машин. Обп(им недостатком БИС ЕМУ перечис ленных серий является невозможность организации обработки запросбв на прерывание на микропрограммном уровн Наиболее близким по технической сущности к изобретению является микропроцессор для управления памятью микрокоманд, Микропроцессор дпя управления памятью микрокоманд содержит: регистр микрокоманд, вход микрокоманд ШМК, блок формирования адреса, регистр адреса микрокоманд, вход адреса и вход синхронизации. К недостаткам известного микропроцессора относится невозможность организации прерывания на микропрограммном уровне,.отсутствие стека для хранения адреса прерванной микро команды, большое время ожидания на обработку прерывания (на программно уровне) и как следствие, низкое быс родействие по прерьшаниям. Цель изобретения - расширение функциональных возможностей микропроцессора за счет осуществления обработки прерываний на микропрограммном уровне и повьшгение его быстродействия. Цель достигается тем, что в микропроцессор для управления памятью микрокоманд введены: второй регистр адреса микрокоманд, коммутатор, управ ляющий триггер, два счетных триггера, триггеры прерываний, элементы И, ИЛИ, НЕ, И-НЕ, причем выходы первого и второго регистров адреса микрокоманд соединены соответственно с первым и вторым информационными входами коммутатора, выход мультиплексора соединенс выходом адреса микропроцессора и .третьим входом блока формирования адреса, первьй выход которого соединен с адресным входом второго регистра адреса микрокоманд; прямой выход управляющего триггера соединен с первыми входами первых элементов И-НЕ и ИЛИ и с первым управляющим входом коммутатора, инверсный выход управляющего триггера соединен со своим информационным входом и с первыми входами вторых элементов И-НЕ и ИЛИ и с вторым управляющим входом коммутатора, выходы первого и второго элементов И-НЕ соединены соответственно с входами установки первого и второго регистров адреса микрокоманд, выход второго элемента ИПИ соединен с пер вым входом третьего элемента П-НЕ, выход которого соединен с синхровходом второго регистр. адреса микрокоманд, выход первого элемента ИЛИ соединен с первым входом четвертого элемента И-НЕ, выход которого соединен с синхровходом первого регистра адреса микрокоманд, второй и третий выходы блока формирования адреса соединены с первым и вторым входами третьего элемента ИЛИ соответственно выход которого соединен с первым вхо дом первого элемента И, выход которо го соединен с синхровходом управляющего триггера, синхровход первого счетного триггера соединен с входом первого синхроимпульса микропроцессора и с тактовы - входом регистра микрокоманд, прямой выход первого счетного триггера соединен с вторым входом первых и вторых элементов И-НЕ и ИЛИ и с третьим входом третье го элемента ИЛИ, инверсиьй выход первого счетного триггера соединен с своим информационньм входом и с синхровходом второго счетного триггера, инверсный выход которого соединен с своим информационным входом, а прямой выход соединен с первым входом пятого элемента И-НЕ, первьй вход второго элемента И соединен с входом второго синхроимпульса микропроцессора, с входом элемента НЕ и с четвертым входом блока формирования адреса, второй вход второго элемента И соединен с инверсным выходом триггера прерываний и с входом сброса перво|Го счетного триггера, а выход втоjporo элемента И соединен с входом сброса второго счетного триггера, выход элемента НЕ соединен с вторыми входами с третьего но пятый элементов И-НЕ и первого элемента И, выход пятого элемента И-НЕ соеди11ен с входом сброса триггера прерываний, вход установки которого соединен с входом прерываний микропроцессора. Блок-схема микропроцессора для управления памятью микрокоманд приве

дена на чертеже.

Микропроцессор для управления памятью микрокоманд содержит регистр 1 микрокоманд, вход 2 микрокоманд,блок 3 формирования адреса, информационный вход 4, выход 5 адреса, коммутатор 6, два регистра 7 и 8 адреса микрокоманд, управляющий триггер 9, второй и первый элементы И-НЕ 10 и 11, третий и четвертый элементы И-НЕ 12 и

синхроимпульсу счетньп триггер 18 устанавливается в единицу. Этот высокий потенциал подается на элементы ИЛИ 17, 14 и 15, элементы И-НЕ 10,11 и разрешает прохождение синхроимпульсов с входа 25 через элемент НЕ 21, элементы И-НЕ 12 и 13 сразу к двум регистрам 7 и 8 адреса. По переднему фронту синхроимпульса, проходящего через элемент НЕ 21 и эле0413, второй и первьй элементы ИЛИ 14 и 15, первый элемент И 16, третий элемент ГШИ 17, два счетных триггера 18 и 19;триггер прерываютй 20, элемент НЕ 21,второй элемент И 22, пятьй элемент И-НЕ 23, вход 24 первого синхроимпульса, вход 25 второго синхроимпульса и вход 26 прерываний. Микропроцессор для управления .памятью микрокоманд работает следующим образом. В нормальном режиме работы (отсутствие запросов на прерывание) счетный триггер 18 находится в нулевом состоянии и синхроимпульсы с входа 25 проходят через элемент НЕ 21 и один из элементов И-НЕ 12 или 13 в соответствш с состоянием управляющего триггера 9. Допустим, управляющий триггер 9 находится в единичном состоянии, тогда сипхпоимпульсы проходят через элемент И-НЕ 13 на регистр адреса микрокоманд 8, коммутатор 6 подключит регистр адре микрокоманд к выходу адреса 5. Таким образом, текущий адрес с блока формирования адреса 3 подается на регистр адреса 8 и на выход адреса 5. В этом случае работа микропроцессора для управления памятью микрокоманд аналогична работе прототипа. Если управляющий триггер 9 находится в нулевом состоянии, то текущий адрес с блока 3 формирования адреса поступает на регистр 7 адреса и на вькод 5 адреса. Таким образом, управляющий триггер 9 осуществляет подключение регистров 7 и 8 адреса к коммутатору 6 и подачу синхроимпульсов с входа 25 к выбранному регистру. В режиме запроса на прерывание запрос поступает по входу 26 прерьта1шя на вход триггера 20 прерьшания и устанавливает его в ноль, при этом о счетного триггера 18 снимается сигнал установки и счетщда триггер 18 начинает считать синхроимпульсы, приходящие по входу 24. По первому мент И 16 управлякнцего триггера 9, происходит переключение управляющего триггера 9 в другое состояние. Допустим, управляющий триггер 9 находится в нулевом состоянии, т.е. в. работе находится регистр 7 адреса. При проходе синхроимпульса происходит переключение управляющего тригге ра 9 и к выходу 5 адреса подключается регистр 8 адреса, при этом элемен И-НЕ 11 вырабатывает сигнал установки регистра 8 адреса в единичное состояние и по заднему фронту синхроимпульса адрес с блока 3 формировани адреса записьшается в регистр 7 адре са, а регистр 8 адреса устанавливается в единичное состояние и этот адрес выдается на выход 5 адреса. Регистр 8 адреса устанавливается в единицу) не смотря на то, что на его информационные входы тоже подан теку щий адрес с блока 3 формирования адреса. Это происходит потому, что сиг нал установки перебивает информацию на входе. По второму синхроимпульсу с входа 24 счетный триггер 18 устанавливается в ноль и снимается единица элементов И-НЕ 10, 11 и элементов ИЛИ 14,15 и 17, тем самым открывая только один путь для прохождения синхроимпульсов с входа 25, а именно, к регистру 8 адреса. Единица с инверсного выхода счетного триггера 18 устанавливает счетный триггер 19 в единичное состояние, разрешая синхроимпульсам с входа 25 проходить через элемент И-НЕ 23. Передний фронт синхроимпуль са с входа 25, пройдя через элемент НЕ 21 и элемент И-НЕ 23, установит триггер 20 прерываний в единичное состояние. Единица с триггера 20 прерьшания будет удерживать счетньй триггер 18 в нулевом состоянии, так как подается на вход. По заднему фронту синхроимпульса с входа 25 элемента И 22 Счетный триггер 19 уста-, новится в нулевое состояние. При этом счетные триггеры 18,19 и триггер 20 прерьшаний установятся в исходное состояние. Таким образом происходит следующее . Если мы работали с регистром 7 адреса, то после всего происшедшего в регистре 7 адреса оказался следующий адрес, а с регистра 8 адреса вьщался на выход 5 адреса единичньй адрес. Значит мы спасли текущий адрес и перешли к начальной ячейке программы обработки прерывания. В режиме возврата к прерванной программе возврат происходит программно. При этом блок 3 формирования адреса вырабатьшает сигнал переключения управляющего триггера 9, который с выхода два или три блока 3 поступает на входы элемента ИЛИ 17 и на элемент И 16. По синхроимпульсу с входа 25 происходит переключение управляющего триггера 9 и к выходу 5 адреса подключается тот регистр адреса, которьй был отключен, в нашем случае это регистр 7 адреса. С регистра 7 адреса текущий адрес, на котором была прервана программа, поступает на выход 5 адреса и продолжается выполнение прерванной программы. Наличие второго регистра адреса, входа прерываний и схем управления регистрами адреса позволяет организовать прерывание на программном уровне без дополнительных затрат оборудования и времени. Кроме того, при этом не нужно спасать текущий адрес. Это позволяет значительно уменьшить объем программы обработки прерываний и соответственно объем ПЗУ микрокоманд, что выгодно отличает предлагаемый микропроцессор для управления памятью микрокоманд от известных устройств аналогичного назначения.

| Мнкропроцессорньй комплект БИС ТТЛ с диодами Шоттки | |||

| Прибор для переработки спирта в газовую смесь для двигателей внутреннего сгорания | 1920 |

|

SU589A1 |

| Справочные данные, 1977.Микропроцессор для управления памятью микрокоманд | |||

| Техническое описание | |||

| Ленинград, 1979. | |||

Авторы

Даты

1986-01-23—Публикация

1979-12-04—Подача