о

4

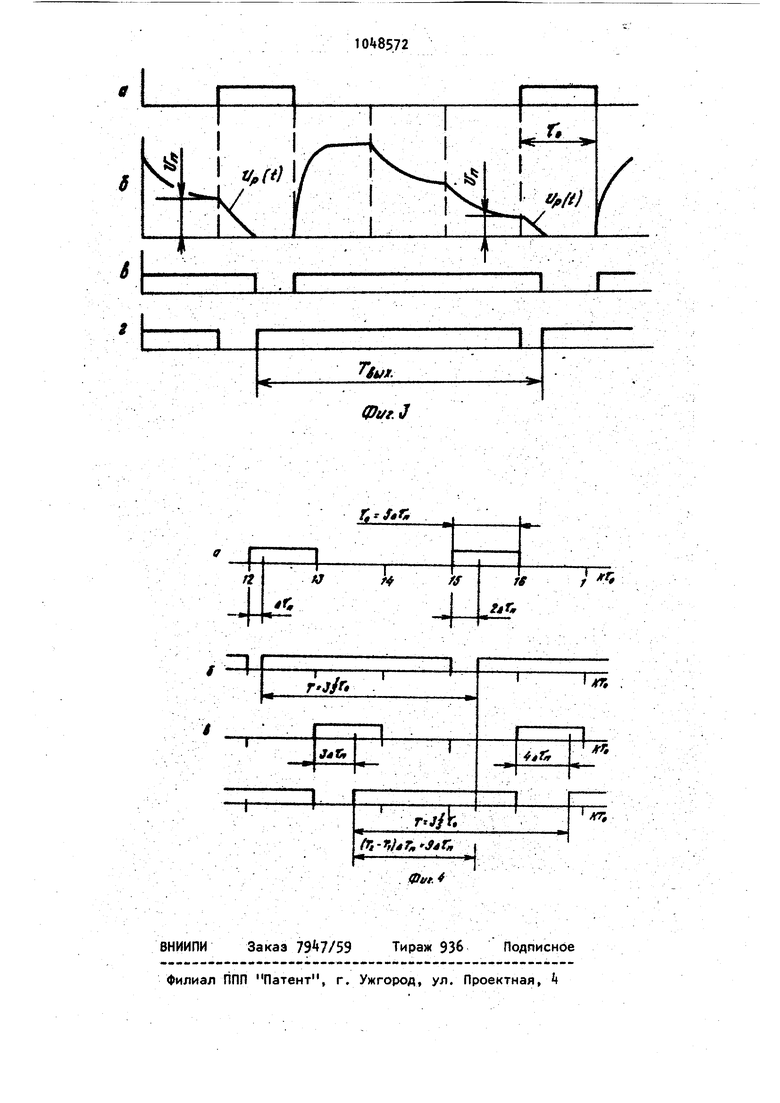

х Изобретение относится к вычислительной технике и автоматике и може быть использовано в устройствах, где необходимо линейное преобразование код-частота с повышенной точностью на малом временном интервале усреднения. Известен преобразователь код-час тота следования импульсов, содержащ регистры кода установки частоты и кода, определяющего временной интер вал преобразования, счетчики, блоки сравнения и считывания, управляющие триггеры и ключи l . Данный преобразователь позволяет получить.линейную зависимость между входным кодом и частотой следования выходных импульсов, но отличается сложностью и низкой точностью на интервалах усреднения, меньших инте вала преобразования устройства Известен также.преобразователь код-частота, содержащий первый сумматор, первый выход которого, подклю чен к первому входу мультиплексора, второй вход которого подключен к входной шине установки фазы, третий вход - к шине управления, а выход через регистр, тактируемый вход которого соединен с тактовой шиной подключен к первому входу первого сумматора, второй вход которого подключен к входной шине установки частоты 2J . Этот преобразователь характеризуется простотой схемного решения, однако также не позволяет получить высокую точность преобразования на интервале усреднения, меньшем интервала преобразования. Так за время одного цикла преобр зования tij to 2 7 , где LO - период следования тактовых импульсов, П разрядность преобразователя, на выходе преобразователя появится F импульсов, где F - число, устано ленное на шинах кода частоты, со средним периодом Г 1 / ер - р - «-о F В общем виде21 /Р выражается в виде неправильной дроби с целой и дробной частью, наличие которой приводит к возникновению ошибки. Так как фактический период следования выходных импулвсов каждый раз кратен l ( эффект временного квантования) ошибка преобразования выражается в появле- ; НИИ периодов выходного сигнала, равных количеству IQ, соответствующему целой части неправильной дроби, и увеличенному на t . Уменьшение такой ошибки может быть достигнуто путем уменьшения (,, приводящего к увеличению разрядности П преобразователя, а это, при ограниченном быстродействии элементов схемы, приводит к ограничению верхней частоты преобразования. Целью изобретения является повышение точности преобразования. Поставленная цель достигается тем, что в преобразователь код-частота, содержащий первый сумматор, первый выход которого соединен с первым входом мультиплексора, второй вход которого подключен к входной шине установки фазы, третий вход к шине управления, а выход - через регистр, тактируемый вход которого соединен с тактовой шиной, подключен - к первому входу первого сумматора, второй вход которого подключен к входной шине установки частоты, дополнительно введены.второй сумматор, широтно-импульсный преобразователь и блок инверторов, вход которого соединен с первым выходом первого сумматора, а выход- с первым входом второго сумматора, вторые входы которого подключены к соответствующим шинам установки логической единицы, а выход - к первому входу широтнр-импульсного преобразователя., второй, вход которого соединен со втор(йм выходом первого сумматора, третий вход - с входной шиной установки частоты, а выход с выходной шиной. На фиг. t представлена структурная электрическая схема преобразователя; на фиг. 2 - вариант схемы иротно-импульсного преобразователя; на фиг. 3 и - BpeMeHHbte диаграммы, поясняющие, соответственно, работу иротно-импульсного преобразоватея и формирование задержки выходных игналов на выходах двух аналогичных реобразователей. Преобразователь содержит сумматор 1, выходами подключенный к первым входам сумматора 2.через блок нверторов 3 и к первым BxojqaM мультиплёксора Ц, вторые входы которого подключены ко входной шине 5 установки фазы, а вход управления - к шине 6 управления преобразователя. Выход мультиплексора U подключен к первым входам сумматора V через регистр 7« тактируемый вход которого подключе к тактовой шине 8 преобразователя. Входная шина 9 установки частоты подключена ко вторым входам 10 сумматора 1 и ко входам 11 широтноимпульсного преобразователя ШИП) 12 а выход переноса старшего разряд сумматора 1 подключен ко входу 13 ШИП 12. Вторые входы сумматора 2 и вход переноса его первого разряда подключены к шине логической единицы а выходы - ко входам k ШИП 12. Преобразователь работает следующим образом. На шине 5 установлен нулевой код. На шине 6 управления установлен низкий потенциал, осуществляющий управление мультиплексором . При этом код установки фазы по шине 5 передается на входы регистра 7 и под действием тактовых импульсов на шине 8, следующих с частотой ig , переписывается на его выход. На входной шине 9 установлен код F, соответствующий выбранной частоте выходного сигнала. Так как величина f z, на выходе переноса сумматора 1 установлен нулевой потенциал и ШИП 12 закрыт. На выходах сумматора 2 установлено число . Этот этап соответствует подготовке преобразователя Начало преобразования совпадает с установлением высоко.гопотенциала на Шине управления 6 и соответственно на входе управления мультиплексор , переключающего выходы сумматора 1 на входы регистра 7. На выходах сумматора 1 формируется последовател ность чисел, увеличивающаяся на вели чину F по каждому тактовому импульсу действующему на входе В. По К-му импульсу состояние выходов сумматора 2, вычисляющего разность между величиной 2 и числом на выходе сумматора 1 , равно м 2 - (к + 1) ; Очевидно, что по (К + 1)-му импульсу наступает переполнение сумматора 1. На выходе переноса старшего разряда 13 устанавливается единица, с приходом которой в iijun 12 начинается формирование поправочного импульса, ,, -ч М, длительность которого с - (-о -р-. Как видно из формулы, число Р поазывает, на сколько частей надо аспределить период следования таковых импульсов 0 , чтобы получить дин временной поправочный квант о itf,- , а число М - какое количест о квантов 611 п необходимо для ормирования поправочного импульса, тобы обеспечивалось равенство BW Тер. (.фиг. З-г). Таким образом, первый период ожно записать ,IK,.«). + м. ь-гп де К. - количество целых периодов По следующему К + 2)-му тактовому мпульсу на выходах сумматора 1 устаовится число 2 F - М -i 2. На входе 13 ШИП 12 устанавливается нулевой отенциал и ШИП 12 закрывается. родолжается формирование числовой оследовательности, увеличивающейся а Р до появления следующего импульа переноса на выходе сумматора 1. Можно записать выражение периода ля общего случая M-i-Mi.4 где л - количество периодов о между двумя соседними импульсами переноса, М,.,- поправочный коэффициент для предыдущего (i-l)-ro импульса переноса; Mi - поправочный коэффициент -«-го импульса переноса, i 1,2,..... Через интервал преобразования tj, 2 дцикл возобновляется, так как схема переходит в исходное состояние. Один из возможных вариантов построения широтно- импульсного преобрази вателя кодов приведен на фиг. 2. Преобразователь содержит первый цифро-аналоговый преборазователь (ЦАП) 15, выходом подключенный к конденсатору 1б, через последовательно соединенные управляемый ключ 17 и генератор разрядного тока (ГРТ) 18, а входом к шинам 11, второй ЦАП 19, выходом подключенный к конденсатору б через управляемый ключ 20, элемент сравнения 21 по нулю, входом подключенный к конденсатору 16, а выходом к выходной шине через логич кий элемент И-НЕ 22, второй вход ко торого подключен ко входу управлени ключом 20 и входу 13 ШИП, выход элемента И-НЕ подключен ко входу управления ключа- 17. На вход 13 по ступают импульсы переполнения сумматора 1 (фиг. За). На входах 11 установлено число, разное Fi при этом на выходе перво ЦАП 15 действует напряжение Up. где Е модуль опорного напряжения на аналоговом входе первог ЦАП 15. На входах 1 установлено число М:, при этом напряжение на выходе , ;ЦАП 19ип ||-М(фиг. 38), где Е,,.напряжение на входе ЦАП 19. На входе 13 установлен нулевой потенциал, замыкающий ключ 20 и раз мыкащий ключ 17, так как на выходе элемента И-НЕ 22 в этом случае уста новлена логическая единица. Происхо дит &ястрый перезаряд конденсатора 16 (фиг. 36) ,малое внутреннее сопротивление ЦАП 19, до величины Uj, пропорциональной Mi, за время 0. Так как на входе элеменУа сравн ния 21 действует напряжение У| г О, то на его выходе установлена логиче кая единица Гфиг. 3 Ь) и логический элемент 22 открыт. В тот момент, когда на входе 13 ШИП устанавливается единица, что соответствует переполнению сумматора 1 (фиг. l), ключ 20 размыкается, а ключ 17 замыкается, так как на вы де элемента122, а, следовательно, на входе управления ключа 17 устанавлива ется нулевой потенциал. Включается ге нератор 18 и конденсатор 16 линейно разряжается через генератор в течен времени Сп причем ток разряда 1 ii± R -где коэффициент пропорциональности. Напряжение на конденсаторе 16 во время разряда может быть записано в следующем виде И /Л И 2.. E.-P-t Up(thUn--c--27M-j p-, С - емкость конденсатора где 1б, Разряд конденсатора 16 происходит ДО ир (t) 0.8 этот момент на выходе элемента сравнения 21 устанавливается нулевой уровень и на входе управления ключа 17 устанавливается логическая единица, ключ 17 - размыкается и разряд конденсатора 16 прекращается. При этом из формулы (1 время разряда равно EZ-M C-R .В момент снятия логической единицы со входа 13 процесс перезаряда и разряда возобновляется. На выходе логического элемента 22 формируются положительные импульсы, интервал между нарастающими фронтами которых ъьп 4 3)Если по выходу необходимо получить; импульсы формы меандр, то достаточно подключить триггер со счетным входом, срабатывание которого осуществлялось бы по нарастающему фронту импульсов с выхода ШИП 12.. Так как точность преобразования , на большом интервале усреднения определяется дискретной частью устройства, то возможная неточность фор-, мирования поправочного импульса в ШИП 12 не повлияет на эту характеристику, а точность на малом интервач ле усреднения будет существенно упучшена. Кроме формирования последовательности выходных импульсов с периодом равным Tgjj, j .р при одновременной работе двух преобразователей кодчастота возможна установка задержки двумя сигналами на их выходах, если на шинах 5 преоб{аазователей , будут установленычисла, соответствующие требуемой начальной фазе. П р им е р (для случая четырехразрядного преобразователя) . На шинах обоих.преобразователей установлено число Р 0101 ) шинах 5 первого преобразователя установлено число Т 0011 (Зю) шинах 5 второго преобразователя Tg 1100 () . Для сокращения записи описание работы преобразователей будем вести в десятичном исчислении. В этом случае в исходный момент времени на шине 6 действует нулевой потенциал и входные шины 5 подключены- ко вхо- i дам регистров 7« Под действием импульсов на шине 8 в регистрах 7 за писываются соответственно числа 3 и 12. В момент перехода состояния шины б из нулевого в единичное 0 85728 выходы мультиплексора k переключаются с выходов Ц на выходы сумматора 1 и состояние преобразователей изменяется согласно 5 таблице.

| название | год | авторы | номер документа |

|---|---|---|---|

| Преобразователь код-частота | 1981 |

|

SU966890A1 |

| Аналого-цифровой преобразователь | 1986 |

|

SU1325696A1 |

| Многоканальное устройство для измерения температуры | 1990 |

|

SU1791731A1 |

| КАЛИБРОВОЧНОЕ УСТРОЙСТВО ДЛЯ УЛЬТРАЗВУКОВОГО РАСХОДОМЕРА | 1995 |

|

RU2082951C1 |

| Цифроаналоговый преобразователь с автоматической коррекцией нелинейности | 1985 |

|

SU1302435A1 |

| Синтезатор частот | 1985 |

|

SU1262685A1 |

| Цифроаналоговый преобразователь с автоматической коррекцией нелинейности | 1988 |

|

SU1594699A1 |

| Параллельно-последовательный аналого-цифровой преобразователь | 1985 |

|

SU1305851A1 |

| Синтезатор частот | 1984 |

|

SU1293841A1 |

| ЦИФРОАНАЛОГОВЫЙ ПРЕОБРАЗОВАТЕЛЬ | 2012 |

|

RU2485681C1 |

8

О О 1 О О 1 О

3 8

ЛЗ 2

13 2

7

12

7 12

1

6

Т

6

11

о 1 о

11

О

5

о

10

о о 1 о о 1 о

5 10

15

it

15

4

9 14 9

I

3 8

3

Как видно из таблицы, полный ; цикл заканчивается через 2 импуль-: сов К, после чего опять устанавливается исходное состояние. В,течение одного цикла на выходе переноса старшего разряда единица устанавливается Р раз, причем периоД следова-,

1

1

12

15 10

6

1

О

4

6

11

О

i о

11

1

О

и

О

О

5

6

О

5

10

5 10

I

10

15 k

О

;

5

12

1

4 11 6

9 14

О 7 2 13 8 3 14

9 1i

О

3 8 13 2

1

3

О

8

О

13

1

2

7 2 1

О

9

i

13 8

о

7

15

12

1

ния импульсов за время такта прин(мает значения, отличающиеся на величину одного такта IQ .

55

В графах 5 и 9 таблицы подчерк:нуты те значения, которые формируют величины и М; поправочного импульса сh« Определим величину Т дпя произвольных значений, например К от 12 до 16 в первом преобраз aarehe. Как было отмемено выше длительность одного интервалам дол на быть разделена с шин на величи В нашем конкретном случа Таким образом, преобразователь по своему выходу перейдет в единичное состояние, когда в течение действия единицы переноса старшего разряда схема отсчитает одну величину ixniuw - U),a при К 15 - схема отсчитывает 2 величины &tn Таким образом, величина Т gbix для пер ,v вого преобразователя равна 3/фиг, а иБ , что соответствует вели чине tg. Аналогичная величина Т, и для второго преобразователя, так как . код F пру|ложен к обеим шинам 9 (фиг. kb и-г). Для определения задержки между вы ходами необходимо измерить интервал между фронтами нарастания сигналов с выходов преобразователей. Как видно из фиг. S и2 , задержка составляет 9bt п , что соответствует ; (2 П Таким образом, значение чисел, ycтaнaвливae « lX на шинах 5, определяет, на сколько интервалов utVi сигнал с установленной начальной фазой будет опережать сигнал, у которого Т О, а разност 2 Tfi, определяет их взаимную задержку (Сит - HOMeip преобразователей). Так как величина д If, , определяющая дискретность изменения задержки равнаiо/Т, то для установки задержки необходимо воспользоваться формулой 4 -Illljn tj- р toЕсли Tg Tj , то сигнал с Tj опережает сигнал с Т,„ и наоборот. i Разность (т g .- Tffli может меняться в пределах от -(2 - l) до (2 -1), 1(- 7 .% меняется от - -Таким образом, преобразователь осуществляет, линейное преобразование кода в частоту и преобразование это справедливо на любом интервале усреднения, так как обеспечивается 1 . «2 -5.. Одновреравенство То вых Р менно при включении в преобразователь мультиплексора Ц, осуществляющего предварительную установку числа Т в регистр 7 можно получить задержку сигнала тоже на любом интервале усреднения. Эти свойства позволяют существенно упростить дополнительные выходные, фильтрующие и усредняющйе устройства необходимые для создания синтезаторов частот с формой сигналов, близкой к синусоидальной, а также позволяют получить генератор импульсов с линейным управлением частот и с малой дисперсией периода следования. Ориентировочный экономический эффект при внедрении преобразователя может составить 5 тыс. руб, в год.

Фг/г.

10«8572

ше/f/a

фиг. 2

Авторы

Даты

1983-10-15—Публикация

1982-05-31—Подача