1

(21)4700610/24 (22) 05.06.89 (46)23.11.91. Бюл. №43

(71)Научно-производственное объединение Марс

(72)С.Л.Улыбин, А.И.Ляхов и В.Н.Ерастов (53)681.3(088.8)

(56)Авторское свидетельство СССР № 879564, кл. G 06 F 11/26, 1981.

Авторское свидетельство СССР №879563, кл. G 06 F 11/26, 1981. (54) УСТРОЙСТВО ДЛЯ ПРОВЕРКИ ПОЛНОТЫ ТЕСТИРОВАНИЯ ПРОГРАММ

(57)Изобретение относится к вычислительной технике. Цель изобретения - уменьшение аппаратных затрат. Устройство позволяет определить, прошла ли тестируемая программа по всем возможным маршрутам и использовала ли она все выделенные ей адреса. На вход 16 из адресного тракта процессора поступают адреса. На входы 17 - 24 из устройства управления процессора поступают признаки Адрес, Адрес команды, Команда условного перехода, Сброс, Запись, Чтение. Информация и Режим. Устройство с помощью регистра 4, элемента 5 задержки, блока 6 сравнения, триггеров 7 и 8, распределителя 9 импульсов, счетчика 10, элемента ИЛИ 11, элементов И 12 - 14, мультиплексора 15 анализирует приходящие адреса, признаки и фиксирует; в ячейках блока 1 памяти - факт использования программой выделенных ей адресов; в ячейках блока 2 памяти - факт отсутствия перехода по команде условного перехода; в ячейках блока 3 памяти - факт реализации перехода по команде условного перехода. 1 ил.

СО

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для подключения устройств ввода-вывода к многосегментной магистрали | 1987 |

|

SU1564638A2 |

| Устройство для отладки программ | 1983 |

|

SU1290334A1 |

| Автоматизированная система контроля радиоэлектронных устройств | 1989 |

|

SU1683038A1 |

| Устройство для отладки программ | 1983 |

|

SU1322290A2 |

| Устройство для обмена информацией | 1989 |

|

SU1702378A1 |

| Устройство для сбора статистических данных о работе программ ЭВМ | 1987 |

|

SU1471202A1 |

| Устройство для сопряжения каналов передачи данных с ЭВМ | 1985 |

|

SU1226476A1 |

| Микропрограммное устройство управления | 1986 |

|

SU1481759A1 |

| Устройство для отладки микроЭВМ | 1985 |

|

SU1410708A1 |

| Устройство для сопряжения ЭВМ с объектами управления | 1986 |

|

SU1401469A1 |

о

Ч)

со а о

XI

Изобретение относится к области вычислительной техники и может быть исполь- зовано в аппаратных и гибридных мониторах для проверки полноты тестирования программ,

Цель изобретения - уменьшение аппаратных затрат.

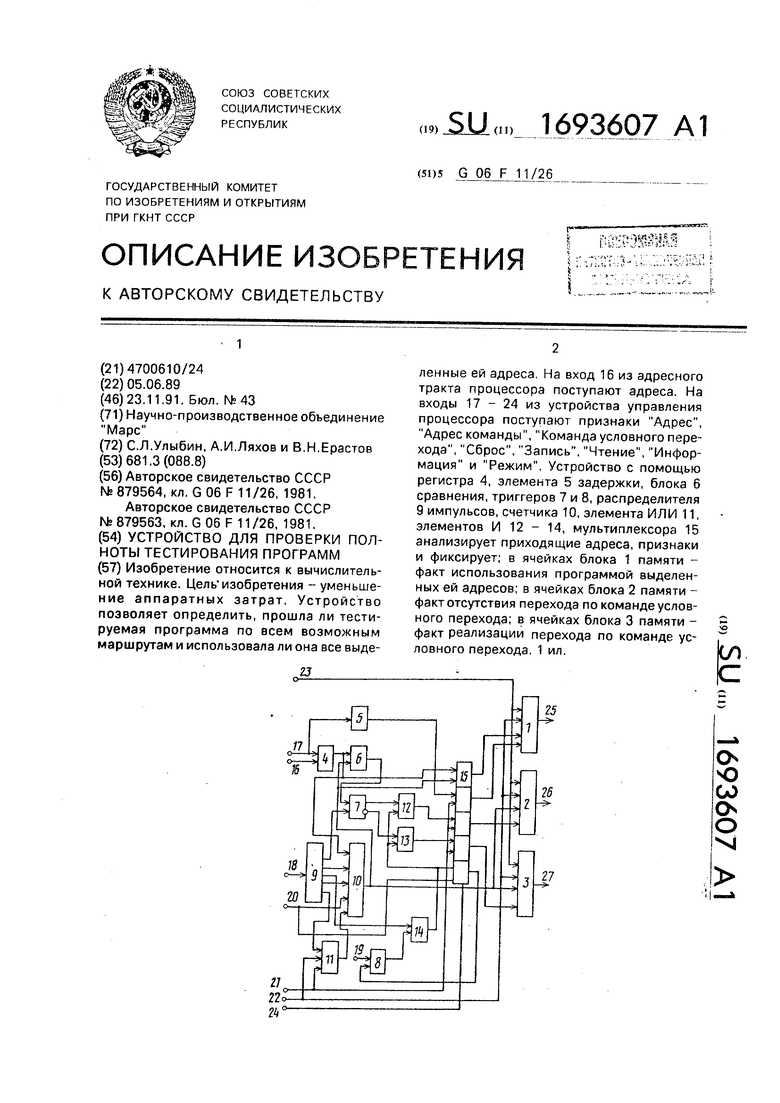

На чертеже представлена схема предлагаемого устройства.

Устройство содержит три блока 1 - 3 памяти, регистр 4, элемент 5 задержки, блок 6 сравнения, два триггера 7 и 8, распределитель 9 импульсов, счетчик 10, элемент ИЛИ 11, три элемента И 12-14, мультиплексор 15, входы адреса 16, признака Адрес 17, признака Адрес команды 18, признака Команда условного перехода 19, сброса 20, записи 21, чтения 22 устройства, информационный вход 23 устройства, вход 24 режима устройства, три информационных выхода 25 - 27 устройства.

Каждый из блоков 1 - 3 памяти имеет емкость 2k бит, где k - разрядность адресной константы процессора.

Блок 1 памяти предназначен для фиксации факта обращения по каждому адресу из адресного пространства процессора. Блок2 памяти предназначен для фиксации факта отсутствия перехода по команде условного перехода. Блок 3 памяти предназначен для фиксации факта реализации перехода по команде условного перехода.

Устройство может работать в трех режимах; Начальная установка, Работа, Вывод результатов.

В режиме Начальная установка устройство работает следующим образом.

На вход 24 режима устройства из ЭВМ (или с тумблера наборного поля) подается единичный потенциал. С входа режима 24 устройства единичный потенциал поступает на управляющий вход мультиплексора 15 и разрешает прохождение на его выходы сигналов с его первой группы входов.

На вход сброса 20 устройства из ЭВМ (или с кнопки наборного поля) подается сигнал, который далее проходит на вход сброса счетчика 10, обнуляя его, и на первый вход первой группы входов мультиплексора 15. На первом выходе мультиплексора 15 появляется сигнал, который поступает на вход сброса триггера 8. Задним фронтом этого сигнала триггер 8 сбрасывается в нулевое состояние.

. Нулевой адрес с выхода счетчика 10 поступает на адресные входы блоков 2 и 3 памяти и на второй вход первой группы входов мультиплексора 15. Этот адрес появляется на втором выходе мультиплексора 15 и

далее поступает на адресный вход блока 1 памяти.

Из ЭВМ (или с тумблера наборного поля) на информационный вход 23 устройства

подается нулевой потенциал, который далее поступает на информационный вход блоков 1-3 памяти.

Из ЭВМ (или с кнопки наборного поля) на вход записи 21 устройства подается сиг0 нал, который далее поступает на первый вход элемента ИЛИ 11 и на третий, четвертый, пятый входы первой группы входов мультиплексора 15, На третьем, четвертом и пятом выходах мультиплексора 15 появля5 ются сигналы, которые поступают на входы записи блоков 1-3 памяти. При этом происходит запись нулей в нулевую ячейку блоков 1 - 3 памяти, Кроме того, на выходе элемента ИЛИ 11 появляется сигнал, кото0 рый поступает на вход- 1 счетчика 10 и задним фронтом увеличивает его содержимое на 1.

Таким образом, в режиме Начальная установка обеспечивается формирование

5 на счетчике 10 адреса следующей ячейки блоков 1-3 памяти. Для обнуления всех ячеек блоков 1-3 памяти необходимо 2k раз подать сигнал на вход записи 21 устройства. После этого устройство готово к выполне0 нию режима Работа.

В режиме Работа устройство работает следующим образом.

На вход режима 24 устройства из ЭВМ (или с тумблера наборного поля) подается

5 нулевой потенциал, который далее поступает на управляющий вход мультиплексора 15 и разрешает прохождение на его выходы сигналов с его второй группы выходов. На информационный вход 23 устройства ЭВМ

0 (или с тумблера наборного поля) подается единичный потенциал. С входа 23 этот потенциал поступает на информационный вход блоков 1 - 3 памяти.

Адреса команд и данных выполняемых

5 программ поступают из ЭВМ через вход адреса 16 устройства на информационный вход регистра 4 и записываются в него сигналом из ЭВМ, проходящим на вход 17 признака Адрес устройства и далее на вход

0 записи регистра 4. С выхода регистра 4 адрес поступает на второй вход второй группы входов мультиплексора 15: С второго выхода мультиплексора 15 этот адрес поступает на адресный вход блока 1 памяти. Кроме

55 того, сигнал с входа 17 устройства поступает на элемент 5 задержки, который задерживает его на время, достаточное для записи информации в регистр 4. Сигнал с выхода элемента 5 задержки поступает на третий

вход второй группы входов мультиплексора

Таким образом, адресные константы, которые использованы в процессе выполнения программы, отмечены единицей в соответствующих ячейках блока 1 памяти.

Нулевая информация, сохранившаяся в ячейках блока 1 памяти по окончанию тестирования, покажет какие адресные константы не использованы программой. Если адрес, записываемый в регистр 4, является адресом команды, то на вход 18 признака адрес команды устройства из устройства управления ЭВМ приходит сигнал, поступающий далее на вход распределителя 9 импульсов. Последний имеет пять выходов, на которых последовательно вырабатывается единичный сигнал.

Сигнал с первого выхода распределителя импульсов поступает на вход записи триггера 7 и записывает на него информацию, поступающую на его информационный вход с выхода блока б сравнения.

На выходе блока 6 сравнения вырабатывается 1, если содержимое регистра 4, поступающее на его первый вход, совпадает с содержимым счетчика 10, поступающим на его второй вход. При этом регистр 4 хранит адрес текущей команды, а счетчик 10 - увеличенный на 1 адрес предыдущей команды, который формируется в предыдущем цикле работы распределителя 9 импульсов, Таким образом, на триггер 7 записывается 1, если выполняются команды с последовательными адресами.

Сигнал с второго выхода распределителя 9 импульсов поступает на вход -1 счетчика 10 и вычитает из его содержимого 1. Таким образом, на счетчике 10 формируется адрес предыдущей команды, который поступает с выхода счетчика 10 на адресные входы блоков 2 и 3 памяти.

Сигнал с третьего выхода распределителя 9 импульсов поступает на первый вход элемента И 14. При выполнении условного перехода в ЭВМ вырабатывается в момент дешифрации кода команд условного перехода сигнал, поступающий на вход 19 признака Команда условного перехода устройства. Сигнал с входа 19 устройства поступает на установочный вход триггера 8 и устанавливает на выходе триггера 8 единичный потенциал. Этот единичный потенциал поступает на второй вход элемента И 14 и разрешает прохождение сигнала с первого входа элемента И 14 на его выход.

Сигнал с выхода элемента И 14 поступает на вторые входы элементов И 12 и 13, первые входы которых соединены соответственно с прямым и инверсным выходами триггера 7. 5Если триггер 7 находится в единичном

состоянии, т.е. выполняются команды с последовательными адресами, то на выходе элемента И 12 появляется сигнал, который поступает на четвертый вход второй группы

0 входом мультиплексора 15. Этот сигнал появляется на четвертом выходе мультиплексора 15 и далее поступает на вход записи блока 2 памяти. При этом в ячейку блока 2

5 памяти, адресуемую адресом команды условного перехода, записывается единица. Таким образом, адреса команд условного перехода, по которым хоть один раз не осуществлен переход, отмечаются единицей в

0 соответствующих ячейках блока 2 памяти.

Если триггер 7 находится в нулевом состоянии, то на выходе элемента И 13 появляется сигнал, который поступает на пятый вход второй группы входов мультиплексора

5 15. На пятом выходе мультиплексора 15 появляется сигнал,который поступает на вход записи блока 3 памяти и записывает в его ячейку, адресуемую адресом команды условного перехода, единицу. Таким образом,

0 адреса команд условного перехода, по которым хоть один раз осуществлен переход, отмечаются единицей в соответствующих ячейках блока 3 памяти.

Кроме того, сигнал с выхода элемента И

5 14 поступает на первый вход второй группы входов мультиплексора 15. На первом выходе мультиплексора 15 появляется сигнал, который поступает на вход сброса триггера 8, сбрасывая его задним фронтом в нулевое

0 состояние.

Сигнал с четвертого выхода распределителя импульсов 9 поступает на вход записи счетчика 15 и записывает на него адрес

5 текущей команды, приходящий на его информационный вход с выхода регистра 4.

Сигнал с пятого выхода распределителя 9 импульсов поступает на второй вход элемента ИЛИ 11. На выходе элемента ИЛИ 11

0 появляется сигнал, который поступает на вход +1 счетчика 10 и задним фронтом увеличивает его содержимое на единицу. Таким образом, на выходе счетчика 10 формируется увеличенный на 1 адрес текущей

5 команды и счетчик 10 готовится к следующему циклу работы распределителя 9 импульсов. По окончанию тестирования прог-. раммы устройство переводится в режим Вывод результатов.

Устройство работает следующим образом.

На вход режима 24 устройства из ЭВМ (или с тумблера наборного поля) подается единичный потенциал. С входа 24 единичный потенциал поступает на управляющий вход мультиплексора 15 и разрешает прохождение на его выходы сигналов с его первой группы входов.

На вход сброса 20 устройства с ЭВМ (или с кнопки наборного поля) подается сигнал, который далее проходит на вход сброса счетчика 10, обнуляя ее. Нулевой адрес с выхода счетчика 10 поступает на адресные входы блоков 2 и 3 памяти и через мультиплексор 15 на адресный вход блока 1 памяти.

Из ЭВМ (или с кнопки наборного поля) на вход чтения 22 устройства подается сигнал, который далее поступает на третий вход элемента ИЛИ 11, и на входы чтения блоков 1-3 памяти. При этом на выходах 25 - 27 блоков 1 - 3 памяти появляется информация, считанная из нулевых ячеек блоков 1 - 3 памяти.

На выходе элемента ИЛИ 11 появляется сигнал, который поступает на вход +1 счетчика 10 и задним фронтом увеличивает его содержимое на 1, Таким образом обеспечивается формирование на счетчике 10 адреса следующей ячейки блоков 1-3 памяти. Для считывания всей информации, находящейся в ячейках блоков 1-3 памяти, необходимо 2k раз подать сигнал на вход 22 устройства.

Программу можно считать протестированной полностью, если в процессе выполнения программа использовала все выделенные для нее адреса и прошла по всем возможным маршрутам. В этом случае во всех ячейках блока 1 памяти, соответствующих выделенным программе адресам, должна быть единичная информация, а информация, сформированная в блоке 2 памяти должна совпадать с информацией, сформированной в блоке 3 памяти.

Таким образом, предлагаемое устройство позволяет определить полноту тестирования программ.

Формула изобретения Устройство для проверки полноты тестирования программ, содержащее регистр, счетчик, блок сравнения, элемент ИЛИ, два блока памяти и триггер, причем первый и второй входы блока сравнения соединены с выходами регистра и счетчика соответственно, отличающееся тем, что, с целью уменьшения аппаратных затрат, оно содержит третий блок памяти, второй триггер, три элемента И, элемент задержки, распределитель импульсов и мультиплексор, причем первый и второй входы первой группы информационных входов мультиплексора соединены соответственно с входом сброса

устройства и выходом счетчика, третий, четвертый и пятый входы первой группы информационных входов мультиплексора и первый вход элемента ИЛИ соединены с входом записи устройства, с первого по пятый входы второй группы информационных входов мультиплексора соединены соответственно с выходом первого элемента И, выходом регистра, выходом элемента задержки, выходом второго элемента И и выходом

третьего элемента И, с первого по пятый выходы мультиплексора, соединены соответственно с входом сброса первого триггера, адресным входом первого блока памяти и входами записи первого, второго и третьего блоков памяти, выходы которых являются информационными выходами устройства с первого по третий, вход распределителя импульсов является входом признака Адрес команды устройства, а с первого по

пятый выходы распределителя импульсов соединены соответственно с входом синхронизации второго триггера, вычитающим входом счетчика, первым входом первого элемента И, входом записи счетчика и вторым входом элемента ИЛИ, третий вход которого и входы считывания первого, второго и третьего блоков памяти соединены с входом чтения устройства, информационный вход устройства соединен с информационными входами первого, второго и третьего блоков памяти, выход элемента ИЛИ соединен с суммирующим входом счетчика, выход которого соединен с адресными входами второго и третьего блоков памяти,

информационный вход счетчика соединен с выходом регистра, информационный вход которого является входом адреса устройства, а вход записи и вход элемента задержки соединены с входом признака Адрес устройства, выход блока сравнения соединен с информационным входом второго триггера, прямой и инверсный выходы которого соединены с первыми входами второго и третьего элементов И соответственно, вторые

0 входы которых соединены с выходом первого элемента И, второй вход которого соединен с выходом первого триггера, единичный вход которого является входом признака Команда условного перехода устройства,

5 вход сброса счетчика соединен с входом сброса устройства, управляющий вход мультиплексора является входом режима устройства.

Авторы

Даты

1991-11-23—Публикация

1989-06-05—Подача